Testing system and method for DCM of FPGA

A test system and test method technology, applied in the direction of digital circuit test, electronic circuit test, measurement of electricity, etc., can solve the problems of high cost, high test platform cost, low efficiency, etc., to reduce operation time, reduce manual setting, The effect of testing the simplicity of the system

Pending Publication Date: 2020-06-19

NORTH CHINA UNIV OF WATER RESOURCES & ELECTRIC POWER

View PDF6 Cites 1 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

At present, the commonly used test is to use a professional automatic tester ATE for testing, but the automatic tester is expensive and expensive, and the ATE test is mainly for the functional test of the chip. For the test of some performance parameters of the DCM, the ATE test index Can't meet testing requirements

If you build a circuit board and connect separate oscilloscopes, spectrum analyzers, signal source equipment, and digital control power supply equipment, you can perform full-coverage testing on the performance of the DCM of the FPGA chip, and the indicators can also meet the testing requirements. However, using multiple separate testing instruments, It will lead to complex construction of the entire test system and high cost of building a test platform. In addition, when using separate test instruments for testing, it is necessary to operate different test instruments and repeatedly set test parameters, which makes the test time too long and low in efficiency.

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

test Embodiment to F

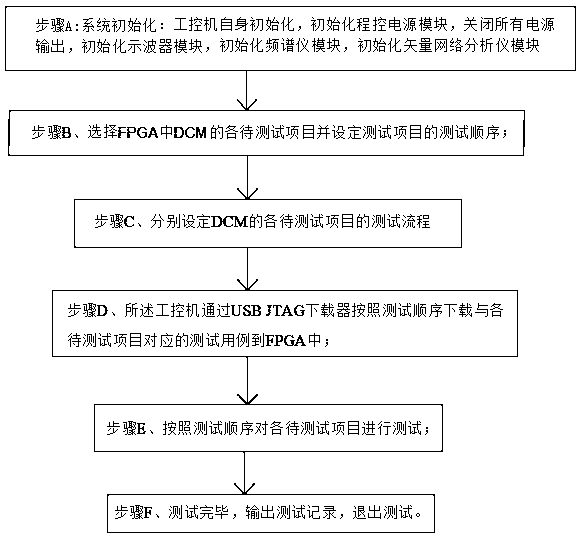

[0059] One end of the USB JTAG downloader is connected with the JTAG download interface, and the other end is connected with the USB interface of the industrial computer, and the industrial computer downloads the test case in the FPGA by the USB JTAG downloader;

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

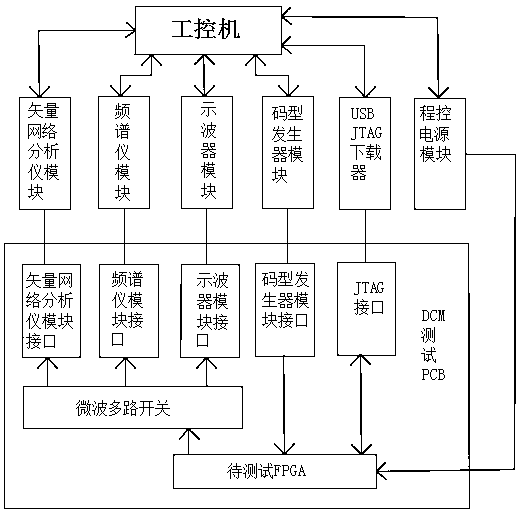

The invention provides a testing system and method for a DCM of an FPGA. The method is used for carrying out full-coverage testing on functions and performance of a DCM of an FPGA. A code pattern generator module, a test instrument module, a vector network analyzer module and a programmable power supply module are integrated in a PXI industrial personal computer; a DCM is adopted to test a PCB; the PXI industrial personal computer and the DCM test PCB are connected together through a USB JTAG downloader to form a test system. The testing system is simpler, and the USB JTAG downloader is controlled by the PXI industrial personal computer to download each test case. Each test item is selected on the PXI industrial personal computer and test parameters of each test item are preset; in a testprocess, an output signal of a DCM output pin of the FPGA is input to an oscilloscope module, a frequency spectrograph module and the vector network analyzer module through a switch matrix module according to preset content; therefore, full-coverage testing of the function and the performance of the DCM of the FPGA is achieved, manual setting is reduced, the operation time is shortened, and the testing efficiency of the DCM module of the FPGA is greatly improved.

Description

technical field [0001] The invention relates to the field of integrated circuit testing, in particular to an FPGA DCM testing system and testing method. Background technique [0002] The DCM of the FPGA is the digital clock management unit (Digital Clock Manager), which is an important part of the FPGA. It can achieve zero clock skew, eliminate clock distribution delays, and realize clock closed-loop control. It can also be mapped to the PCB for synchronizing external chips. , Integrate the clock control inside and outside the chip to reduce the requirements for external chips and facilitate the design of the system. [0003] DCM testing of FPGA chips is a very important link in chip design and production. DCM is a digital-analog hybrid circuit. Therefore, DCM testing of FPGAs is very different from other resource testing inside FPGAs. Not only functional testing, but also performance testing is required. The function test of DCM includes: clock frequency multiplication, fr...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G01R31/317G01R31/3183

CPCG01R31/31712G01R31/31725G01R31/31726G01R31/31727G01R31/318314

Inventor 段美霞段爱霞段艳玲江勇杨媚黄永志姚淑霞白娟杜爱国

Owner NORTH CHINA UNIV OF WATER RESOURCES & ELECTRIC POWER