Security coprocessor structure based on RISC-V instruction extension

A technology of RISC-V and instruction expansion, which is applied in the direction of concurrent instruction execution, electronic digital data processing, computer security devices, etc., and can solve problems such as poor universality and universality, existence of authorization and universality, and efficiency that cannot meet expectations. , to achieve the effect of reducing intrusion, avoiding instruction set authorization problems, and less intrusiveness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In the description of the present invention, it should be noted that the terms "installation", "connected" and "connected" should be understood in a broad sense, unless otherwise clearly specified and limited. For example, they can be fixed or detachable. Connected or integrally connected; it can be a mechanical connection or an electrical connection; it can be directly connected or indirectly connected through an intermediate medium, and it can be the internal communication between two components. For those of ordinary skill in the art, the specific meanings of the above-mentioned terms in the present invention can be understood in specific situations.

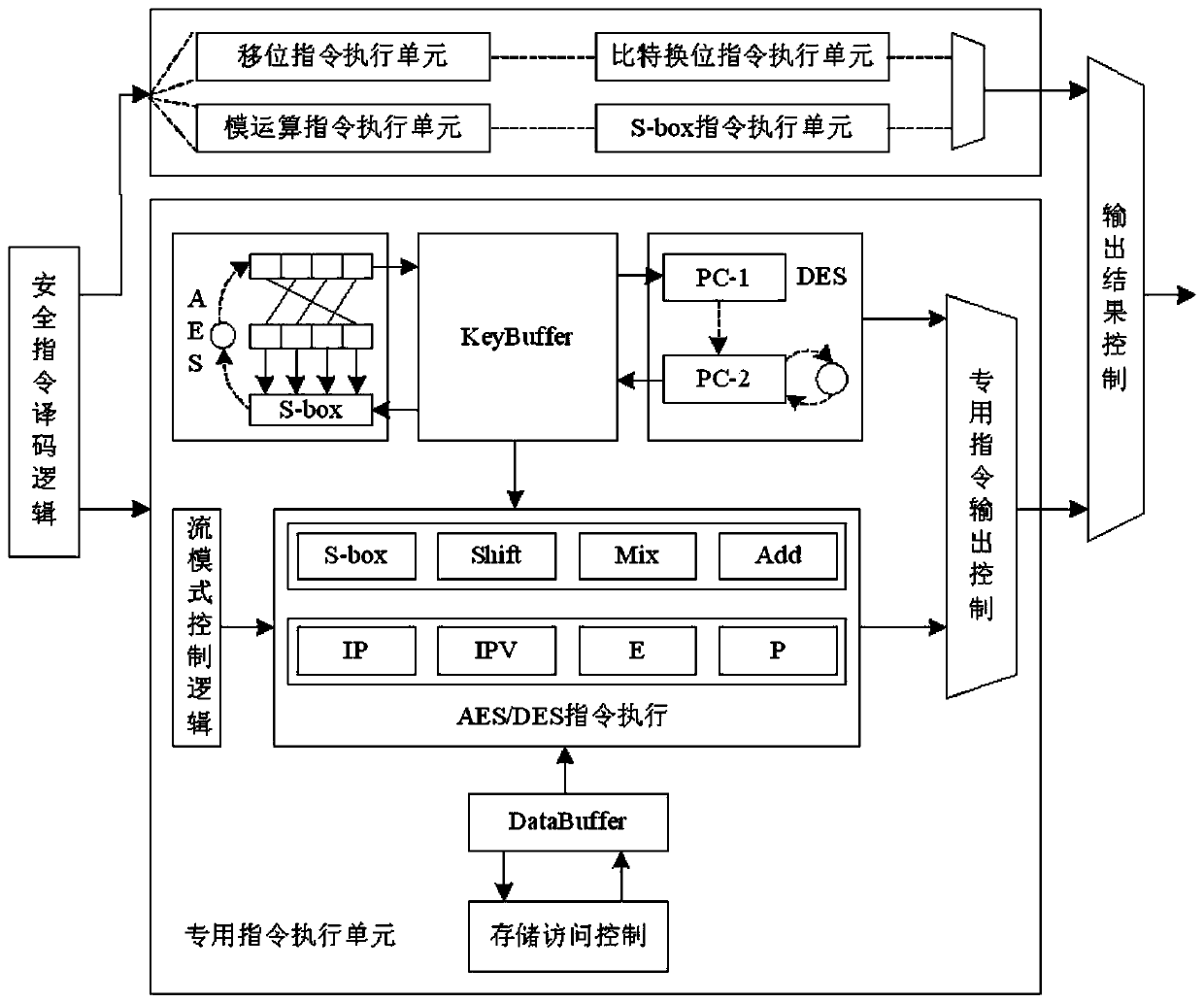

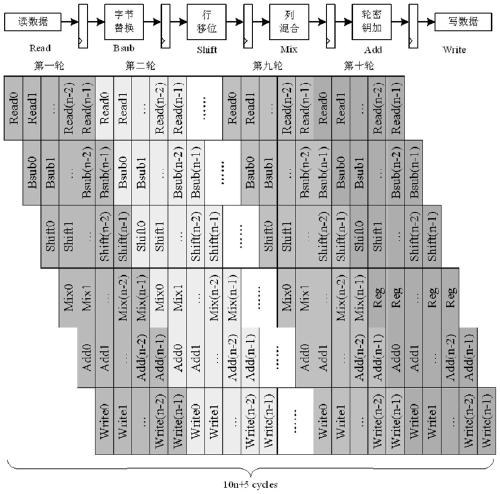

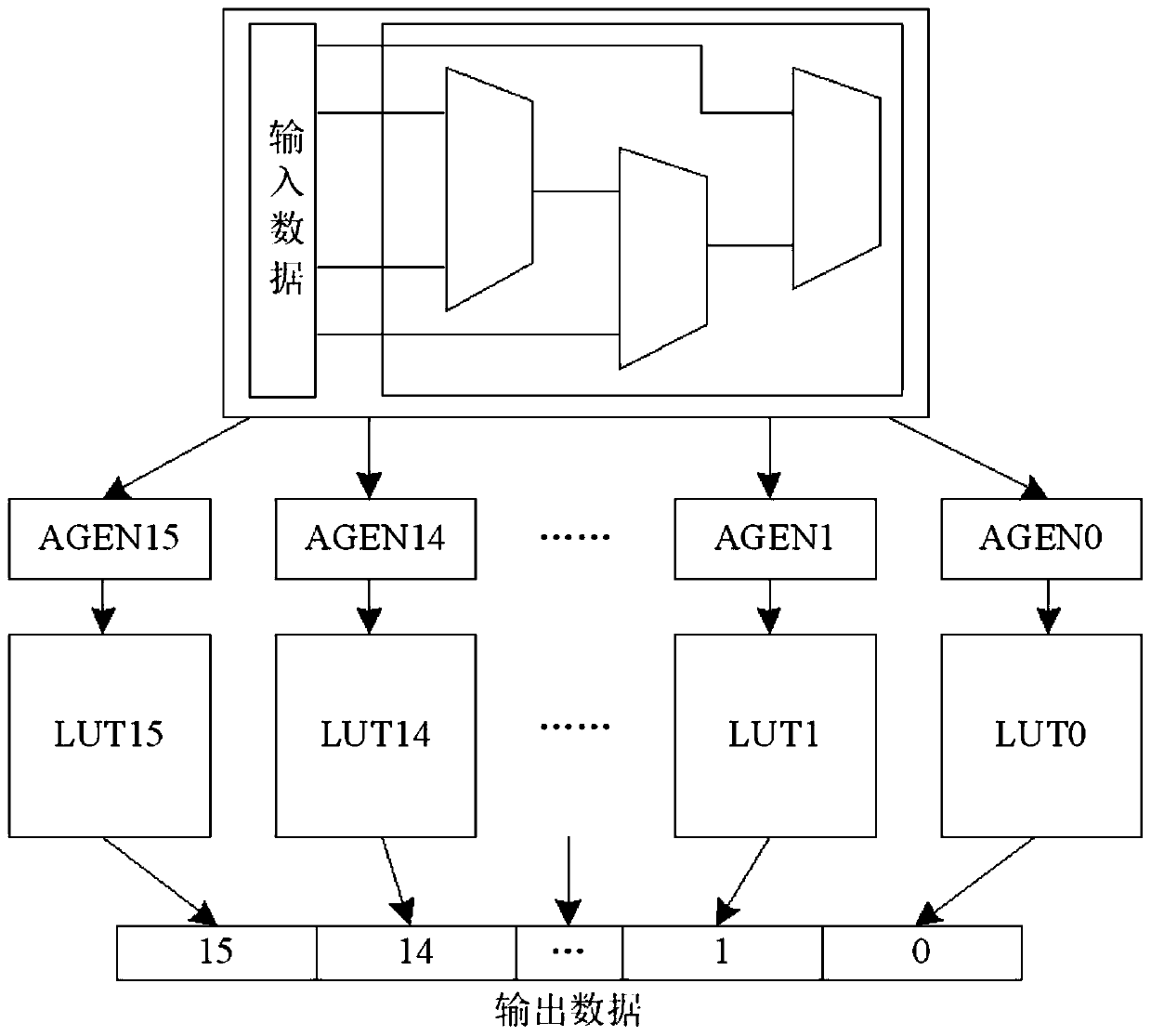

[0047] The present invention provides a security coprocessor structure based on RISC-V instruction extension, adopts the user scalability provided by the current open source instruction set RISC-V, and summarizes and extracts mainstream multiple symmetric group encryption and decryption algorithms. Construct a security co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More