Power device embedded substrate packaging structure and preparation method

A power device and packaging structure technology, applied in the field of power device embedded substrate packaging structure and preparation, can solve the problems of undrilled holes, floating pads, Al melting of pads, etc., to improve processing yield, Effect of Reliability Improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

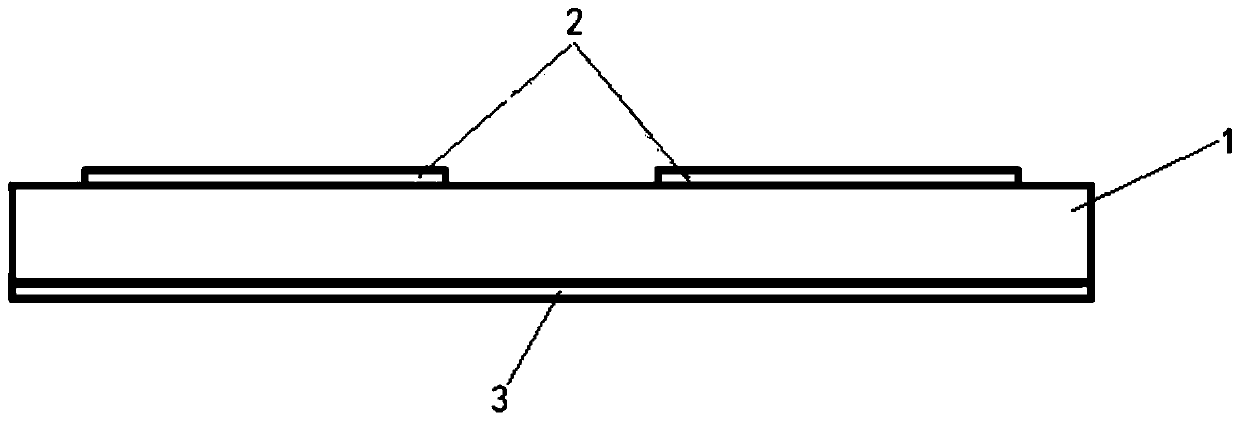

[0051] A method for preparing a power device embedded substrate packaging structure, comprising the following steps:

[0052] Step 1: Preparation of Power Semiconductor Die

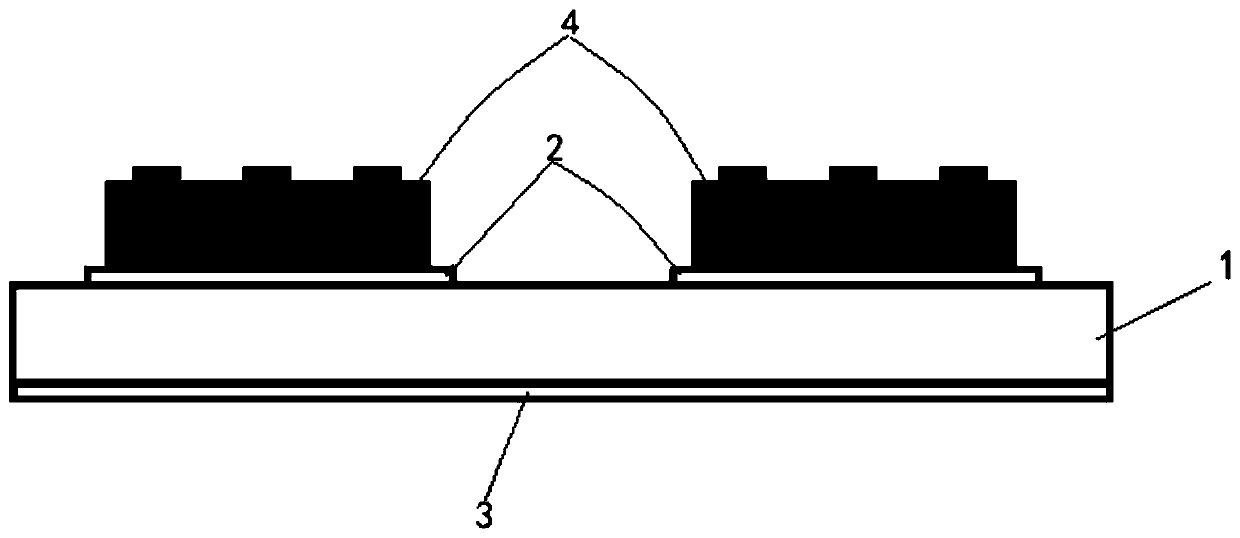

[0053] 1.1 see Figure 5 , the upper surface of the silicon layer 110 is covered with a dielectric layer 130, a passivation layer 140, and a bonding pad Al layer 111, a part of the bonding pad Al layer 111 is directly connected to the silicon layer 110, and another part of the bonding pad Al layer 111 A dielectric layer 130 is provided between a part and the silicon layer 110, and the adjacent pad Al layers 111 are separated by a passivation layer 140;

[0054] 1.2 see Image 6 , make conductive column 112 on each pressure pad Al layer 111 to form the upper electrode 110 of the power semiconductor die; conductive column 112 can be nickel column, copper column or gold column or other metal materials, nickel column can adopt electroless plating The metal nickel is formed, the copper pillar can be formed ...

Embodiment 2

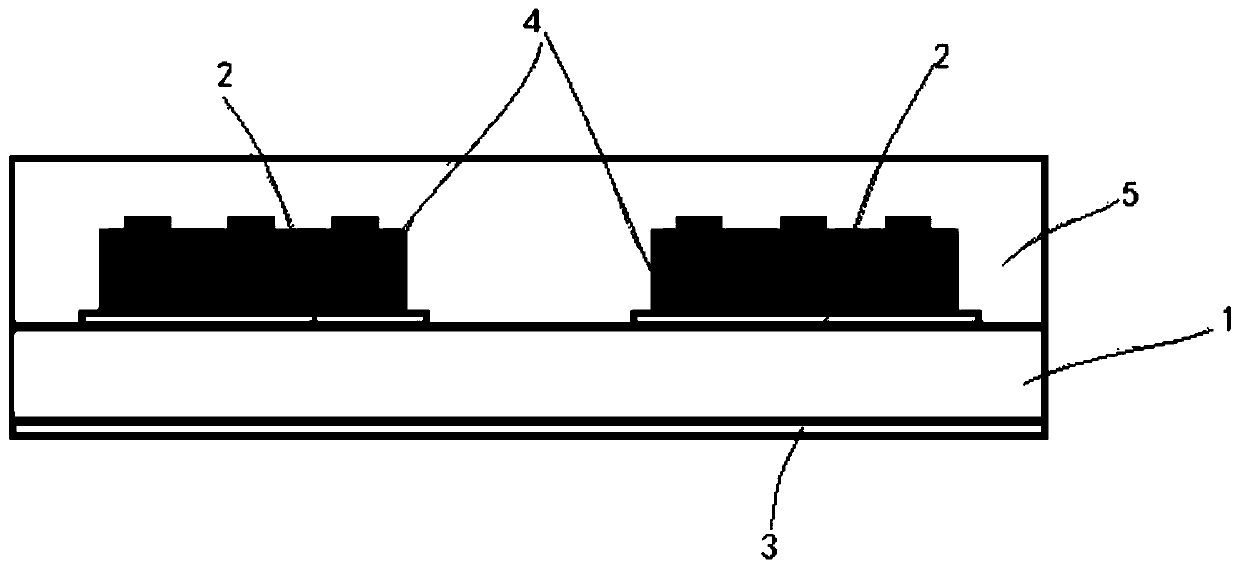

[0066] Steps 1 and 2 of the method for preparing a power device embedded substrate packaging structure in this embodiment are the same as those in Embodiment 1, except that Step 3.2 and Step 3.3 in Step 3 are different, see Figure 14 , Step 3 of this embodiment is replaced by the following steps 3.2a and 3.3a:

[0067] 3.2a Use flow glue 300 to fill each power semiconductor die A and cover each power semiconductor die A for dielectric lamination, then directly grind the upper surface of flow glue 300, and place the upper electrode in each power semiconductor die A The upper surface of the conductive pillar 112 of 110 exposes the upper surface of the flow glue 300 to form a laminated substrate embedded with power semiconductor dies;

[0068] 3.3a Use a laser to punch some blind holes 320 and some through holes 330 on the substrate embedded with the power semiconductor die after lamination, and the blind holes 320 expose the lower electrode 120 of the power semiconductor die ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More