High-voltage bootstrap diode composite device structure

A composite device, high-voltage bootstrapping technology, applied in diodes, semiconductor devices, electro-solid devices, etc., can solve the problems of device size and increase in manufacturing cost, and achieve the effects of reducing power consumption, saving chip space, and reducing leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

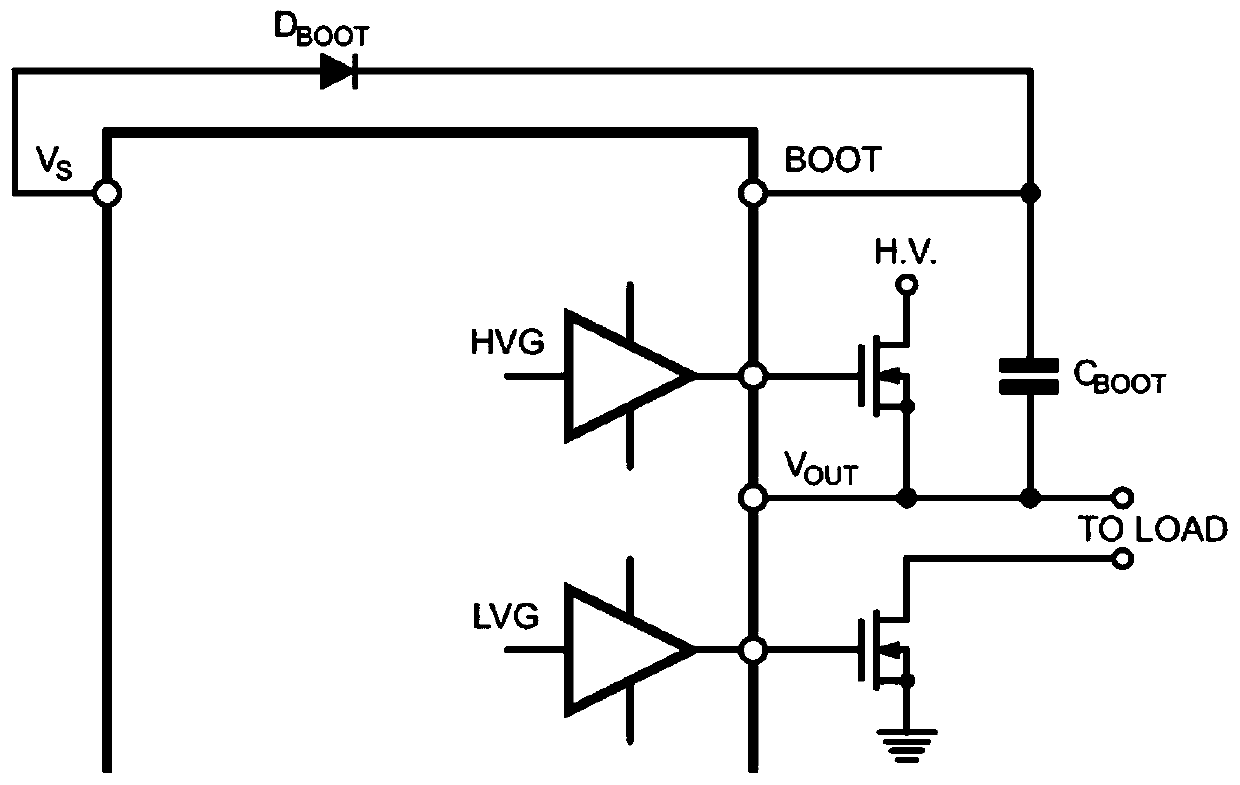

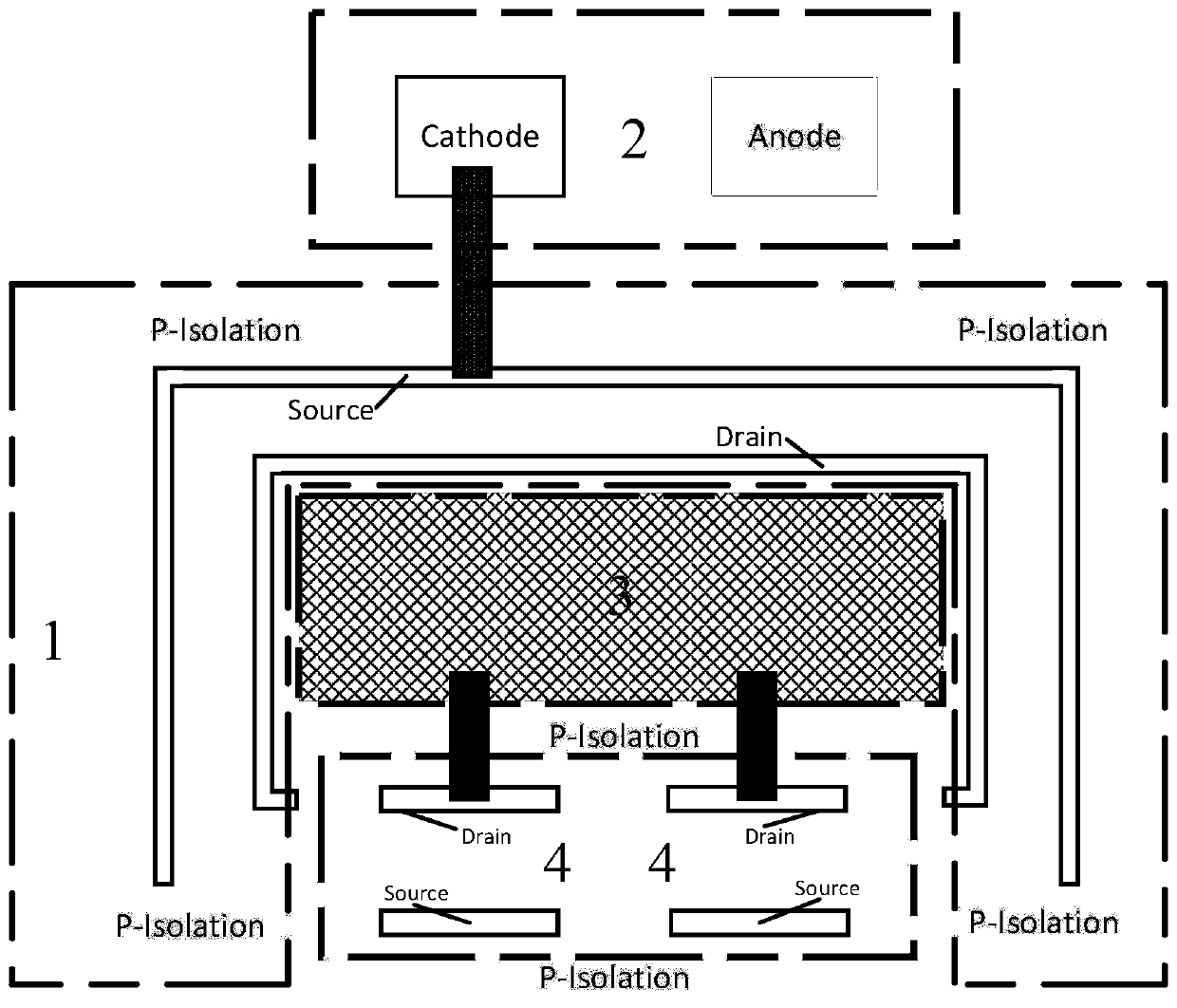

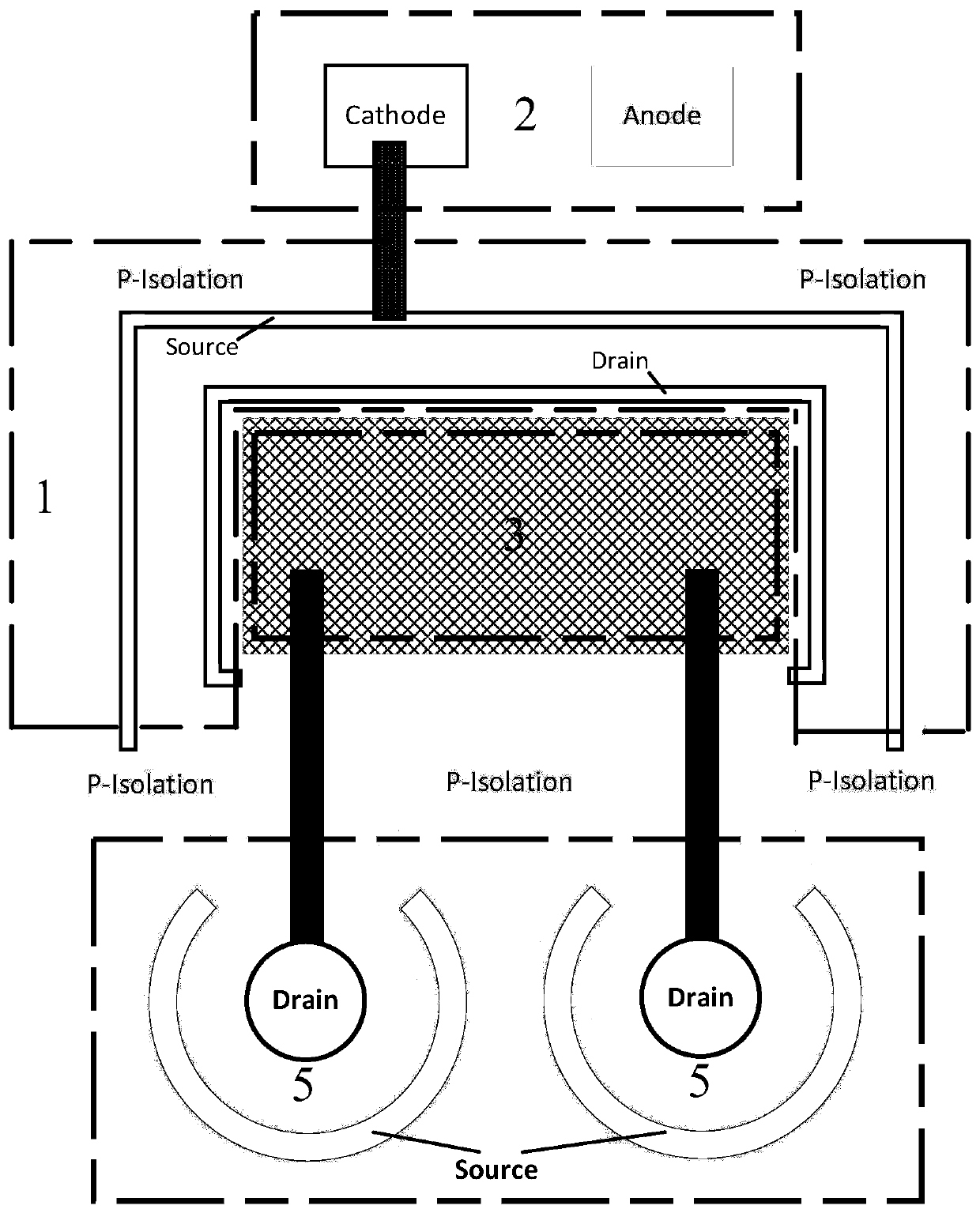

[0024] This embodiment provides a high-voltage bootstrap diode composite device structure, the composite device includes a high-voltage JFET and a diode device, and the source of the high-voltage JFET is connected to the cathode of the diode through metal, thereby forming a composite device that can replace a traditional high-voltage bootstrap diode.

[0025] In terms of layout, the high-voltage JFET device 1 is surrounded by P-type isolation P-Isolation, so that the JFET forms a ring-like structure. At the same time, in order to facilitate the connection with the diode, the JFET outer ring side is the JFET source region Source, and the inner ring side is the JFET drain region Drain. Diode 2 is also surrounded by P-type isolation, and the cathode Cathode is connected to the source of JFET1 through metal to form a composite device, which can be combined with two Divided RESURF structures or Self Shielded structure LDMOS4 for level shifting to form a high-side circuit ring island...

Embodiment 2

[0032] Such as Figure 5 As shown, the difference between this embodiment and Embodiment 1 is that the high-voltage JFET device 1 is formed by the second P-type buried layer 112, the second P-type implantation P-TYPE111, and the second P-type well region P-WELL110 In the through isolation structure, the second P-type implanted P-TYPE 111 part extends in the X direction to align with the end of the second P-type buried layer 112 to adjust the pinch-off voltage of the JFET.

Embodiment 3

[0034] Such as Figure 6 As shown, the difference between this embodiment and Embodiment 1 is that the high-voltage JFET device 1 is formed by the second P-type buried layer 112, the second P-type implantation P-TYPE111, and the second P-type well region P-WELL110 In the via isolation structure, the length of the second P-type buried layer 112 in the X direction is consistent with that of the second P-type well region P-WELL 110 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More