Multi-PLL parallel output clock synchronization system and working method thereof

A technology for outputting clocks and working methods, applied in the direction of electrical components, automatic control of power, etc., can solve the problem of asynchronous multi-PLL parallel output clocks and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

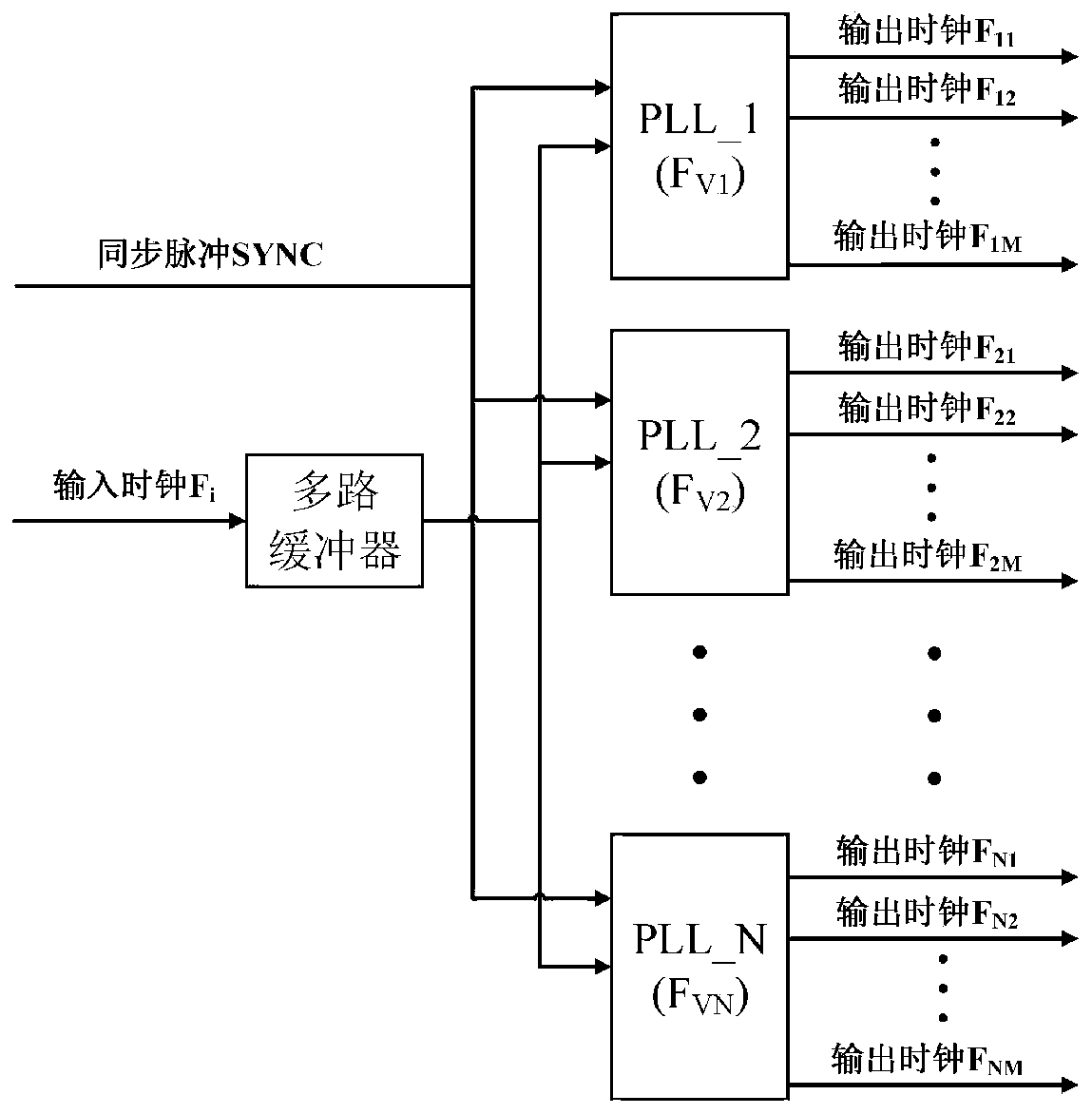

Problems solved by technology

Method used

Image

Examples

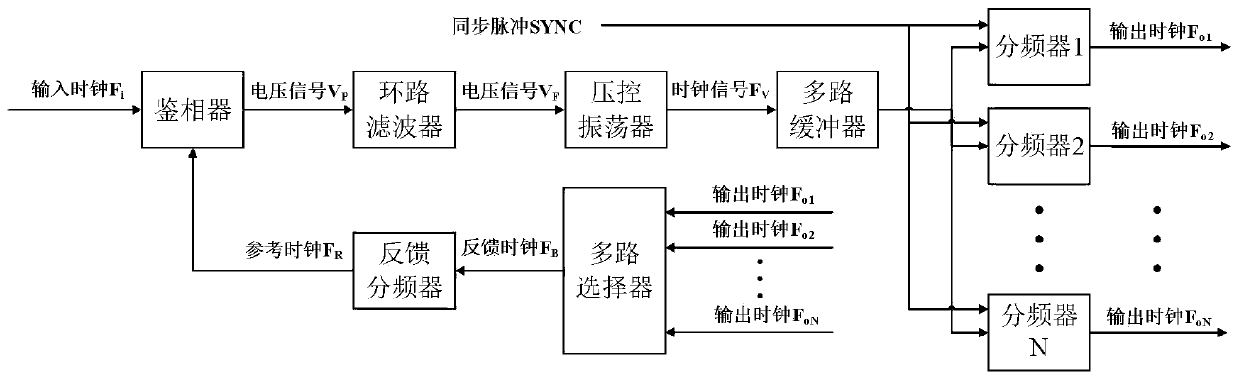

Embodiment 1

[0030] phase detector on the input clock F i with reference clock F R The frequency of the phase detector is compared with the phase, when both are the same, the voltage signal V output by the phase detector P will be stable; the function of the loop filter is to obtain a voltage signal V with a higher signal-to-noise ratio F ; The core clock F of the voltage-controlled oscillator output PLL work V , its frequency is generally above GHz, and the specific output frequency is determined by the voltage signal V F Control; F V After passing through the multi-channel buffer, and then passing through N frequency dividers respectively, N output clocks are obtained; the multiplexer selects one of the N output clocks as the feedback clock F B , after passing through the feedback frequency divider to get the reference clock F R Send it back to the phase detector, so that the entire PLL forms a complete negative feedback structure.

[0031] The synchronization pulse SYNC is also us...

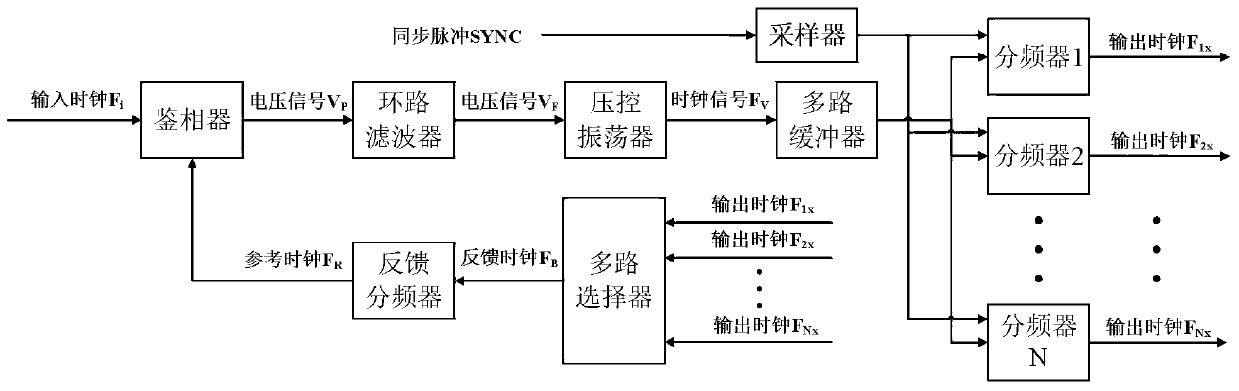

Embodiment 2

[0053] Such as Figure 4 As shown, for off-the-shelf PLL chips, it provides image 3 in the manner required by the sampler circuit. Figure 4 The specific implementation structure of the digital circuit is given, which is composed of a clock multiplexer and a sampling flip-flop. This structure is added to the ready-made PLL chip, and it can be re-made.

Embodiment 3

[0055] For programmable logic devices such as FPGA, while synchronous PLL is integrated inside, it can be programmed on-site by using hardware description language to realize image 3 The sampler circuit shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More