High-erasing-speed semi-floating-gate memory and preparation method thereof

A technology of erasing and writing speed and semi-floating gate, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc. The effect of small contact resistance and increased gate capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be further introduced below in conjunction with the embodiments and accompanying drawings. It should be understood that the examples are only used to explain the present invention, not to limit the present invention. All other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

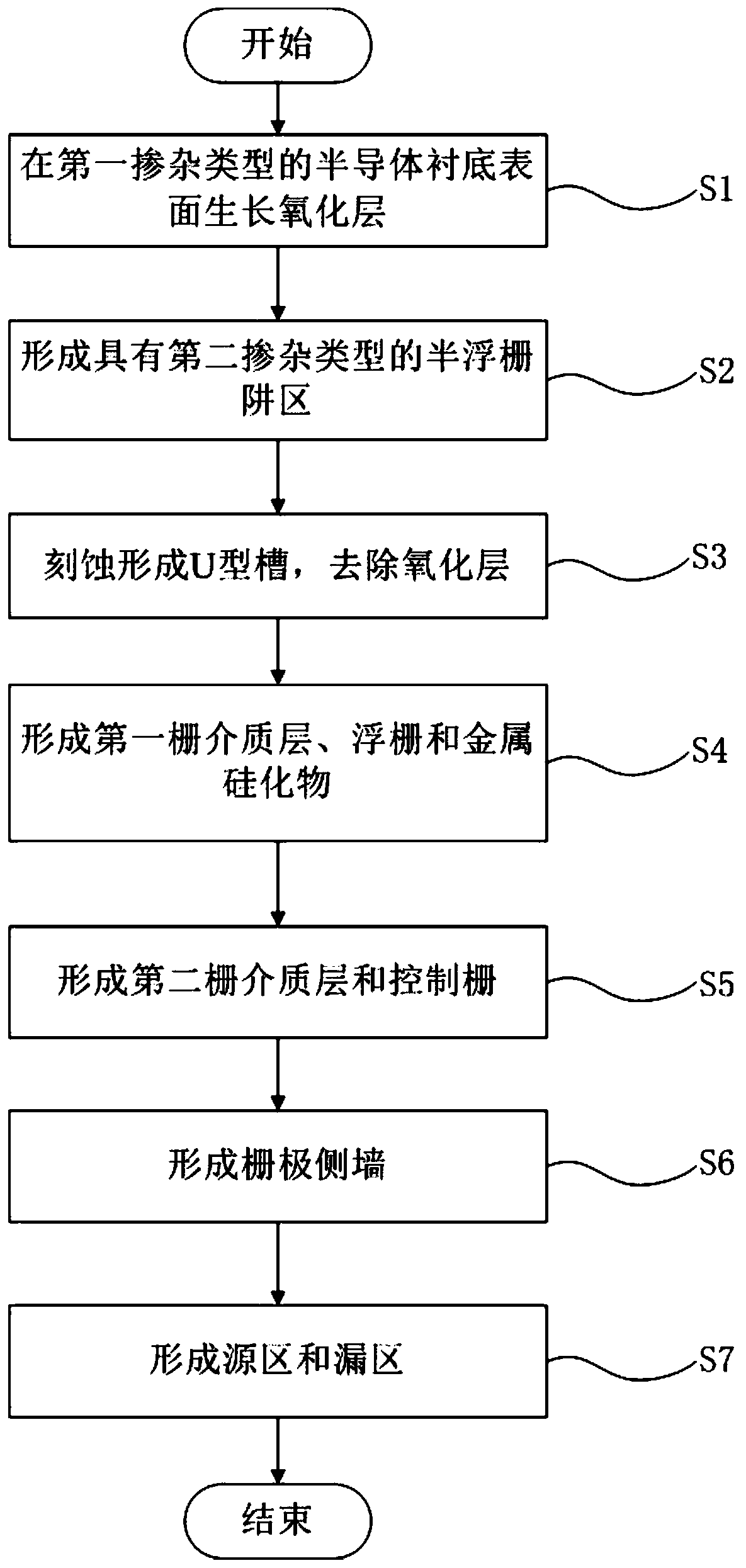

[0040] figure 1 It is a flow chart of the preparation method of the high erasing and writing speed semi-floating gate memory. Figure 2-15 A structural schematic diagram showing each step of the method for manufacturing the high erasing and writing speed semi-floating gate memory. Such as figure 1 As shown, the specific preparation steps are:

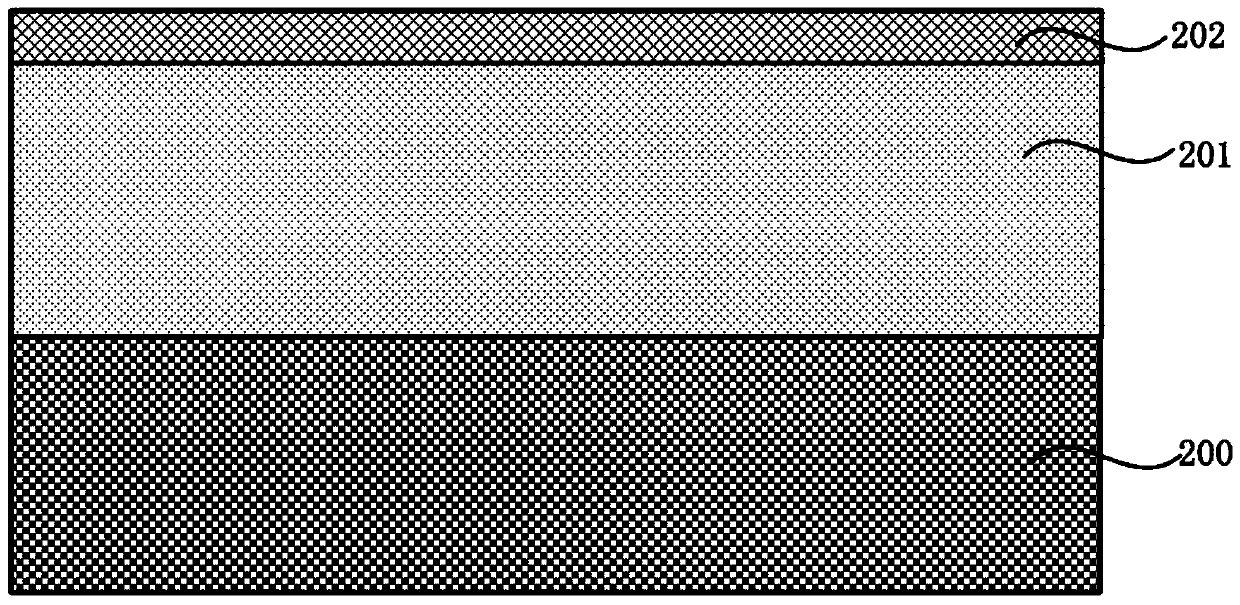

[0041] Step S1, providing a silicon-containing semiconductor substrate 200 with a first doping type. The silicon-containing semiconductor substrate 200 is, for example, a bulk semiconductor substrate such as Si, SiGe, a semiconduct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More