Method for forming field effect transistor and field effect transistor

A field effect transistor and gate technology, applied in the field of semiconductor manufacturing process design, can solve problems such as poor performance of FinFET

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

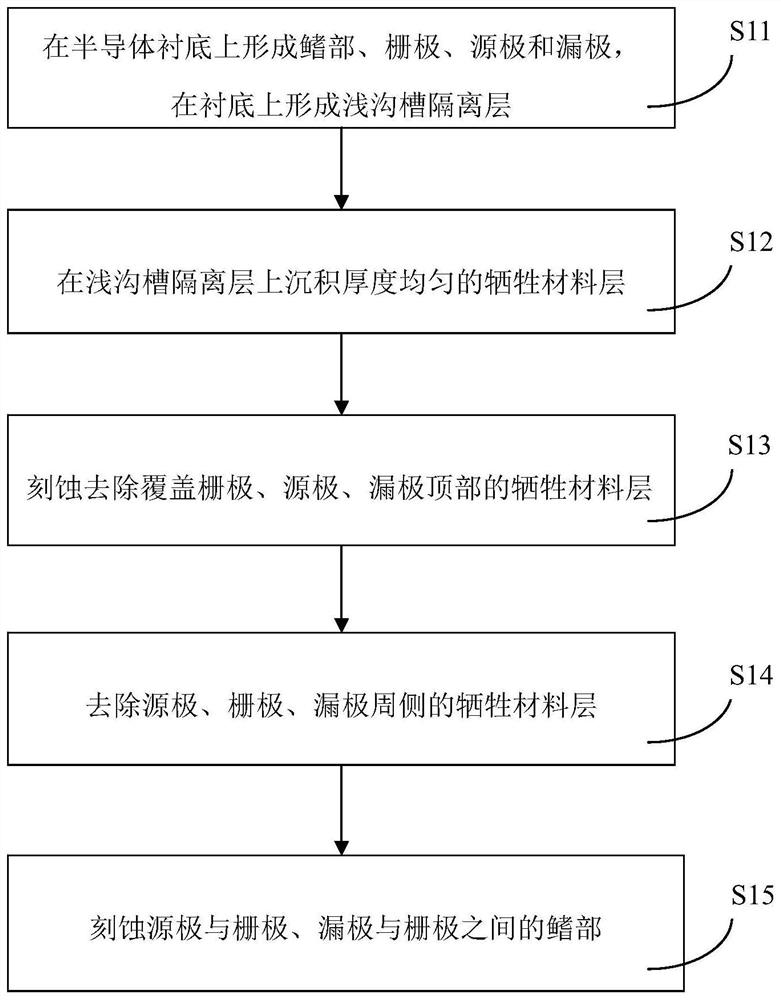

[0039] In order to solve the problem of poor performance of FinFET in the prior art, a method for forming a field effect transistor is proposed. Specifically, see figure 1 , the method for forming the field effect transistor provided in this embodiment includes:

[0040] Step S11: forming a fin, a gate, a source and a drain on the semiconductor substrate, and forming a shallow trench isolation layer on the substrate. More specifically, a semiconductor substrate is provided, and fins are first formed on the semiconductor substrate, then a gate, a source and a drain are formed, and finally a shallow trench isolation layer is formed on the substrate. The substrate is set at the bottom of the field effect transistor and is made of semiconductor material. More specifically, the material of the substrate may be, but not limited to, a sapphire substrate, a silicon carbide substrate, or a silicon substrate. This embodiment uses a silicon substrate.

[0041] Further, the fin is form...

Embodiment 2

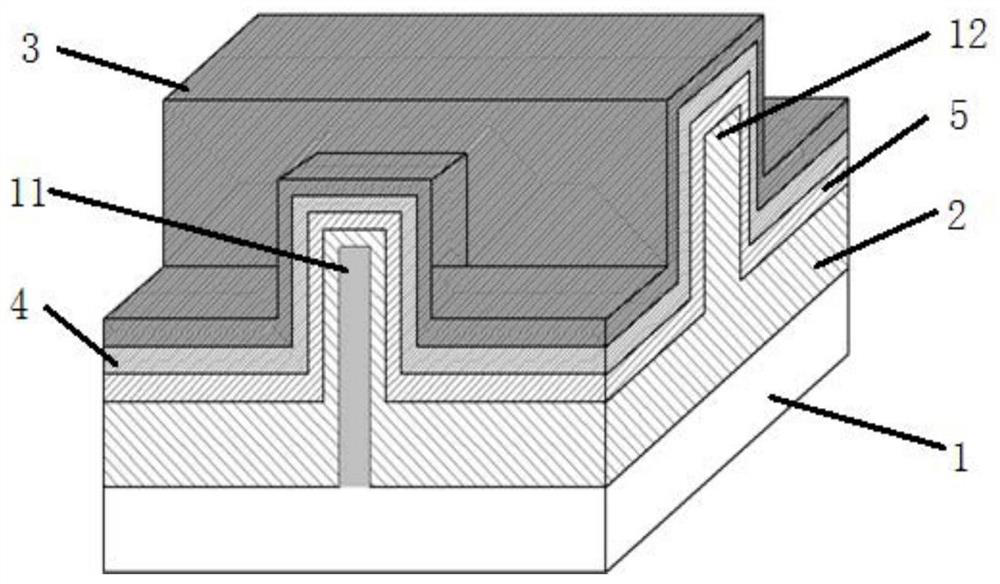

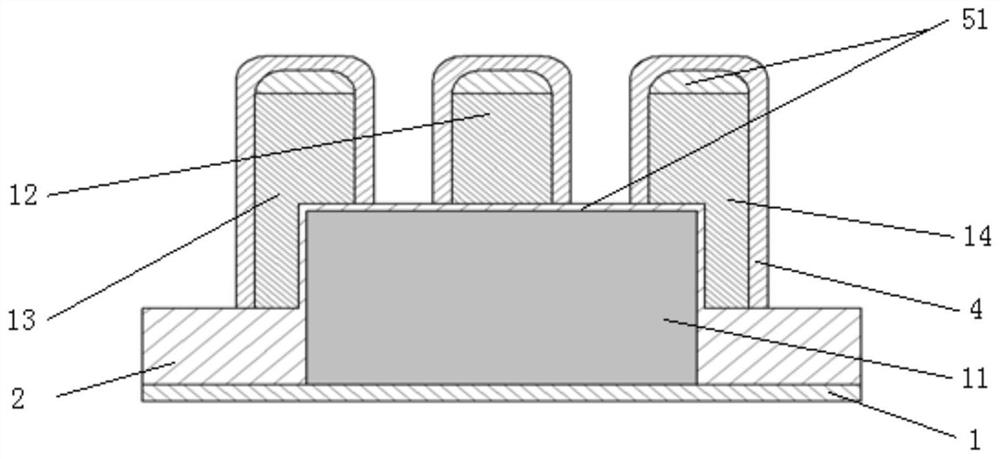

[0060] Based on the method for forming a field effect transistor provided in Embodiment 1, this embodiment provides a method for forming a field effect transistor in which the hard mask layer is a gate mask. Specifically, see Figure 3a-Figure 3e , the steps of the process of forming the FinFET using the gate mask 51 as its hard mask layer 5 may specifically be:

[0061] For the first step, see Figure 3a , providing a semiconductor substrate 1 , forming a fin 11 , a gate 12 , a source 13 and a drain 14 on the semiconductor substrate, and forming a shallow trench isolation layer 2 on the substrate 1 .

[0062] In the second step, see Figure 3b , depositing a sacrificial material layer 3 with a uniform thickness on the shallow trench isolation layer 2 .

[0063] Step three, see Figure 3c , etch and remove the sacrificial material layer 2 covering the tops of the gate 12 , the source 13 and the drain 14 .

[0064] For step four, see Figure 3d , remove the sacrificial ma...

Embodiment 3

[0073] Based on the method for forming a field effect transistor provided in Embodiment 1, this embodiment provides a method for forming a field effect transistor in which the hard mask layer is a well mask. Specifically, see Figure 4a-Figure 4f , the steps of the process of forming the FinFET using the well mask 52 as its hard mask layer 5 may specifically be:

[0074] For the first step, see Figure 4a , providing a semiconductor substrate 1 , forming a fin 11 , a gate 12 , a source 3 and a drain 14 on the semiconductor substrate 1 , and forming a shallow trench isolation layer 2 on the substrate 1 .

[0075] In the second step, see Figure 4b , depositing a sacrificial material layer 3 with a uniform thickness on the shallow trench isolation layer 2 .

[0076] Step three, see Figure 4c , etching and removing the sacrificial material layer 3 covering the tops of the gate 12 , the source 13 and the drain 14 .

[0077] For step four, see Figure 4d , etch the sacrifici...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More