Automatic elimination circuit for input offset voltage of operational amplifier

A technology of operational amplifier and offset voltage, which is applied in the field of automatic elimination circuit, and can solve the problem that the input offset voltage of the amplifier cannot be fully eliminated.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

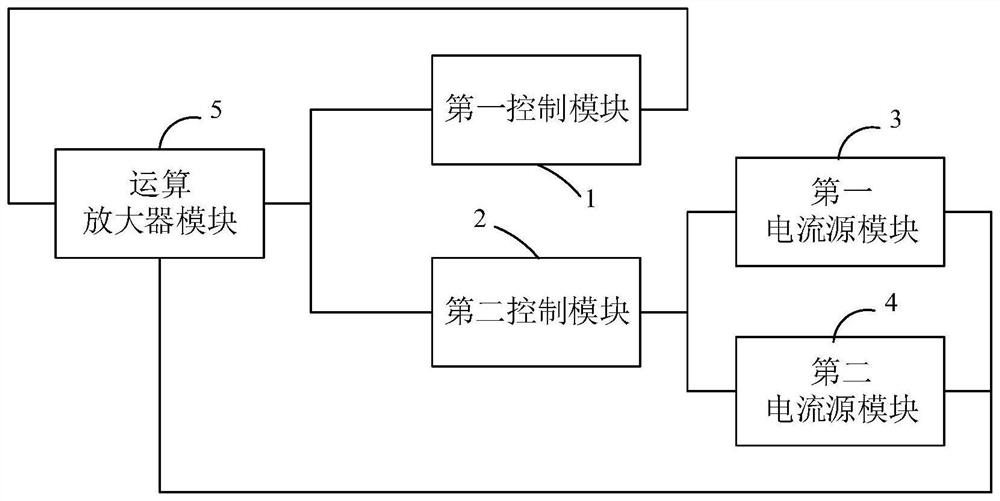

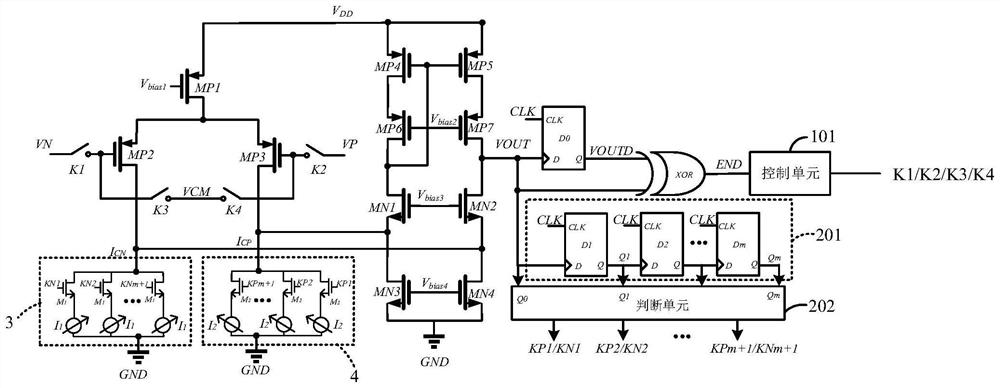

[0051] See figure 1 , figure 1 It is a module schematic diagram of an automatic elimination circuit of an operational amplifier input offset voltage provided by an embodiment of the present invention. As shown in the figure, the automatic elimination circuit of an operational amplifier input offset voltage in this embodiment includes a first control module 1, a second Control module 2, the first current source module 3, the second current source module 4 and operational amplifier module 5, wherein, the first control module 1 produces the first control signal according to the output signal of operational amplifier module 5; The second control module 2 according to The output signal of the operational amplifier module 5 generates a second control signal; the first current source module 3 and the second current source module 4 generate a current signal according to the second control signal; the operational amplifier module 5 realizes the input offset voltage according to the cur...

Embodiment 2

[0063] This embodiment specifically describes the working principle of the automatic elimination circuit for the input offset voltage of the operational amplifier in Embodiment 1. The automatic elimination circuit for the input offset voltage of the operational amplifier in this embodiment includes Offset-Cancelling (OC) mode and In the normal-operation (Normal-Operation, NO) mode, before entering the NO mode, it is first necessary to complete the background elimination of the input offset voltage of the operational amplifier module 5 in the OC mode.

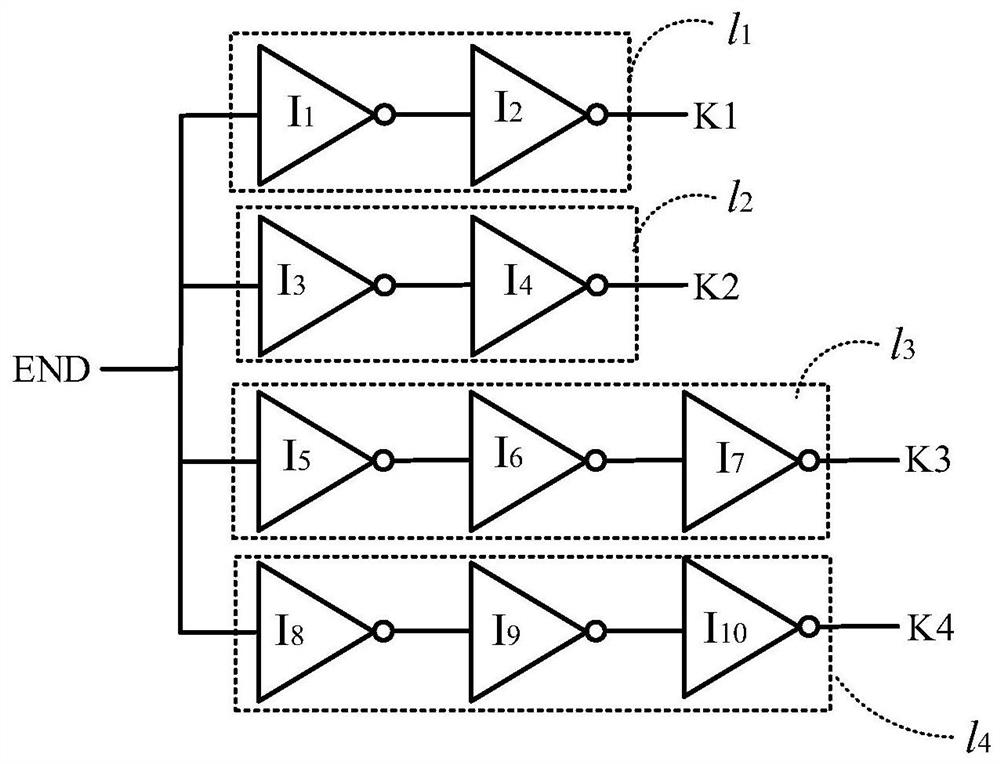

[0064] In the OC mode, the first switch K1 and the second switch K2 are turned off, and at the same time, the third switch K3 and the fourth switch K4 are turned on, and the differential input pair controls the gate voltage of the second PMOS transistor MP2 and the third PMOS transistor MP3 Connect to common mode input voltage terminal VCM. At this time, the operational amplifier module 5 works in an open-loop circuit state. Du...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More