Approximate multiplier design method, approximate multiplier and image sharpening circuit

A design method, multiplier technology, applied in image enhancement, image data processing, CAD circuit design, etc., to achieve the effect of accurate calculation results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

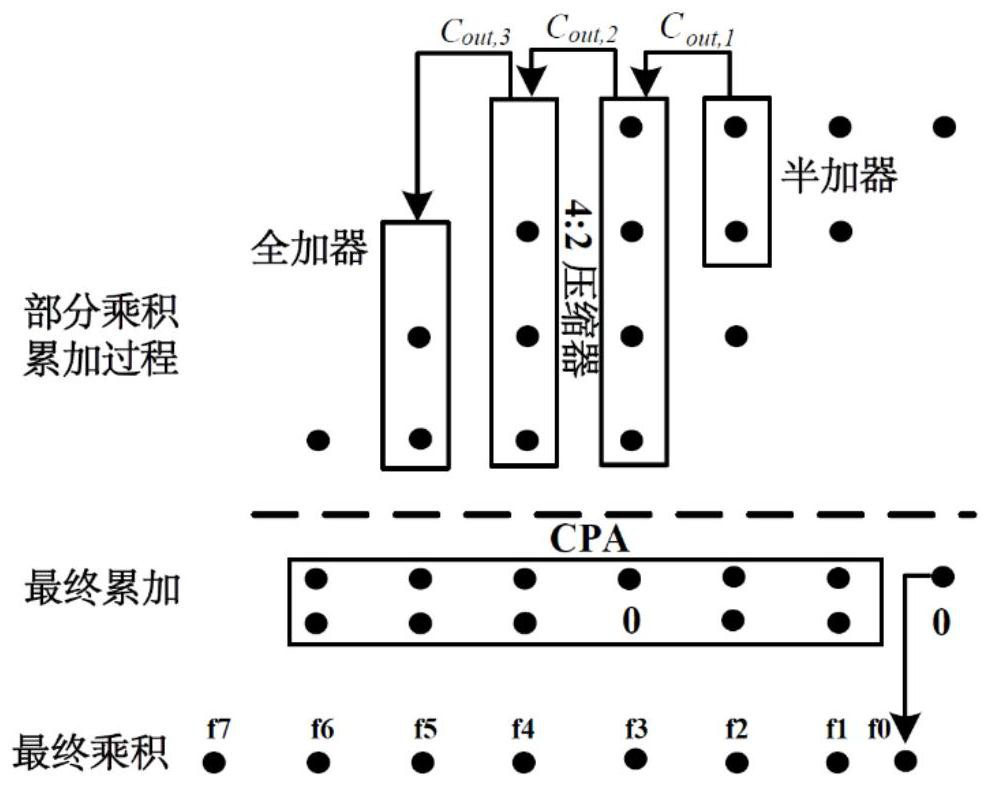

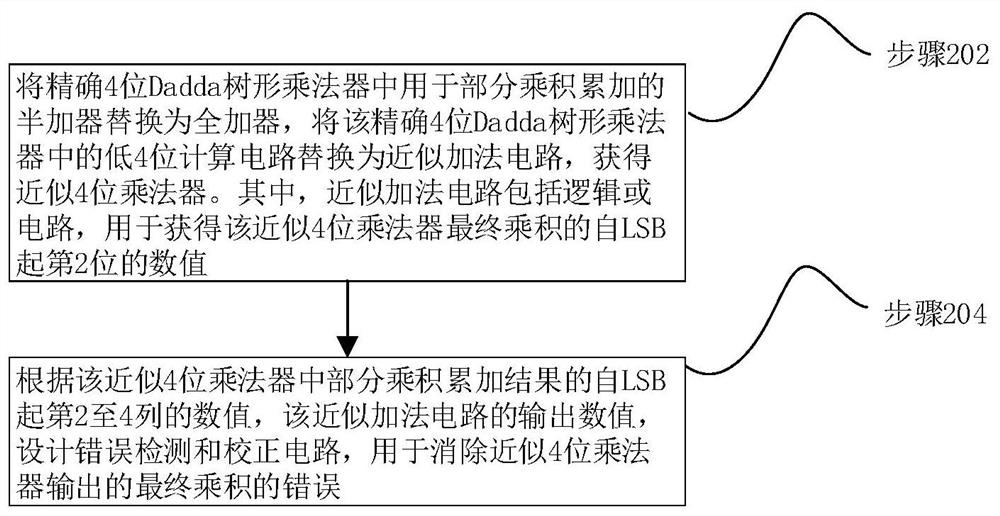

[0029] Accurate 4-bit Dadda tree multipliers in the state of the art, such as figure 1 As shown, in Partial Product Reduction (PPR, Partial Product Reduction), a half adder (HA, Half Adder), a 4:2 compressor and a full adder are used to perform compression accumulation of partial products, and ripple carry addition is used Carry Propagation Adder (CPA, Carry Propagation Adder) performs the final cumulative calculation to obtain the final product. The use of tree structure enables the accumulation process of partial products to be executed in parallel, which improves the u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com