Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of split-gate flash memory failure, short floating gate width, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The manufacturing method of the semiconductor device proposed by the present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention. In addition, the structures shown in the drawings are often a part of the actual structure. In particular, each drawing needs to display different emphases, and sometimes uses different scales.

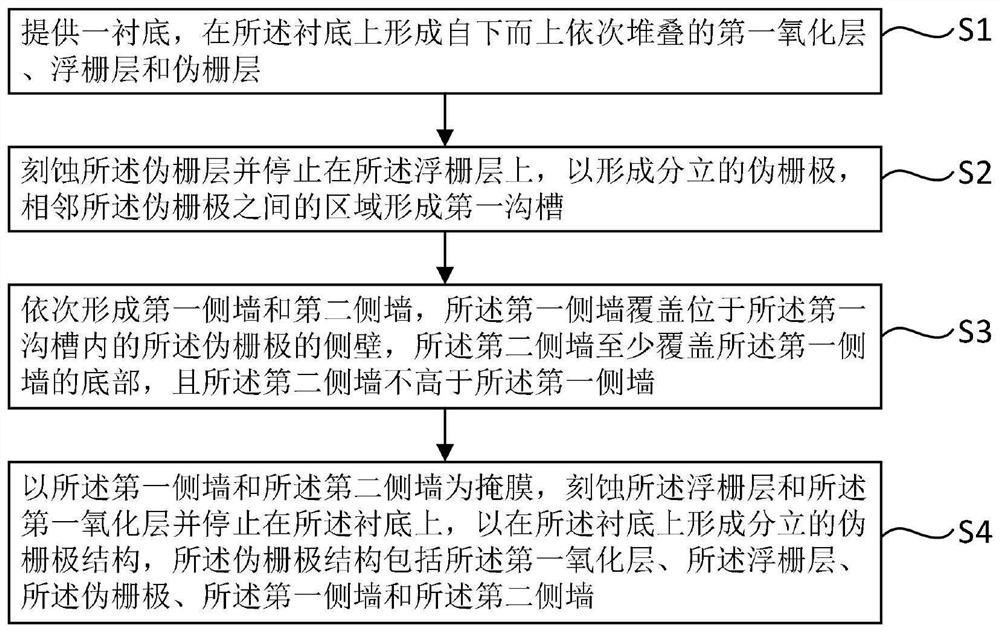

[0040] This embodiment provides a method for manufacturing a semiconductor device, such as figure 1 shown, including:

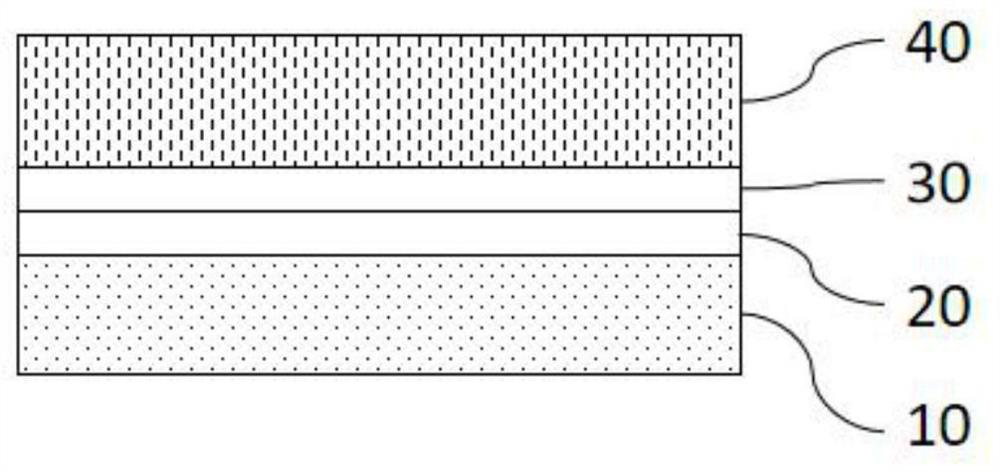

[0041] S1, providing a substrate on which a first oxide layer, a floating gate layer and a dummy gate layer are sequentially stacked from bottom to top;

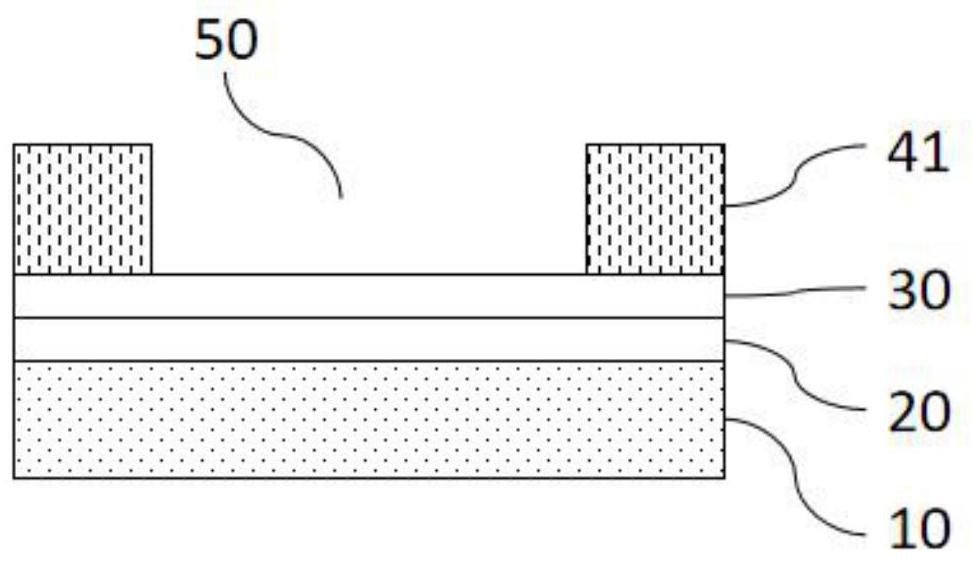

[0042] S2, etching the dummy gate layer and stopping on the floating gate layer to form discr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More