FPGA-based lightweight target detection neural network implementation method

A neural network and target detection technology, which is applied in the realization field of target detection network and lightweight target detection neural network, can solve the problems of large accuracy loss, high computational intensity, poor interpretability of deep learning, etc. Small volume and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

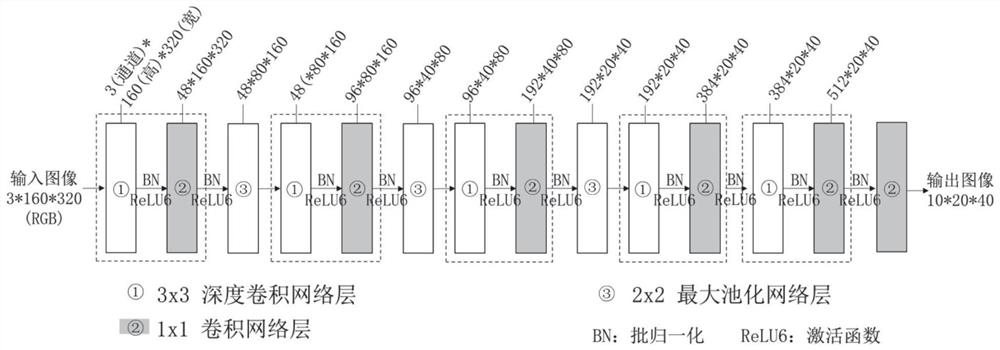

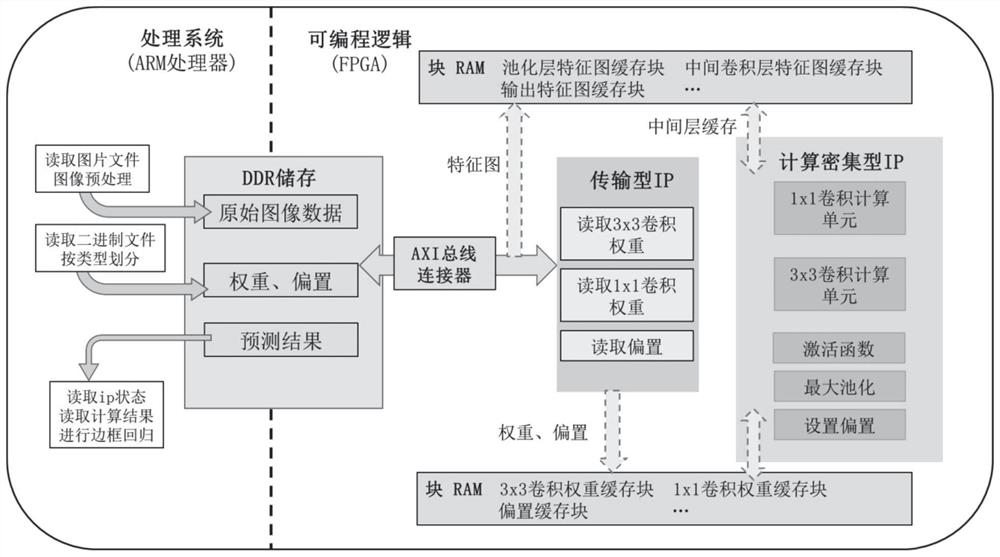

[0057] First, design an effective feature extraction backbone network that can be quickly trained and iteratively designed for migration to subsequent target detection tasks.

[0058] In order to reduce the weight parameters of the network and reduce the time delay, the present invention simplifies the original MobileNet architecture.

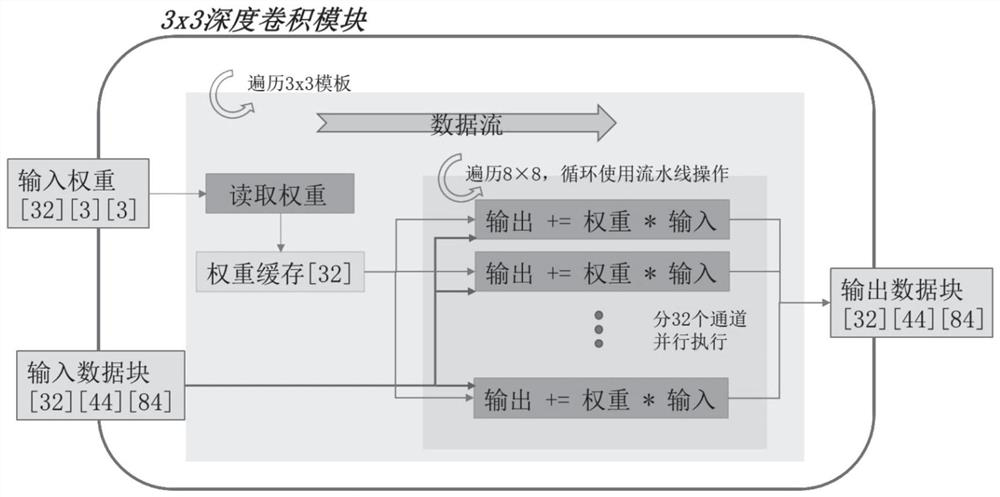

[0059] First, corresponding to the first 13 layers of the prototype architecture, alternate convolution-downsampling operations are performed. The convolution layer deepens the feature channel while reducing the size of the feature map through the pooling layer to gradually extract feature information. The first layer does not go through the traditional convolution of the 3×3 convolution kernel, and directly enters the sub-channel convolution; the implementation of the downsampling operation is replaced by the sub-channel convolution with a sliding step size (stride) of 2 to the maximum of 2×2 Pooling (Max Pooling), reducing the amount of calcu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More