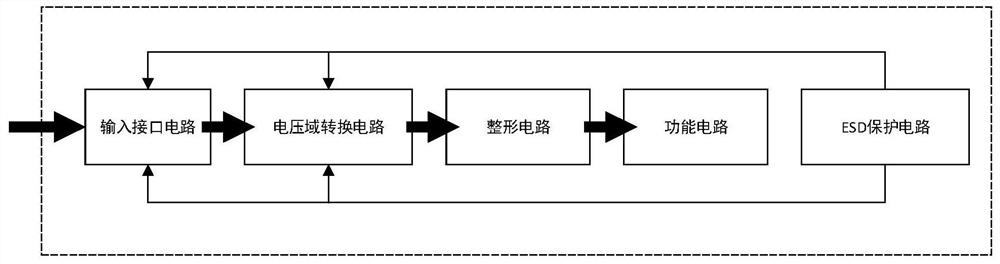

Cross-power-domain circuit and signal processing method

A technology of power supply domain and power supply voltage, applied in the direction of circuit devices, emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc., can solve the problem of increasing chip area and power management costs, reducing interference and noise Issues such as communication speed or quality, reducing chip competitiveness, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

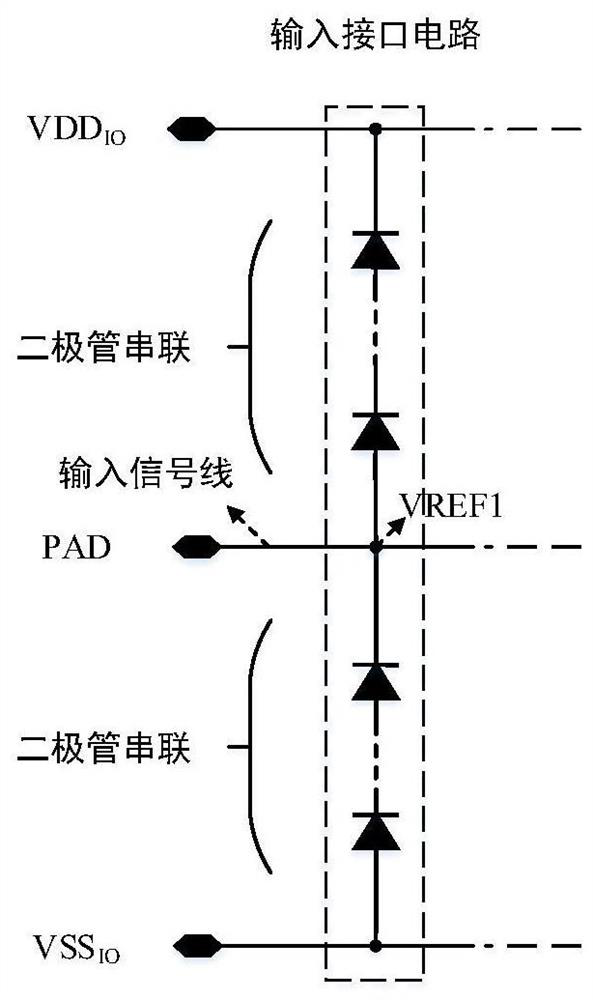

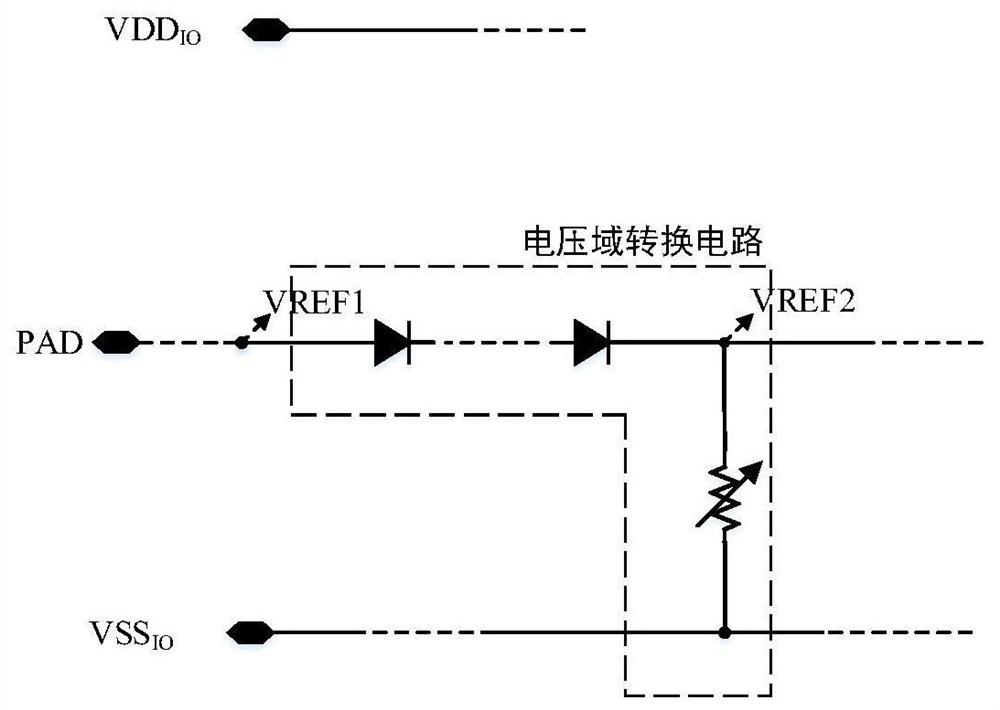

[0056] Implementation example 1: the external signal voltage domain is higher than the power supply voltage domain of the IO interface circuit, and the negative power supply of the IO interface power supply voltage domain is used as the reference ground. Assume that the power supply voltage domain of the IO interface circuit is 1.8V~0V, the external signal voltage domain is 2.4V~0.6V, and the diode conduction threshold V th is 0.4V; under this condition, the overall circuit diagram of the custom IO interface is as follows Figure 10 shown.

[0057] In the input interface circuit, the response range of the first reference voltage node (VREF) can be calculated by the following formula (1):

[0058]

[0059] Among them, N 1 The number of diodes that need to be inserted between the input signal line and the positive power supply network; N 2 The number of diodes that need to be inserted between the input signal line and the negative power supply network; VDD IO It is the po...

Embodiment 2

[0067] Implementation example 2: the external signal voltage domain is lower than the power supply voltage domain of the IO interface circuit, and the negative power supply of the IO interface power supply voltage domain is used as the reference ground. Assume that the power supply voltage domain of the IO interface circuit is 1.8V~0V, the external signal voltage domain is 1.2V~-0.6V, and the diode conduction threshold V th is 0.4V; under this condition, the overall circuit diagram of the custom IO interface is as follows Figure 12 shown.

[0068] Similarly, in the input interface circuit, the response range of the first reference voltage node ( VREF1 ) can be calculated by formula (1). In order to ensure that the response range of the first reference voltage node (VREF1) matches the range of the external input signal voltage domain, it can be seen from formula (1) that at least two ESD diodes need to be inserted between the input signal line and the negative power supply ne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More