High-voltage asymmetric structure ldmos device and its preparation method

An asymmetric structure and device technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of increased on-resistance of devices, achieve the effects of improving breakdown voltage, ensuring performance, and improving control capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

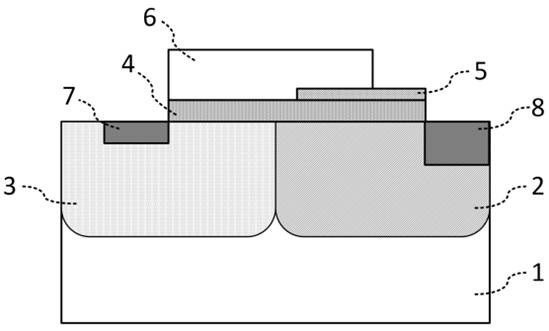

[0051] figure 1 It is a schematic structural diagram of a high-voltage asymmetric structure LDMOS device provided in the first embodiment of the present invention. In this embodiment, the drift region 2 and the body region 3 of the LDMOS device are in lateral contact.

[0052] specific reference Figure 1 to Figure 7 As shown, the LDMOS device has: a drift region 2 and a body region 3; the surface of the drift region 2 is divided into a first region 201 and a second region 202; the surface of the body region 3 is divided into a third region 301 and a The fourth region 302, the second region 202 and the fourth region 302 are extended and covered by the first gate dielectric layer 4; the surface of the first gate dielectric layer 4 is divided into a seventh region 401, the seventh region 401 is located above the drift region 2 and covered by the second gate dielectric layer 5; the surface of the second gate dielectric layer 5 is divided into a sixth region 502 and a fifth regi...

Embodiment 2

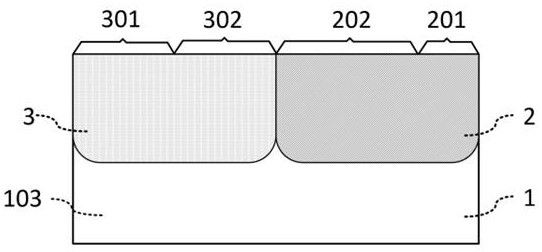

[0058] Figure 8 It is a schematic structural diagram of a high-voltage asymmetric structure LDMOS device provided by the second embodiment of the present invention. In this embodiment, the drift region 2 and the body region 3 of the LDMOS device are laterally spaced apart by the ninth region 103 of the substrate 1 .

[0059] Figure 9 It is a flow chart of a method for manufacturing a high-voltage asymmetric structure LDMOS device provided by an embodiment of the present invention, such as Figure 9 Shown, described preparation method comprises:

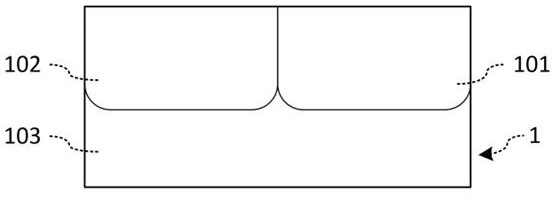

[0060] S1: dividing the eighth region 102 on the substrate to form the body region 3; dividing the tenth region 101 to form the drift region 2;

[0061] S2: Divide a first region 201 and a second region 202 on the surface of the drift region 2; divide a third region 301 and a fourth region 302 on the surface of the body region 3, the second region 202 and the The fourth area 302 is adjacent to each other;

[0062] S3: growing a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More