Full-chip rapid simulation method of negative development photoetching process, negative development photoresist model, OPC model and electronic equipment

A photoresist model and photolithography process technology, applied in microlithography exposure equipment, optomechanical equipment, photolithography process exposure devices, etc., can solve the problems of low optimization speed, poor accuracy of negative development photoresist, etc. Achieve the effect of improving accuracy, improving calculation speed, and solving complex process calculations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the purpose, technical solutions and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and implementation examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

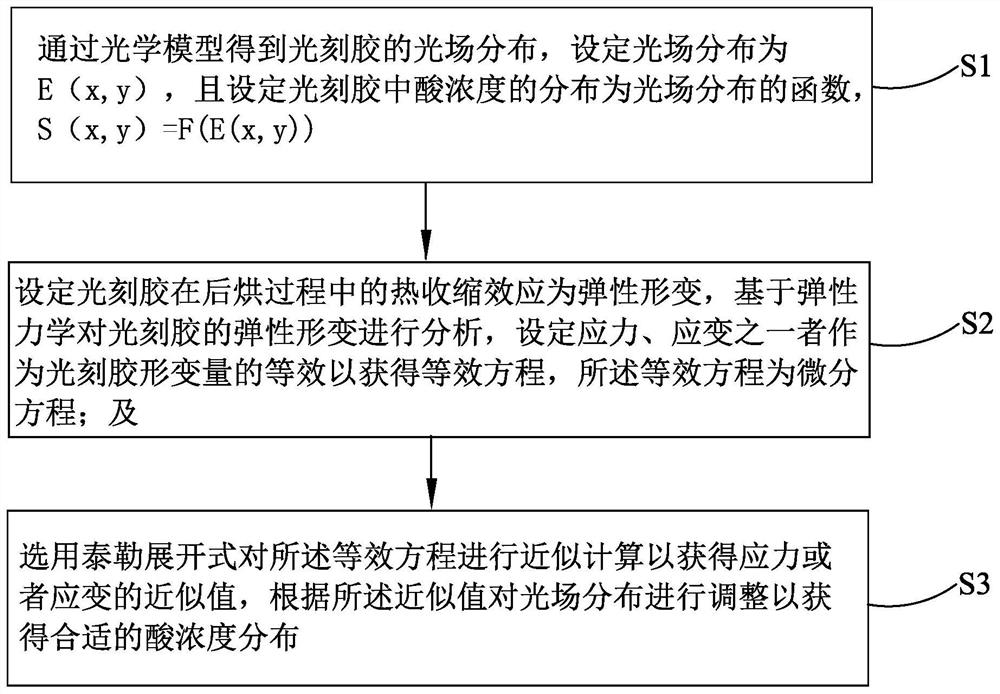

[0045] see figure 1 , the first embodiment of the present invention provides a full-chip rapid simulation method for a negative development photolithography process, including the following steps:

[0046] S1. Obtain the light field distribution of the photoresist through the optical model, set the light field distribution as E(x, y), and set the distribution of the acid concentration in the photoresist as a function of the light field distribution, that is, S(x, y)=F(E(x,y)).

[0047]In this step, the negative developing technique is an image reversal developing technique, which...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More