Method for realizing robust clock tree comprehensive algorithm for near threshold

A clock tree synthesis and implementation method technology, applied in the field of robust optimization, can solve problems affecting buffer timing, clock tree deviation and maximum conversion time, etc., to achieve fast synthesis process, small clock deviation, and strong generalization ability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described below in conjunction with accompanying drawing:

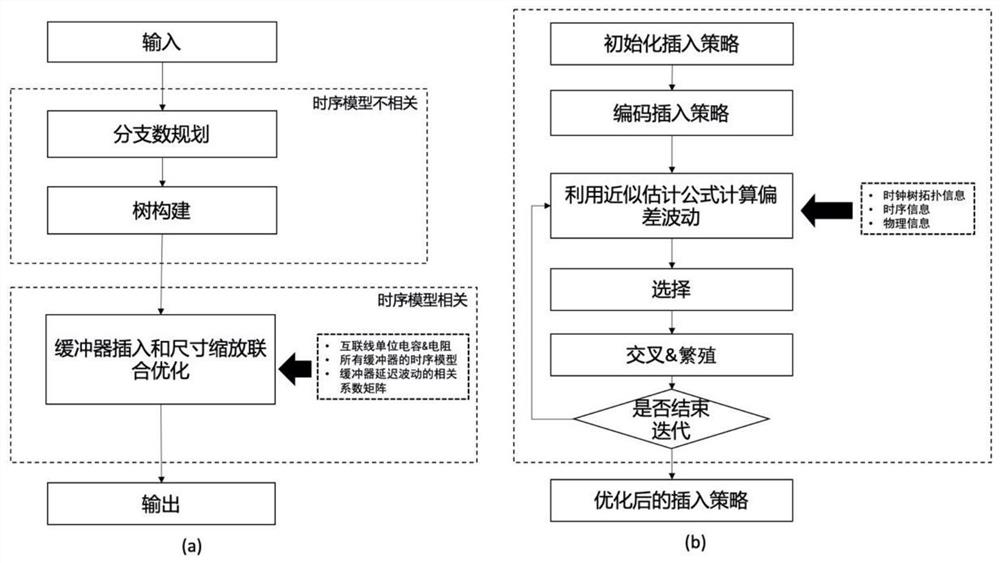

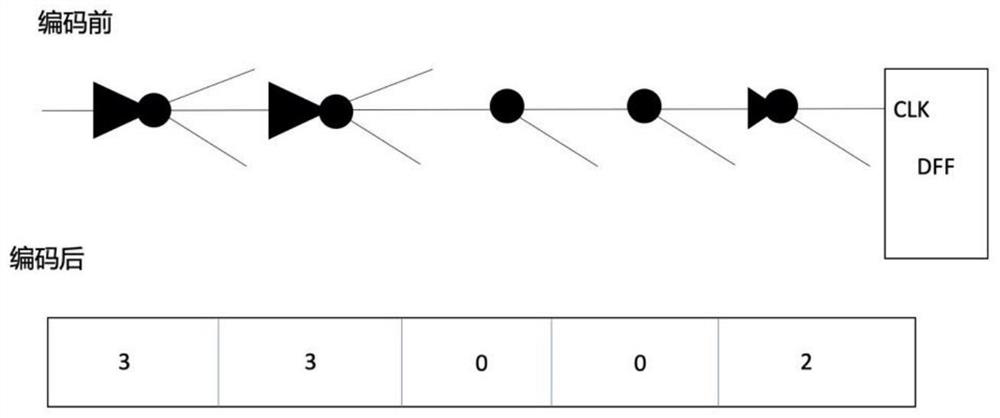

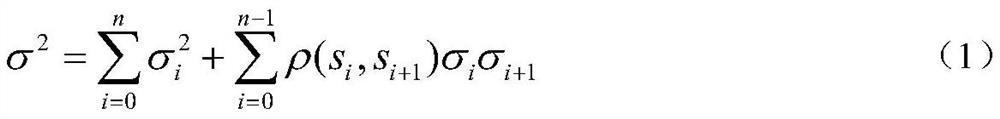

[0030] The present invention applies the symmetrical clock tree structure to the design of the near-threshold value to ensure a small clock deviation. At the same time, a buffer insertion strategy oriented to the buffer library is adopted, and the size of the buffer is scaled during the insertion process to reduce the size of the buffer as much as possible. Clock skew fluctuations due to insertion. figure 1 It is an overall flowchart of the present invention, and the whole flow takes all register position information and clock buffer library as input, and takes maximum conversion time and maximum load capacitance as constraints. The goal of the entire flow is to build a symmetrical buffer-plugged clock tree structure with minimal clock skew fluctuations while satisfying constraints at near-threshold. The whole process is divided into two parts, such as figure 1 (a) and f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More