Digital background self-calibration circuit structure and method of single-channel high-speed high-precision SAR ADC

A circuit structure, high-precision technology, applied in the direction of analog/digital conversion calibration/test, electrical components, analog/digital conversion, etc., can solve problems such as difficult accuracy and limited ADC data conversion speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

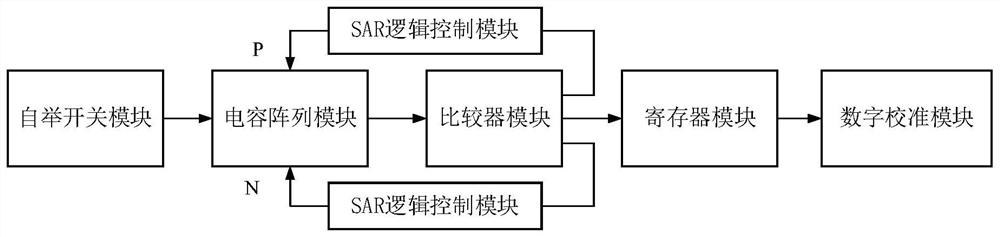

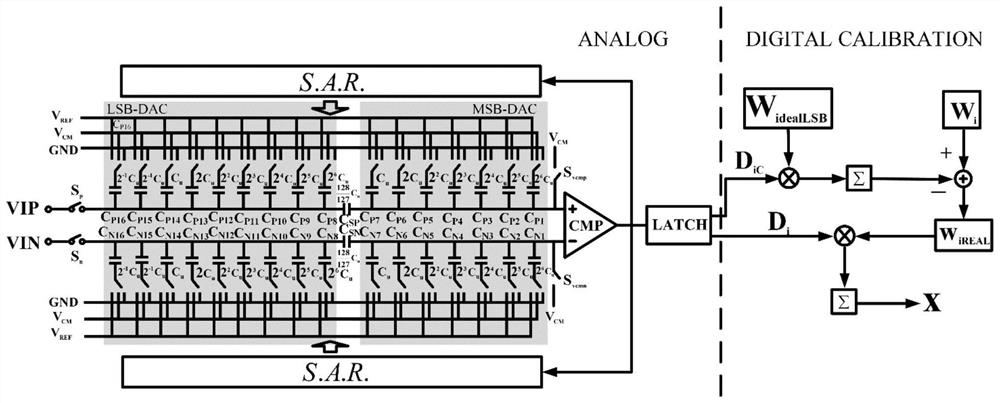

[0055] see figure 1 with image 3 , figure 1 It is a digital background self-calibration circuit module diagram of a single-channel high-speed high-precision SAR ADC provided by an embodiment of the present invention, image 3 It is a digital background self-calibration circuit structure diagram of a single-channel high-speed high-precision SAR ADC provided by an embodiment of the present invention. A digital background self-calibration circuit structure of single-channel high-speed high-precision SAR ADC, including: bootstrap switch module, capacitor array module, comparator module, register module, SAR logic control module and digital calibration module, bootstrap switch module, capacitor The array module, the comparator module, the register module and the digital calibration module are connected sequentially, and the SAR logic control module is connected between the bottom plate of the P terminal and the N terminal of the capacitor array module and the output terminal of ...

Embodiment 2

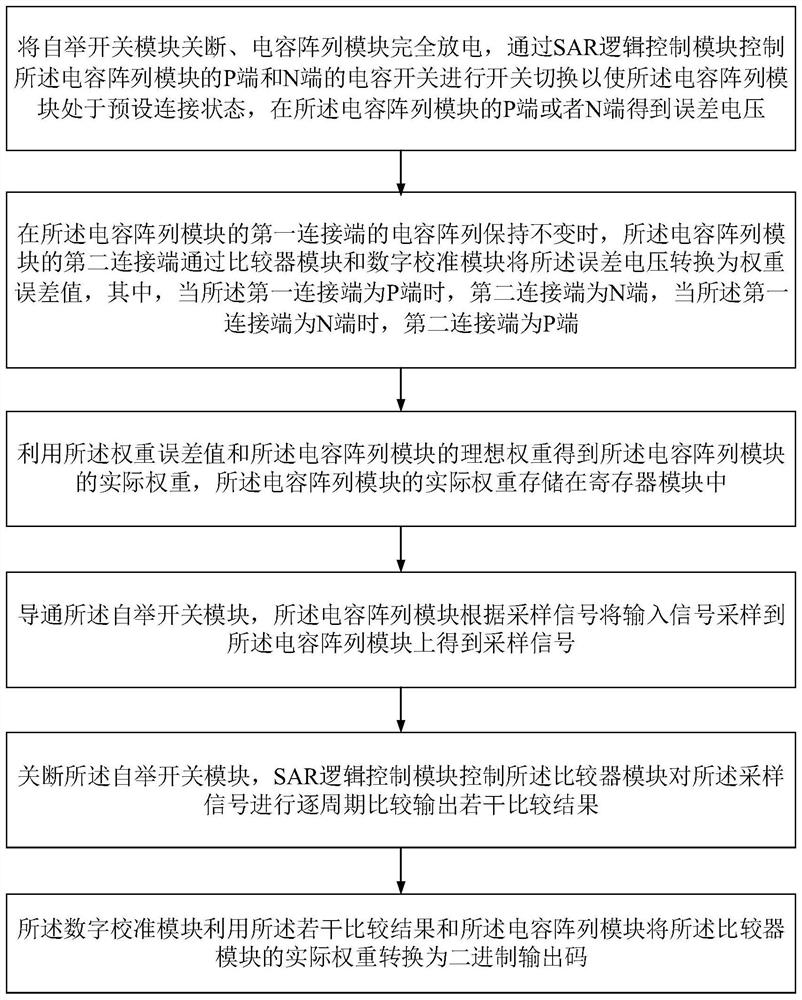

[0086] See figure 1 , figure 2 with image 3 , figure 1 It is a digital background self-calibration circuit module diagram of a single-channel high-speed high-precision SAR ADC provided by an embodiment of the present invention, figure 2 It is a flow chart of a digital background self-calibration method of a single-channel high-speed high-precision SAR ADC provided by an embodiment of the present invention, image 3 It is a digital background self-calibration circuit structure diagram of a single-channel high-speed high-precision SAR ADC provided by an embodiment of the present invention. A digital background self-calibration method of a single-channel high-speed high-precision SAR ADC provided by an embodiment of the present invention includes:

[0087] Step 1. Turn off the bootstrap switch module, fully discharge the capacitor array module, and control the P-terminal and N-terminal capacitor switches of the capacitor array module through the SAR logic control module to...

Embodiment 3

[0118] See Figure 5 with Image 6 , Figure 5 It is a digital background self-calibration circuit simulation diagram of a single-channel high-speed high-precision SAR ADC provided by the embodiment of the present invention. Image 6 It is a circuit uncalibrated simulation diagram of a single-channel high-speed high-precision SAR ADC provided by the embodiment of the present invention. This embodiment can be completed through the following simulation experiments.

[0119] Simulation conditions

[0120] A bridge capacitor is used, the capacitance mismatch sigma=0.01, the parasitic parameters of the top plate of the capacitor are 0.002, the parasitic parameters of the bottom plate of the capacitor are 0.001, and the number of Monte Carlo experiments is 2000 times.

[0121] Simulation content and results

[0122] The effective digits of the self-calibration circuit simulation diagram are mainly distributed around 13.6 bits, and the effective digits of the uncalibrated circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More