Patents

Literature

78results about How to "Improve build accuracy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

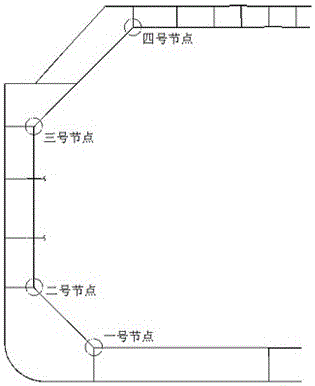

Testing tool system and testing method for LNG ship liquid cargo compartment three-dimensional board CM nodes

ActiveCN106679533AQuick assembly and loadingImprove build accuracyMechanical measuring arrangementsGreek letter alphaElectrical and Electronics engineering

The invention discloses a testing tool system for LNG ship liquid cargo compartment three-dimensional board CM nodes. The testing tool system comprises an inner clamping template and an outer clamping template. The inner clamping template is used for aligning the LNG ship liquid cargo compartment three-dimensional board CM node. The outer clamping template is used for verifying in a CM node verification stage after welding of the LNG ship liquid cargo compartment three-dimensional board CM node. The three-dimensional board comprises a transverse board, a vertical board and an oblique board. An included angle between the transverse board and the oblique board is alpha. A first reference line which is perpendicular with the transverse board is engraved on the transverse board. A second reference line which is perpendicular with the vertical board is engraved on the vertical board. According to the testing tool system, testing templates which matches the three-dimensional board are utilized. The testing templates comprise the inner clamping template for quick assembling and loading, thereby ensuring high precision and high stability in assembly. The testing templates further comprise the outer clamping template for after-welding verification. For ensuring high accuracy in final state measurement, the specialized outer clamping template is utilized, thereby truly testing the final deviation of each node.

Owner:HUDONG ZHONGHUA SHIPBUILDINGGROUP

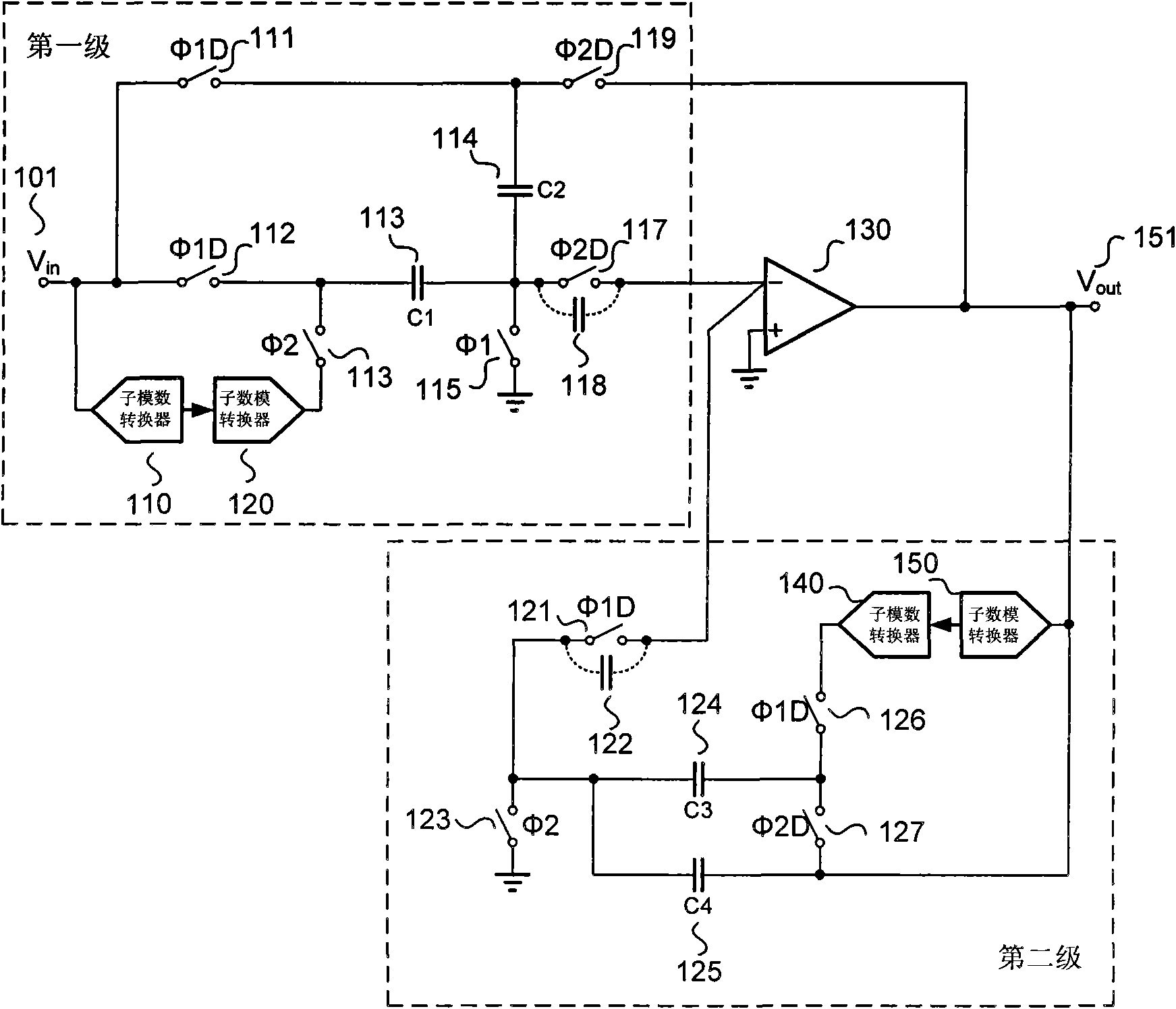

Double-input operational amplifier shared margin gain amplifying circuit

InactiveCN101860335AHigh precisionReduce power consumptionGain controlDifferential amplifiersCircuit complexityCapacitance

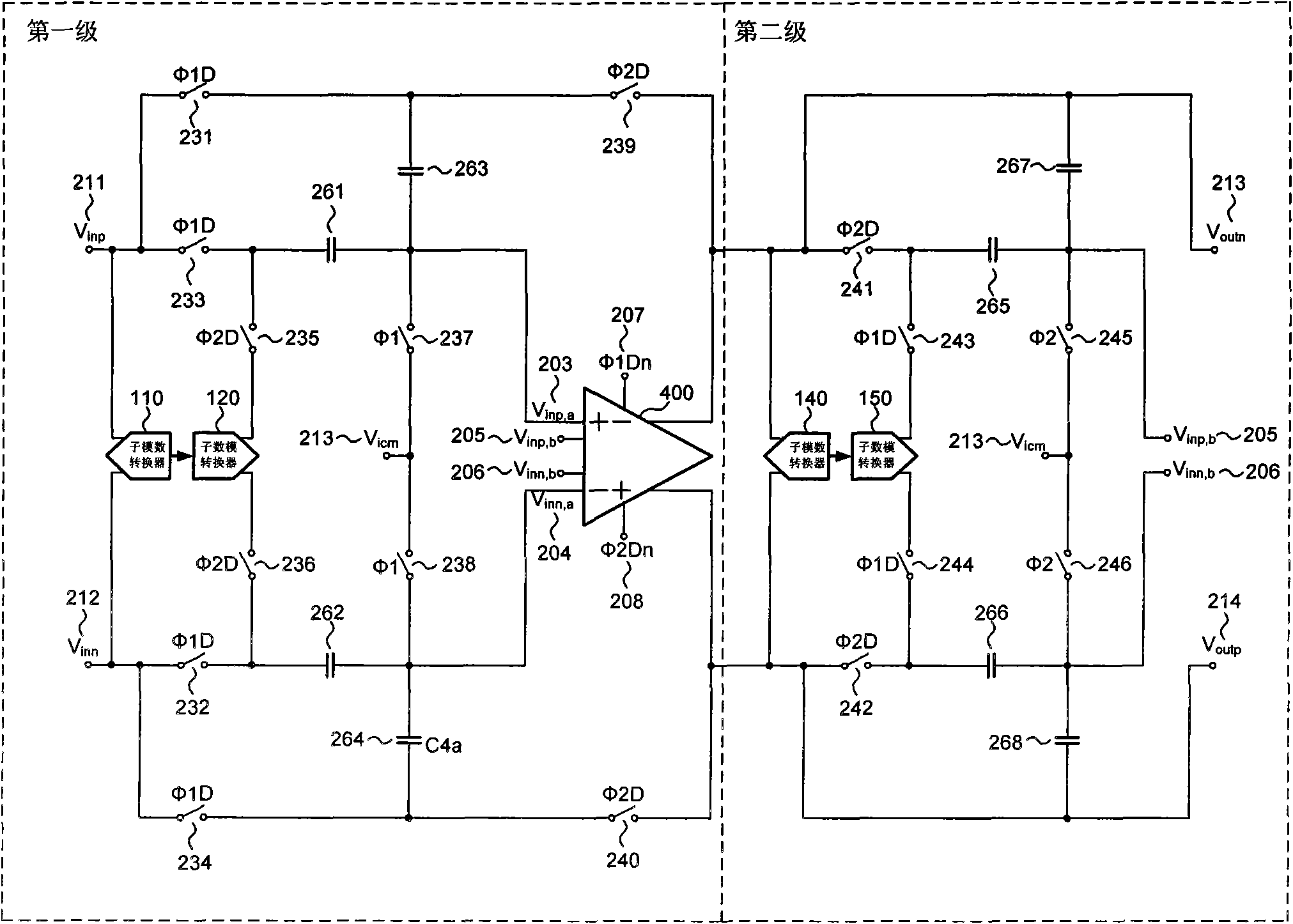

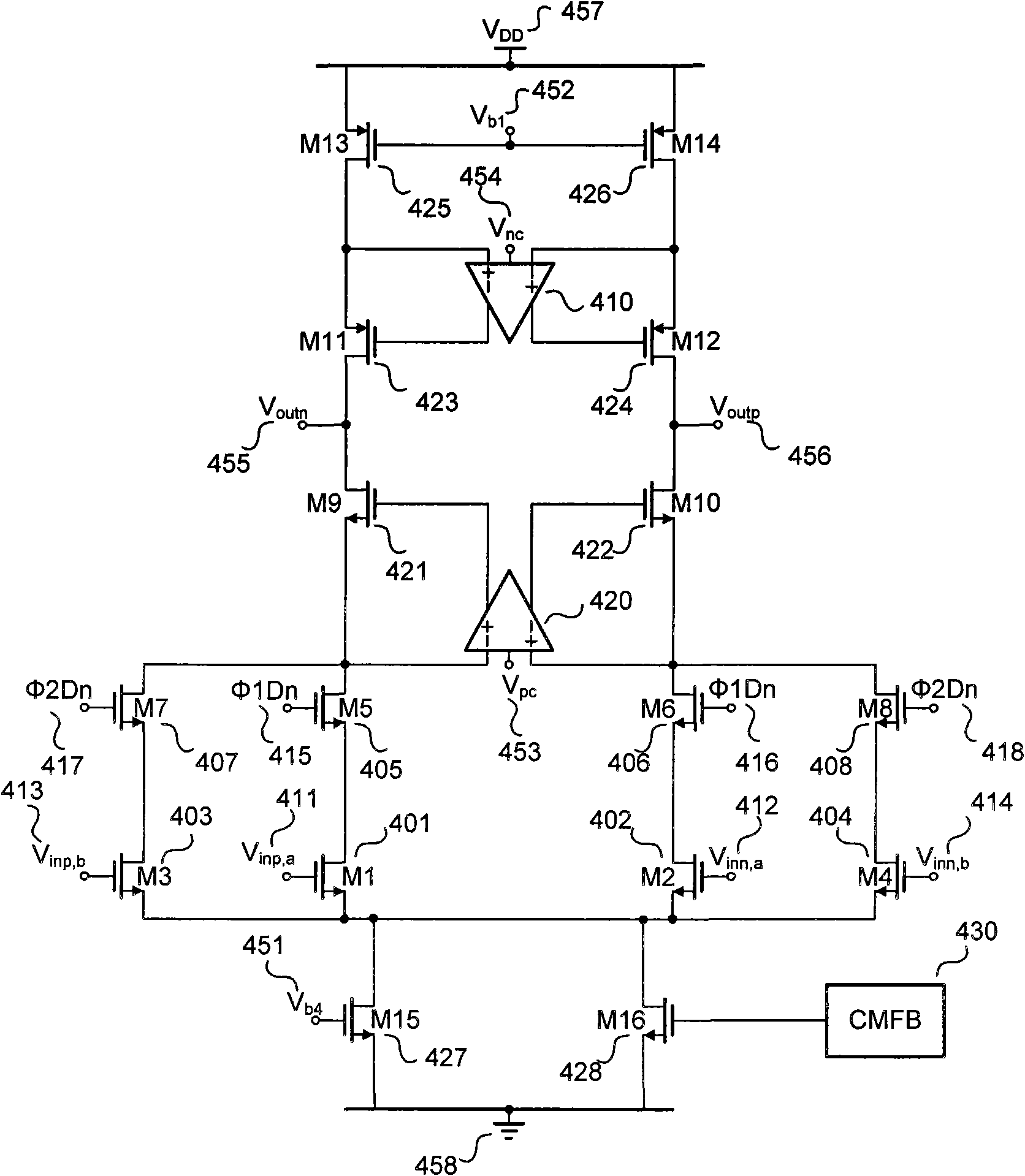

The invention belongs to the technical field of data converters in integrated circuit design, and discloses a double-input operational amplifier shared margin gain amplifying circuit. The amplifying circuit comprises a double-input operational amplifier, a clock generating circuit, a sub digital-to-analog converter, a sub analog-to-digital converter, a capacitor, a switch and the like. Two groups of differential input pair tubes are controlled through the switch controlled by bidirectional overlapped clocks and embedded inside the operational amplifier by adopting the operational amplifier of two groups of input differential pairs and are alternately used at two phases of the clocks, and meanwhile the input differential pairs are alternately reset to a common-mode input voltage so as to fully eliminate the influence of memory effect and inter-stage feed-through in the traditional circuit, improve the signal establishing precision under the condition of keeping the same area, power consumption and circuit complexity and further improve the precision of analog-to-digital conversion.

Owner:FUDAN UNIV

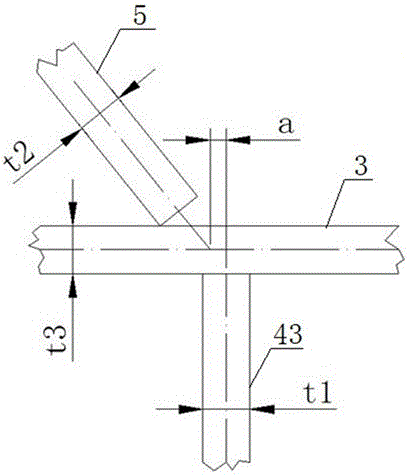

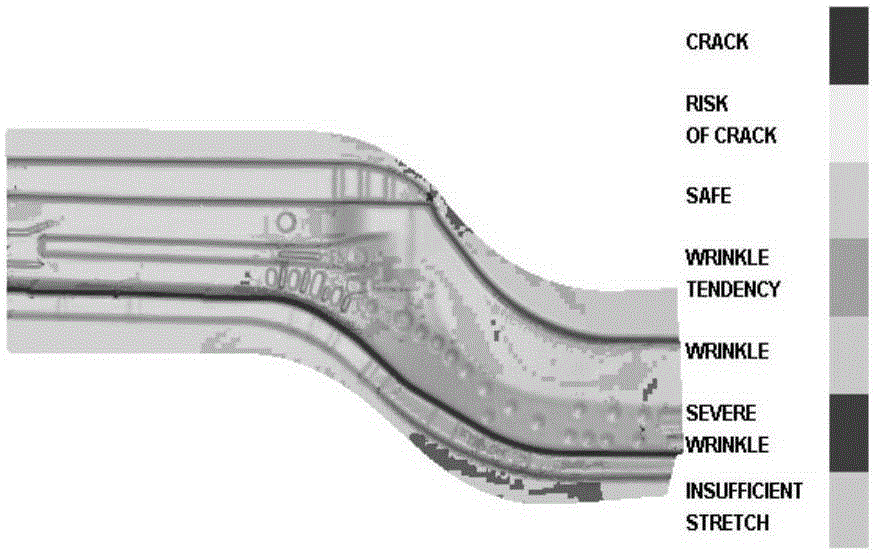

Stamping computer simulation calculating method with consideration of mold deformation

InactiveCN105183932AImprove build accuracyAccurate Stress Field ResultsSpecial data processing applicationsState of artFinite element software

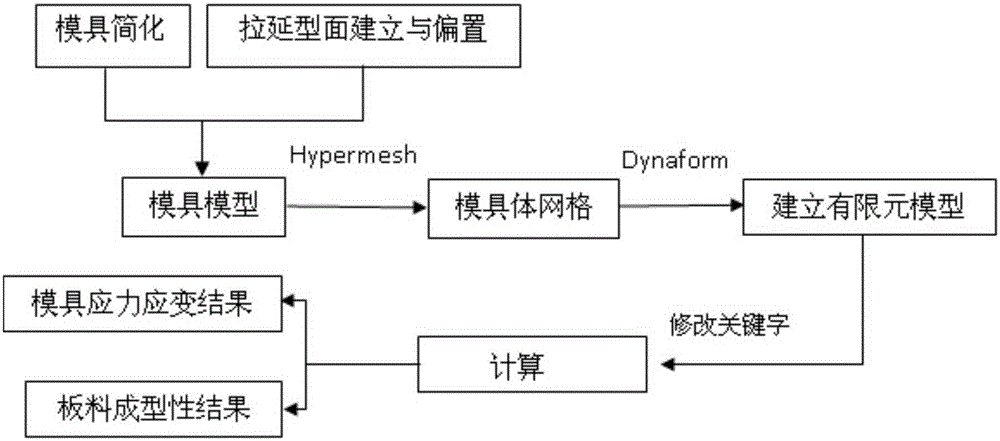

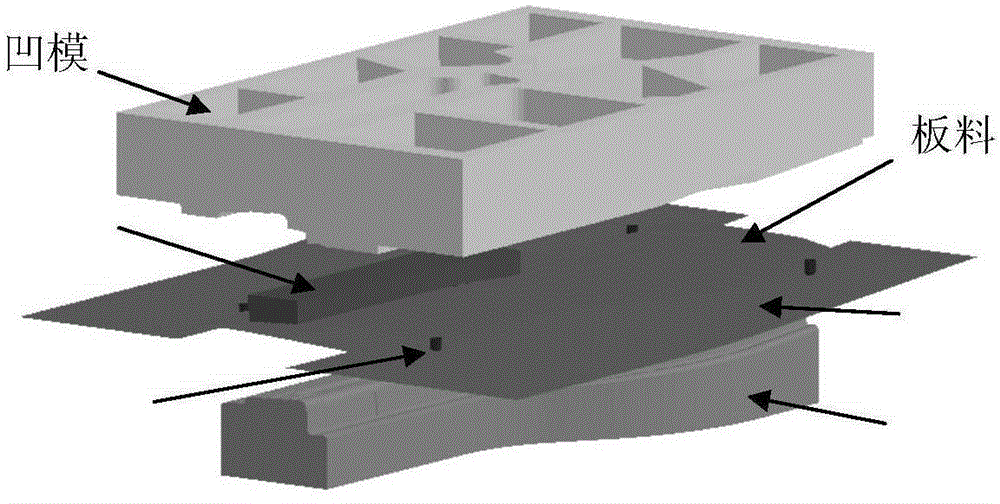

The invention provides a stamping computer simulation calculating method with consideration of mold deformation. The method comprises the following steps of: a step 1, building a mold model; a step 2, performing mesh division for the mold model built in the step 1; a step 3, performing mesh division for sheet material of the mold in a finite element software Dynaform, and setting stamping process parameters and material property parameters of the mold; and a step 4, setting state of motion of a convex mold, a concave mold and a pressure plate through a finite element pre-processing software hypermesh, performing elastomeric setting for the mold, completing finite element simulation of the stamping process, and obtaining a stress strain result of the mold and a sheet material molding result. In comparison with the prior art, in the method provided by the invention, while performing numerical simulation of sheet material molding, the mold is set as an elastoplastic deformation body, influence of mold deformation on numerical simulation of sheet material molding is considered, and an analysis method which has higher precision and is more suitable for stamping numerical simulation of high strength steel plates is established..

Owner:湖南大捷智能装备有限公司

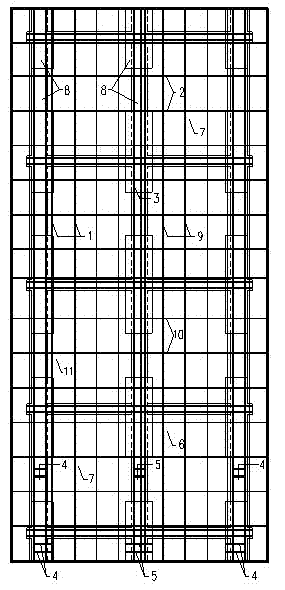

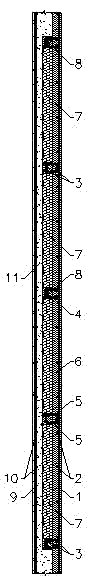

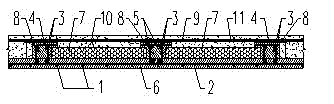

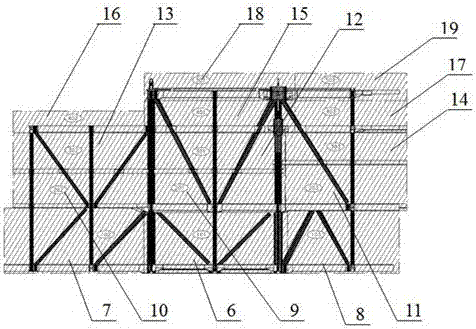

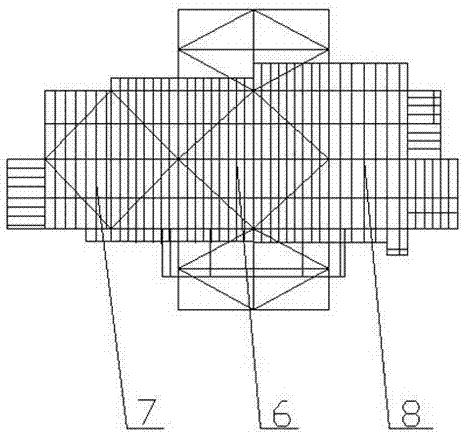

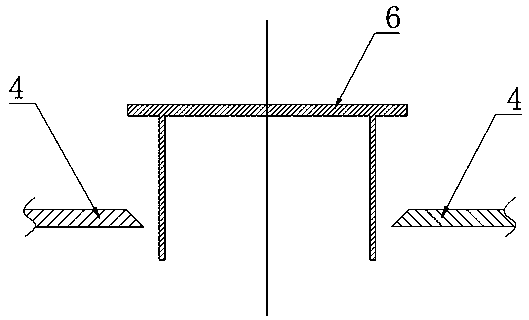

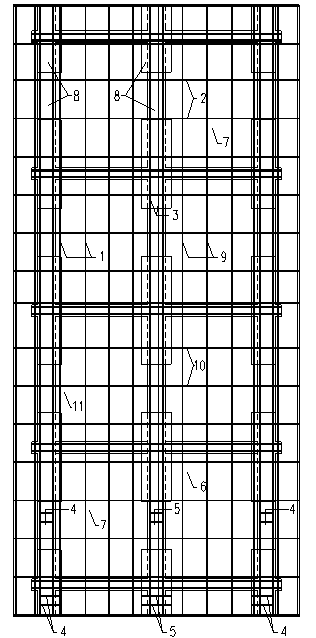

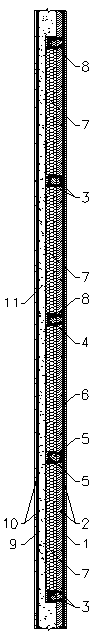

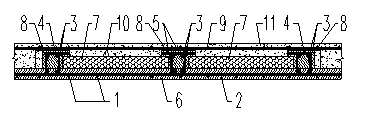

Manufacturing method of fabricated support-free prefabricated ribbed light superposed floor slab

ActiveCN103031952ARealize factoryEasy to install on siteFloorsBuilding material handlingFalseworkFloor slab

The invention provides a manufacturing method of a fabricated support-free prefabricated ribbed light superposed floor slab, and relates to a manufacturing method of a building floor slab. The method comprises the following steps of: firstly processing bottom longitudinal ribs (or prestressed tendons) and transverse reinforcing steel bars of a prefabricated slab, slab rib longitudinal bars (or prestressed tendons) 3, stirrups 4 or bonding ribs 5 of the prefabricated slab; placing the reinforcing steel bars in a production mold of the prefabricated slab; binding the reinforcing steel bars; casting concrete 6 of a bottom plate of the prefabricating part; putting polyphenyl plates 7 or other light materials in corresponding amount according to requirements; then pouring arris of slab 8; finishing factory processing through curing; in the construction site, hanging the floor slab in place, and then putting the longitudinal and transverse reinforcing steel bars 10 at the upper part of the floor slab; and casting the concrete 11 at the upper part of the floor slab, and curing to finish the support-free prefabricated ribbed light superposed floor slab. By adopting the technology, the slab forms and scaffolding work can be basically eliminated at the construction site; the waste of the building material can be reduced to a maximum extent; the industrial and standardized production of the floor slab can be satisfied; and the integral site assembly of the floor slab can be satisfied.

Owner:LIAONING YIZHU BUILDING MATERIALS CO LTD

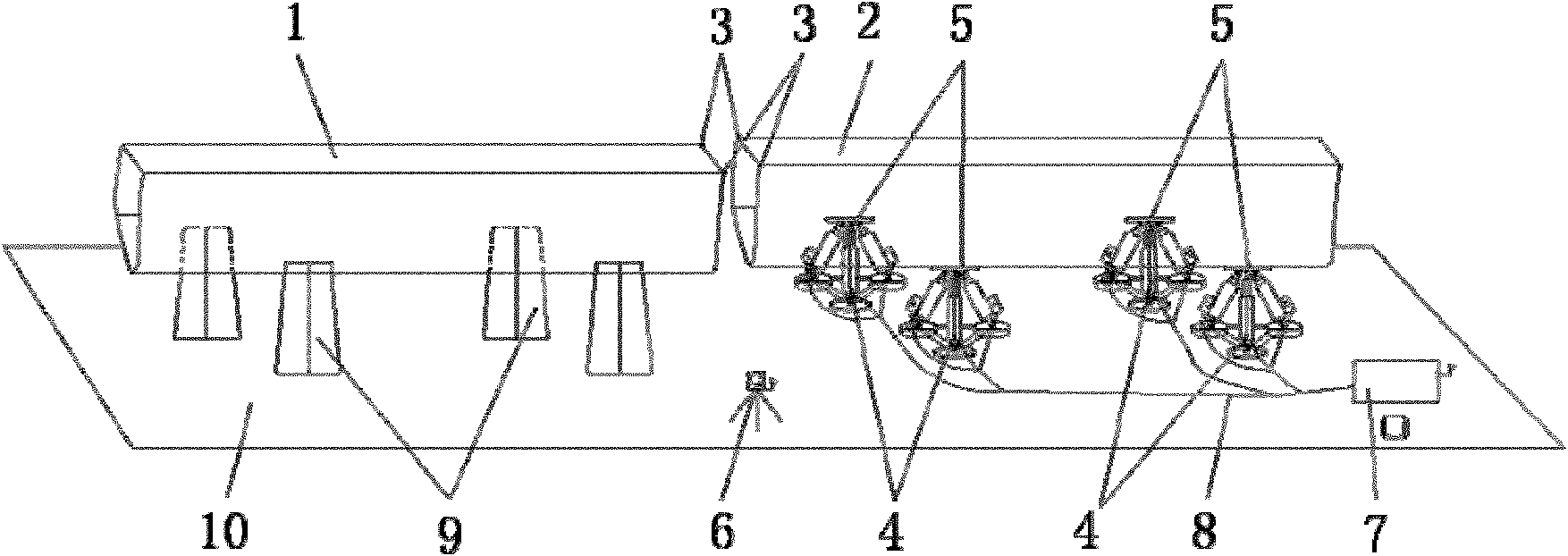

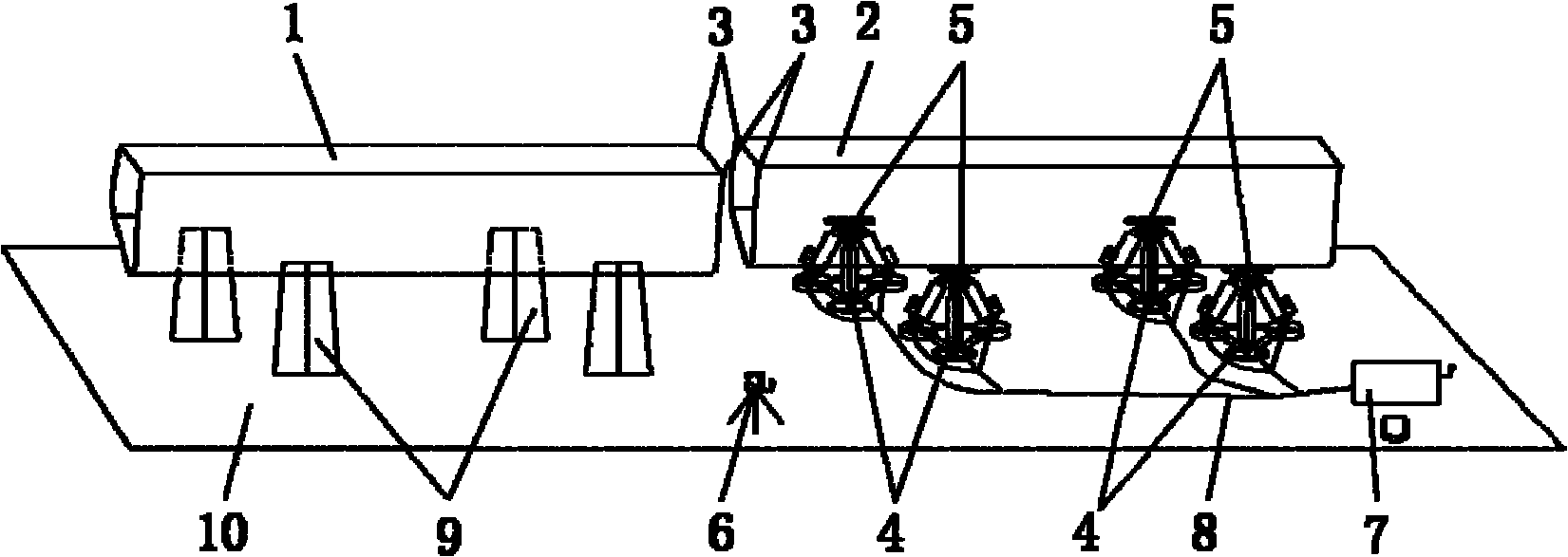

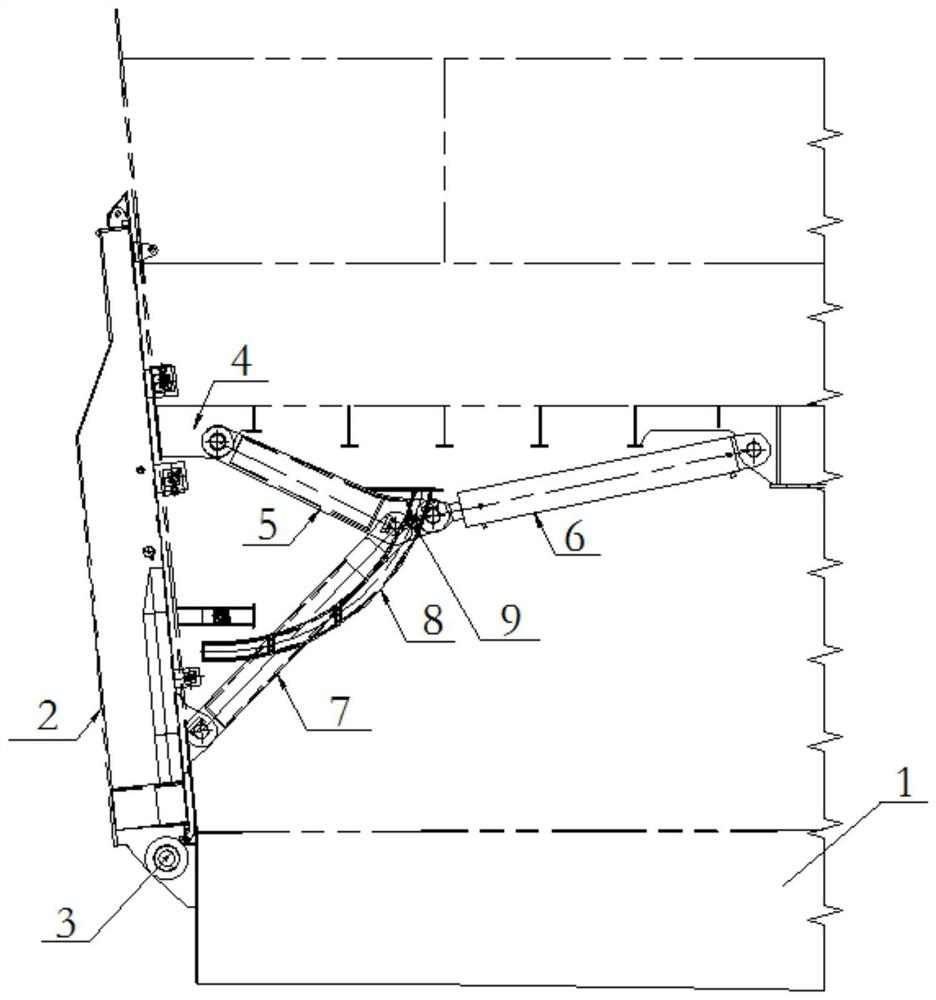

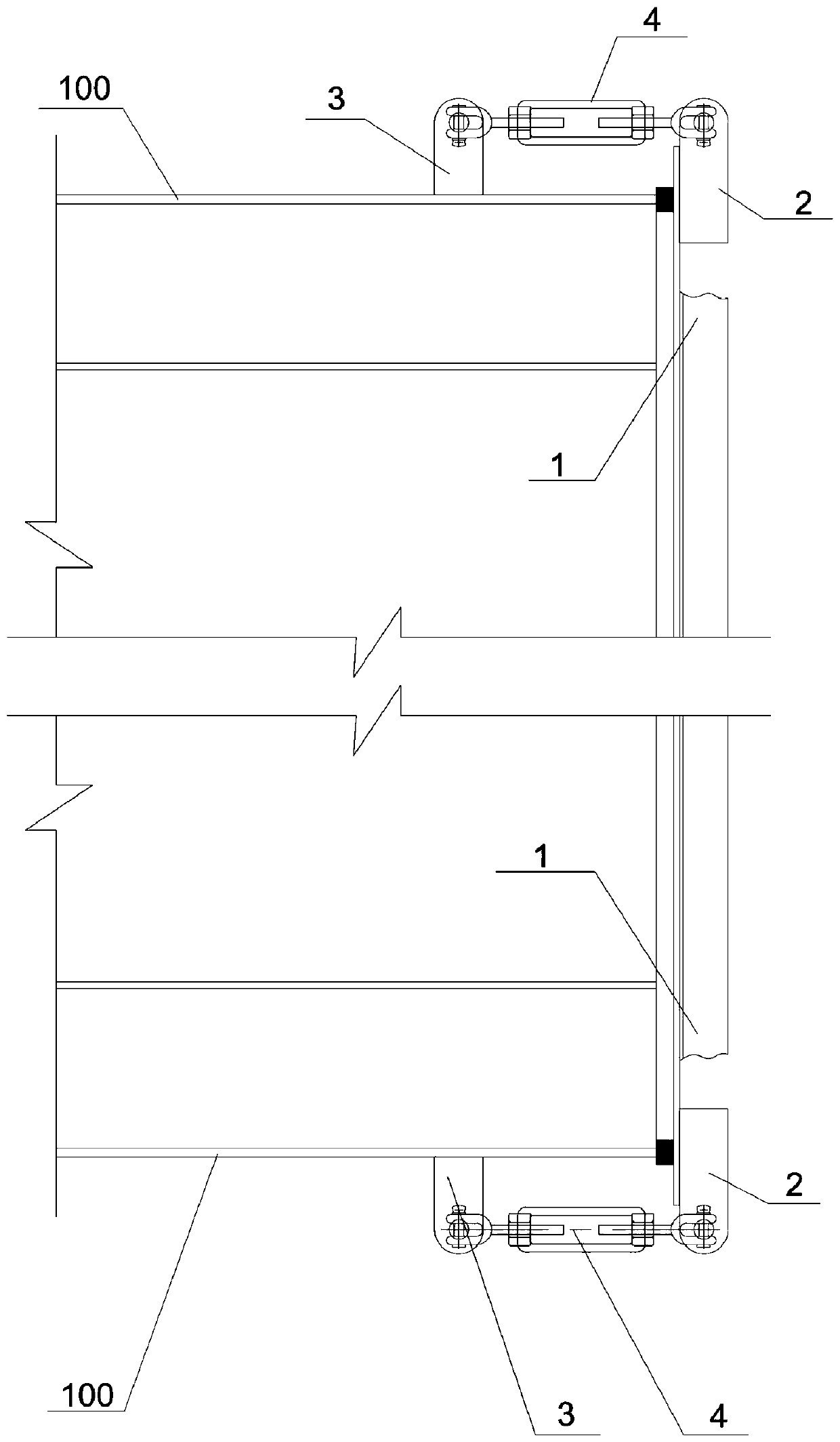

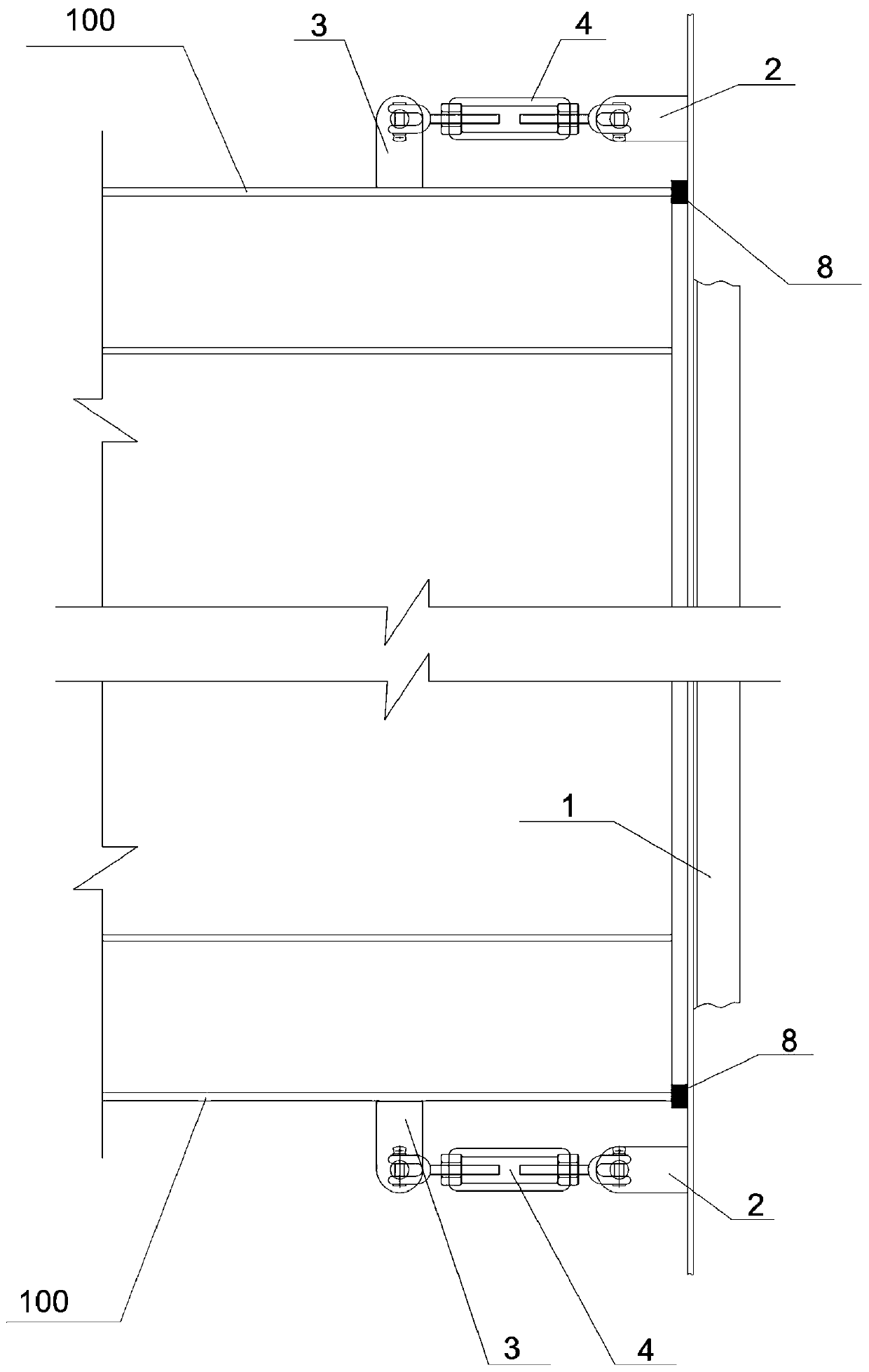

Ship block assembly quick alignment device and method

InactiveCN102091933AQuick releaseImprove build accuracyMetal working apparatusStructural engineeringMechanical engineering

The invention discloses a ship block assembly quick alignment device and a ship block assembly quick alignment method, can be used for adjusting ship block positions and postures in states such as shipway block assembly, general block assembly, shipway assembly and the like, and belongs to the technical field of ship block assembly devices. Aiming at the characteristics of large scale, large tonnage, complicated appearance, low possibility of being moved and accurately aligned and the like of the shipway block assembly, the ship block assembly quick alignment device is designed and developed, and can realize six degree-of-freedom axial shifting and rotating motion of the ship blocks on a universal adjustable platform. The automatic alignment system with accurate alignment function can quickly free cranes, save manpower, improve the quality and efficiency of block folding, and facilitate improving ship building accuracy and shortening construction period.

Owner:DALIAN UNIV OF TECH

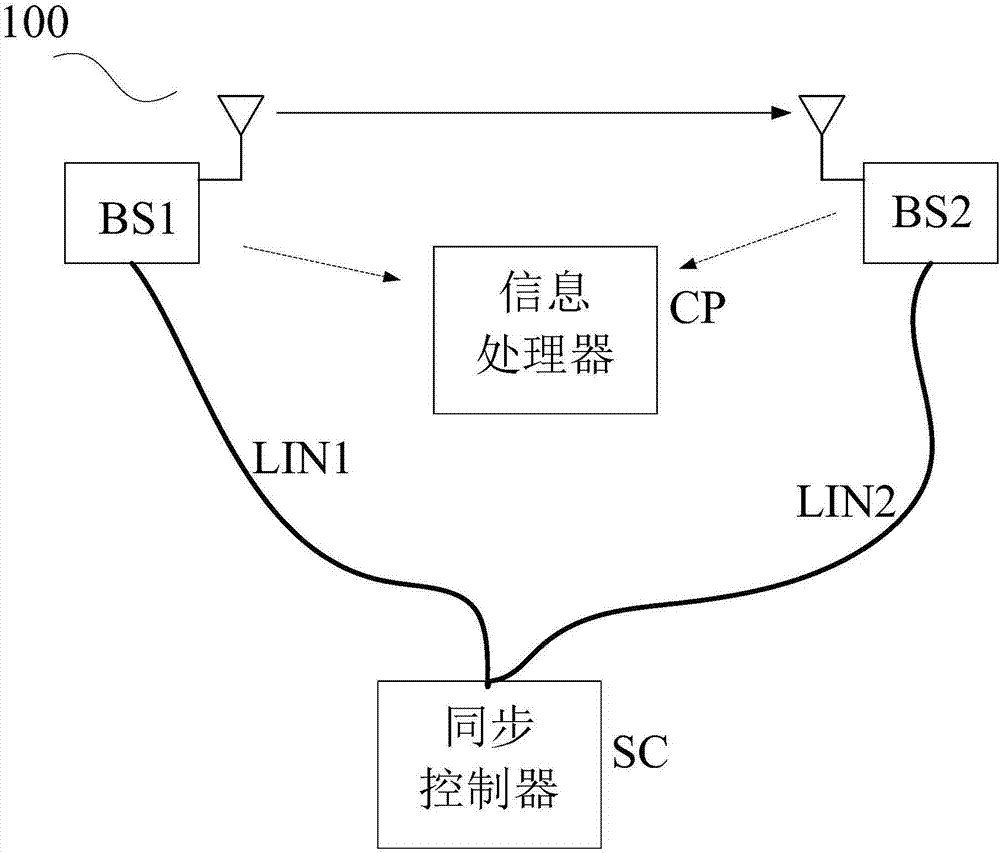

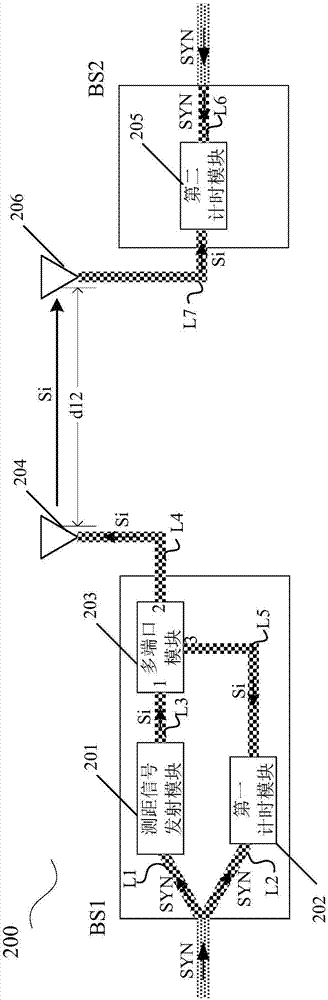

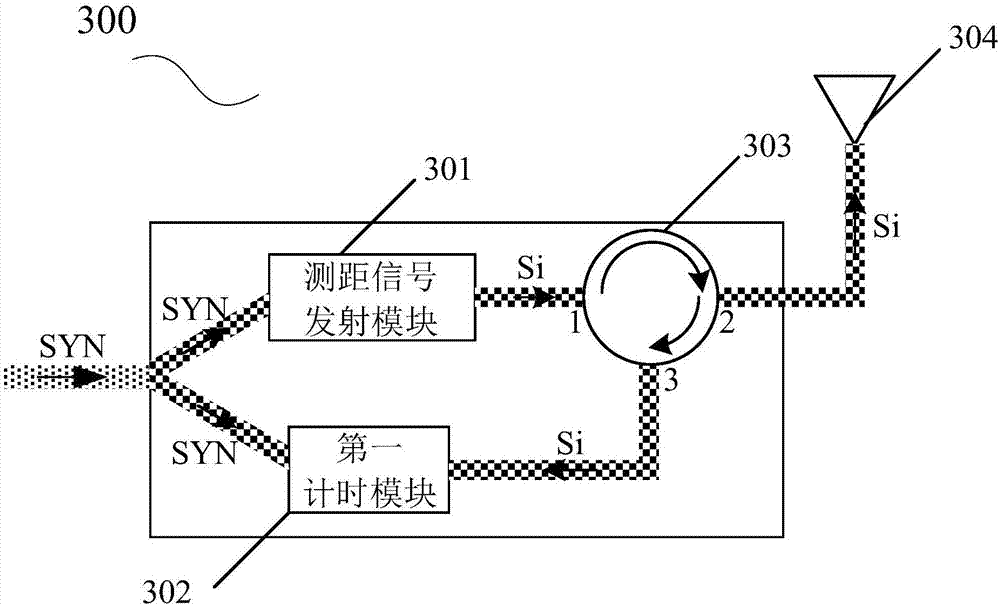

Method of establishing coordinate system between base stations in positioning system

The invention discloses a method, apparatus, device of measuring the distance between base stations, and a positioning system based on the distance measuring method. The method of measuring the distance between base stations includes the steps: utilizing a synchronization signal to trigger a first timing module to start timing and trigger a distance measuring signal emission module to emit a distance measuring signal; utilizing the synchronization signal to trigger a second timing module to start timing; utilizing the distance measuring signal to trigger the first timing module and the second timing module to stop timing; and by means of the interval from the time when the first timing module is triggered by the synchronization signal to start timing to the time when the first timing module is triggered by the distance measuring signal to stop timing, and the interval from the time when the second timing module is triggered to start timing by the synchronization signal to the time when the second timing module is triggered to stop timing by the distance measuring signal, obtaining the distance between the first base station and the second base station. The invention also discloses a method of establishing a coordinate system between base stations in a positioning system. According to the technical scheme of the method of establishing a coordinate system between base stations in a positioning system, the cost of manpower and material resources for measurement can be saved and the positioning accuracy can be improved.

Owner:KUNCHEN TECH CO LTD

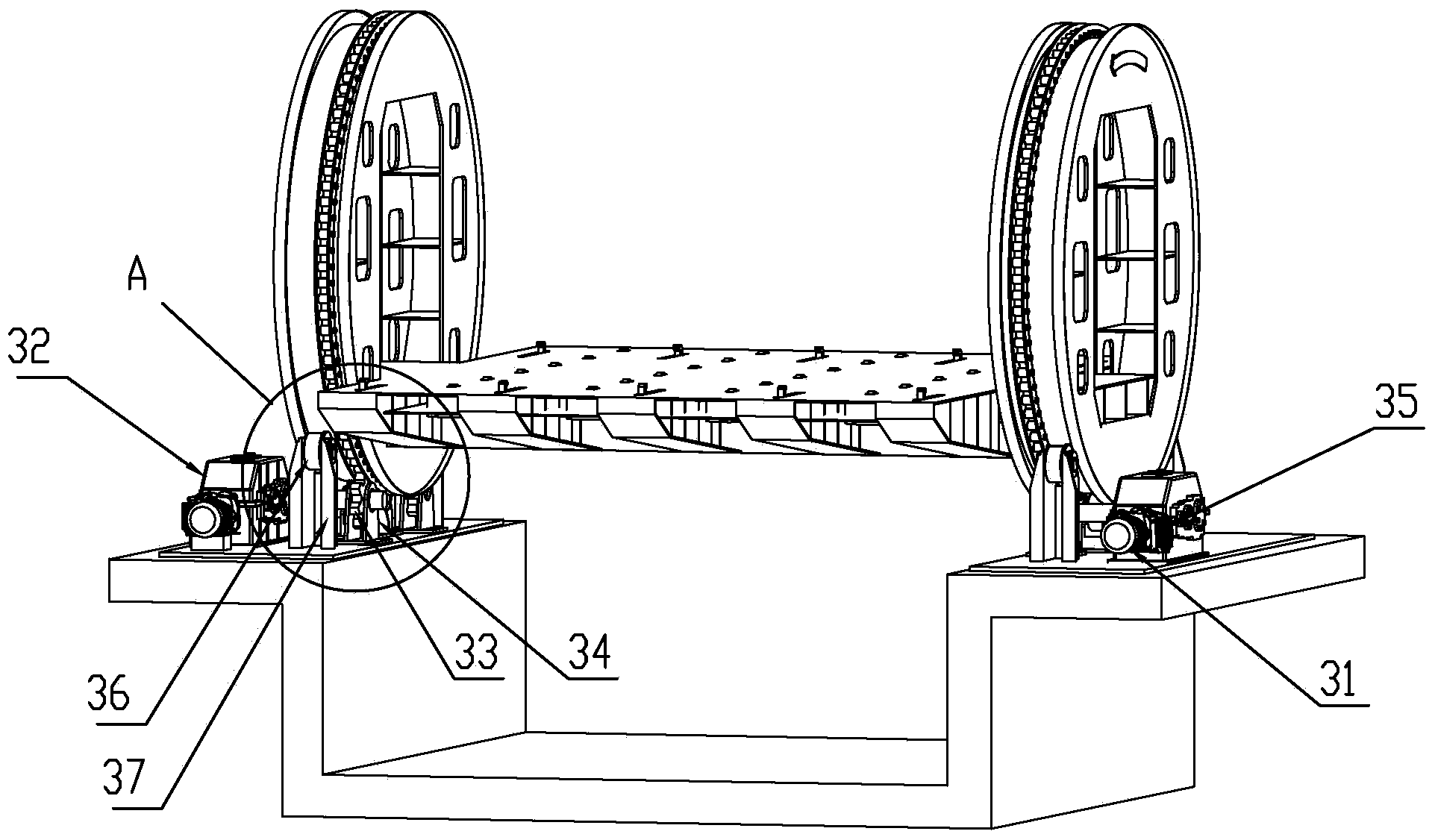

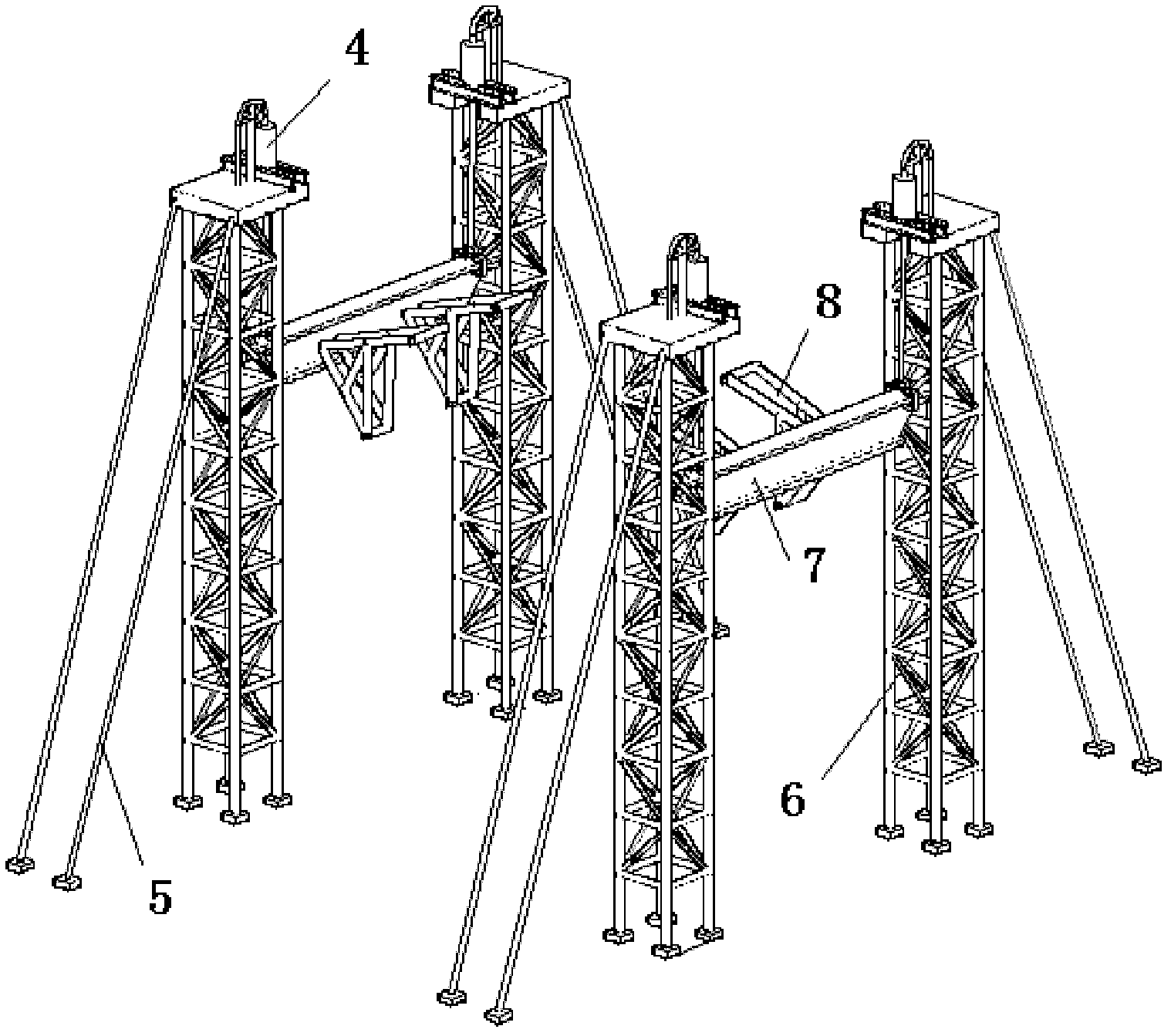

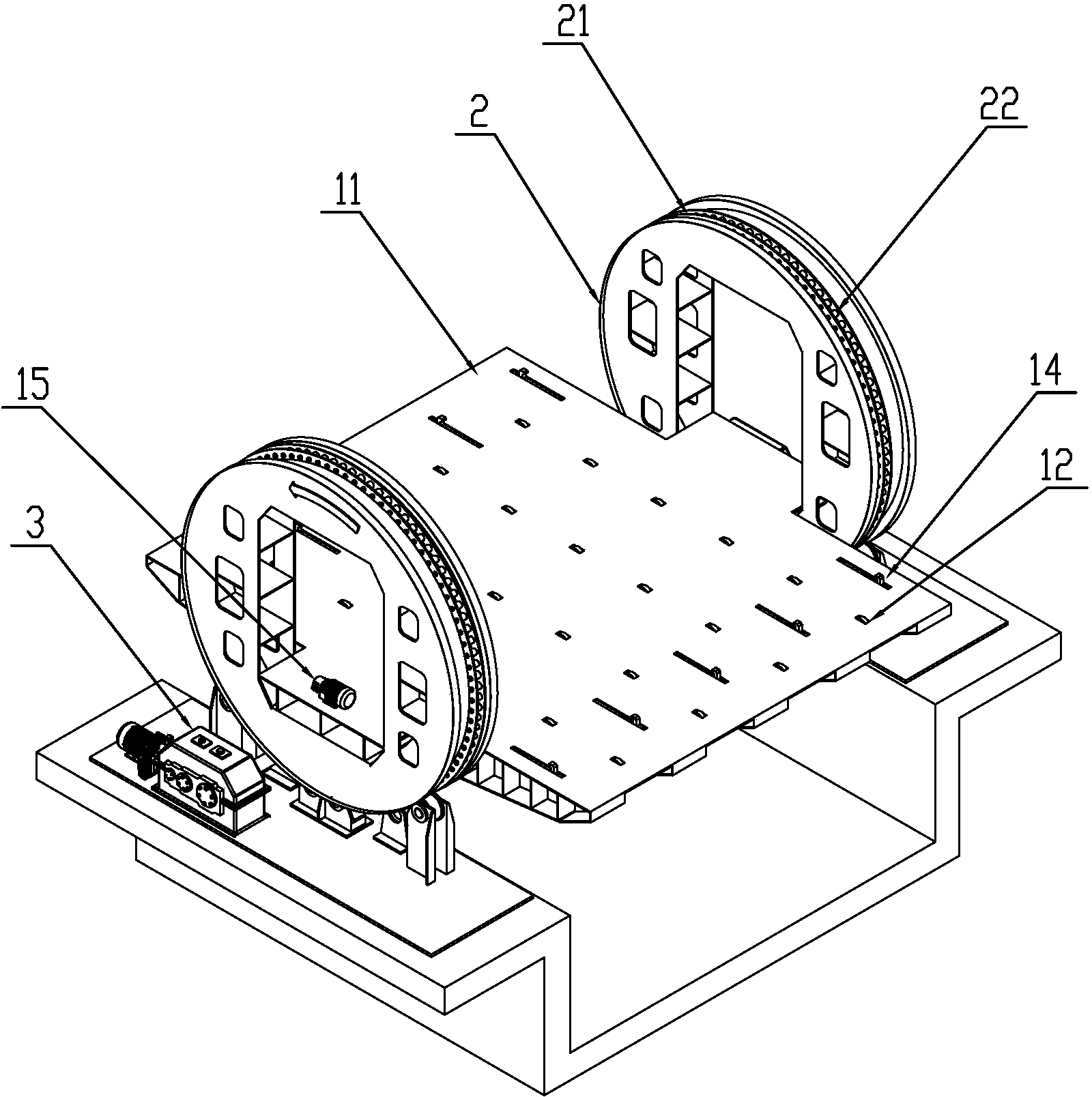

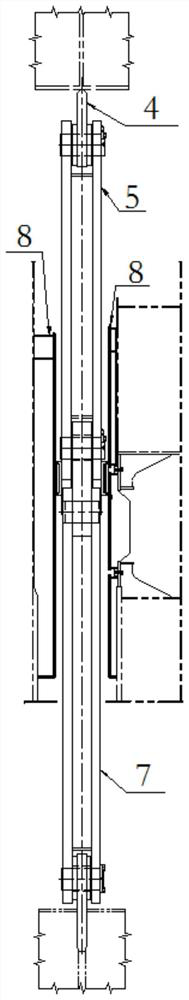

Lift roller based hull block turning equipment during ship construction

ActiveCN103661799AImprove build accuracyReduce secondary transportVessel partsEngineeringMechanical engineering

The invention discloses lift roller based hull block turning equipment during ship construction. The turning equipment comprises a rotary table (11). Two sides of the rotary table (11) are fixed on rotary rings (21) used for overturning respectively. The rotary table (11) comprises an electromagnet adsorption component and a plane attached to a hull block. Each rotary ring (21) rotates together with an outer side driving gear (33). Grooves are formed in the plane, attracted to the hull block, of the rotary table (11) at intervals. Lift roller components (12) are arranged in the grooves. Each lift roller component (12) comprises a track (123) perpendicular to the plane of the rotary table (11). Roller carriers (124) with rollers (121) are arranged in the tracks (123). Lift roller hydraulic oil cylinder components (122) are connected to the lower sides of the roller carriers (124). Rotary shafts of the rollers (121) are connected with roller driving motor components. By the turning equipment, construction cost of the hull block is greatly reduced, and construction efficiency is improved.

Owner:DALIAN SHIPBUILDING IND

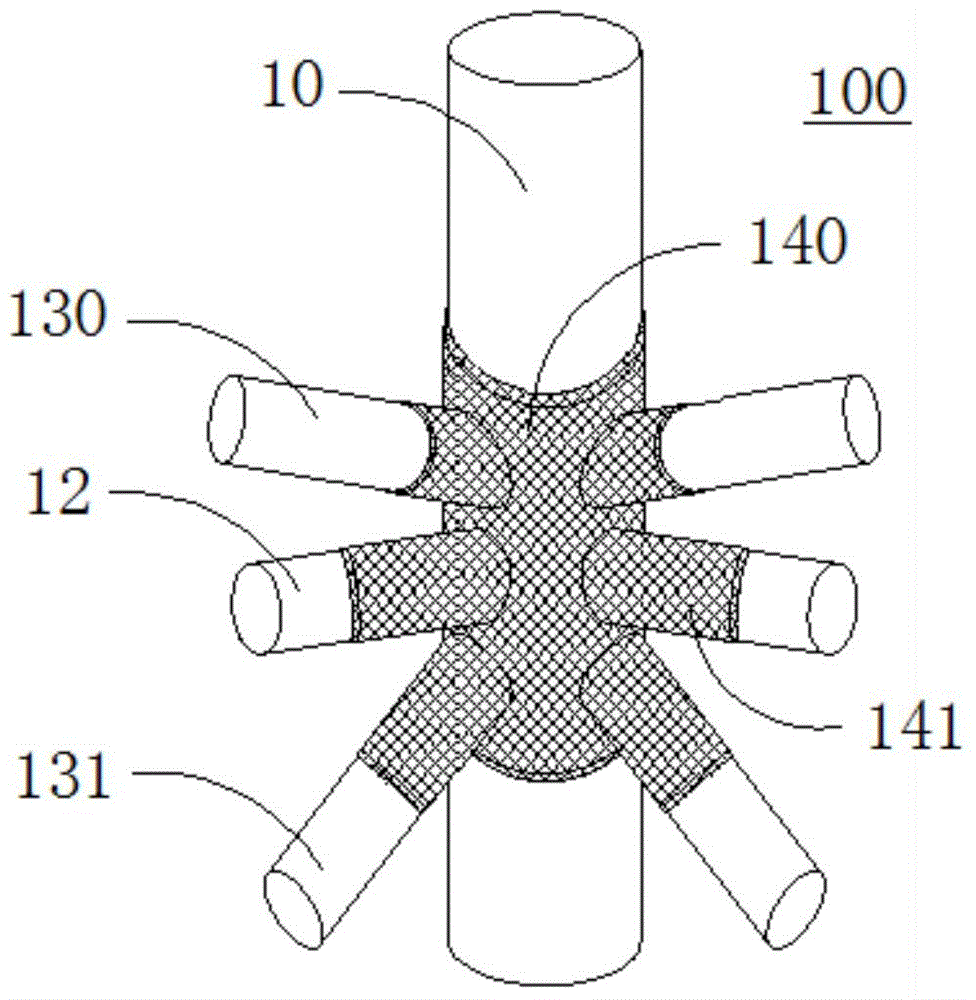

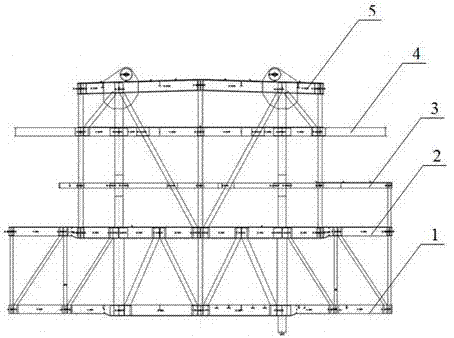

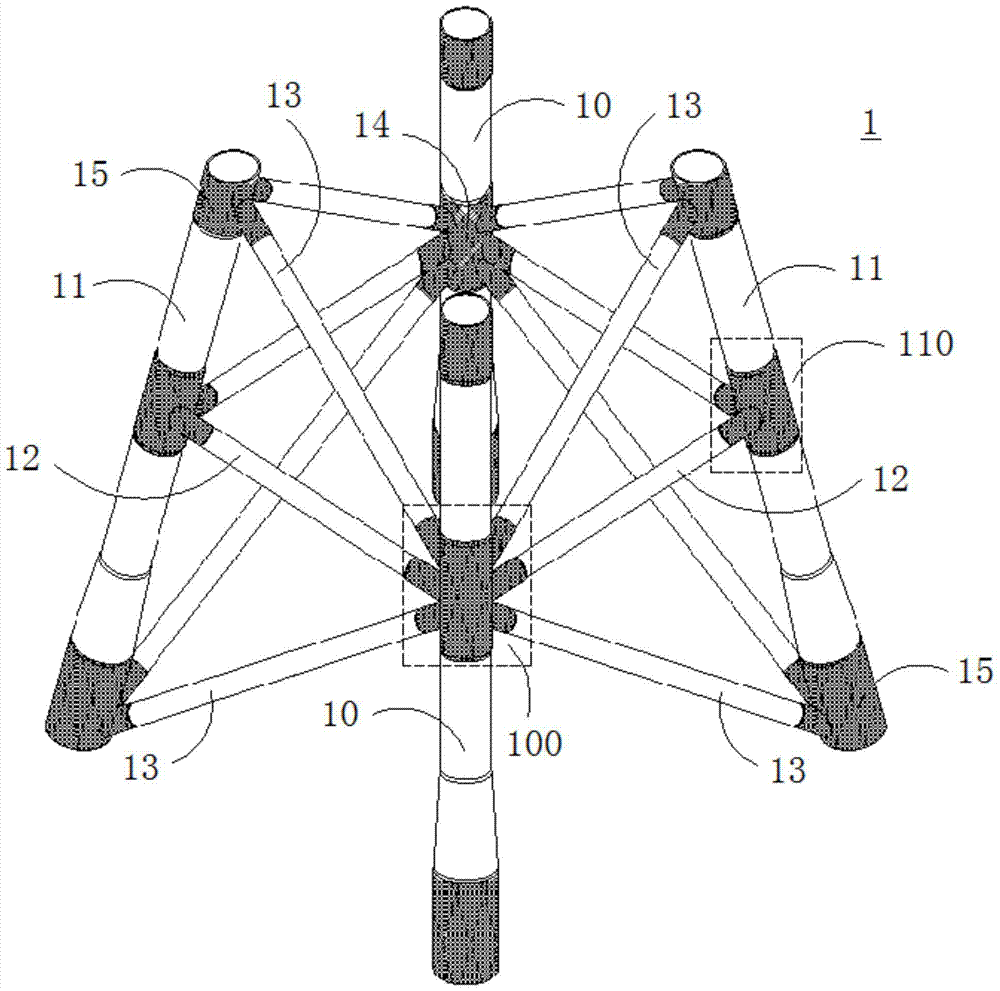

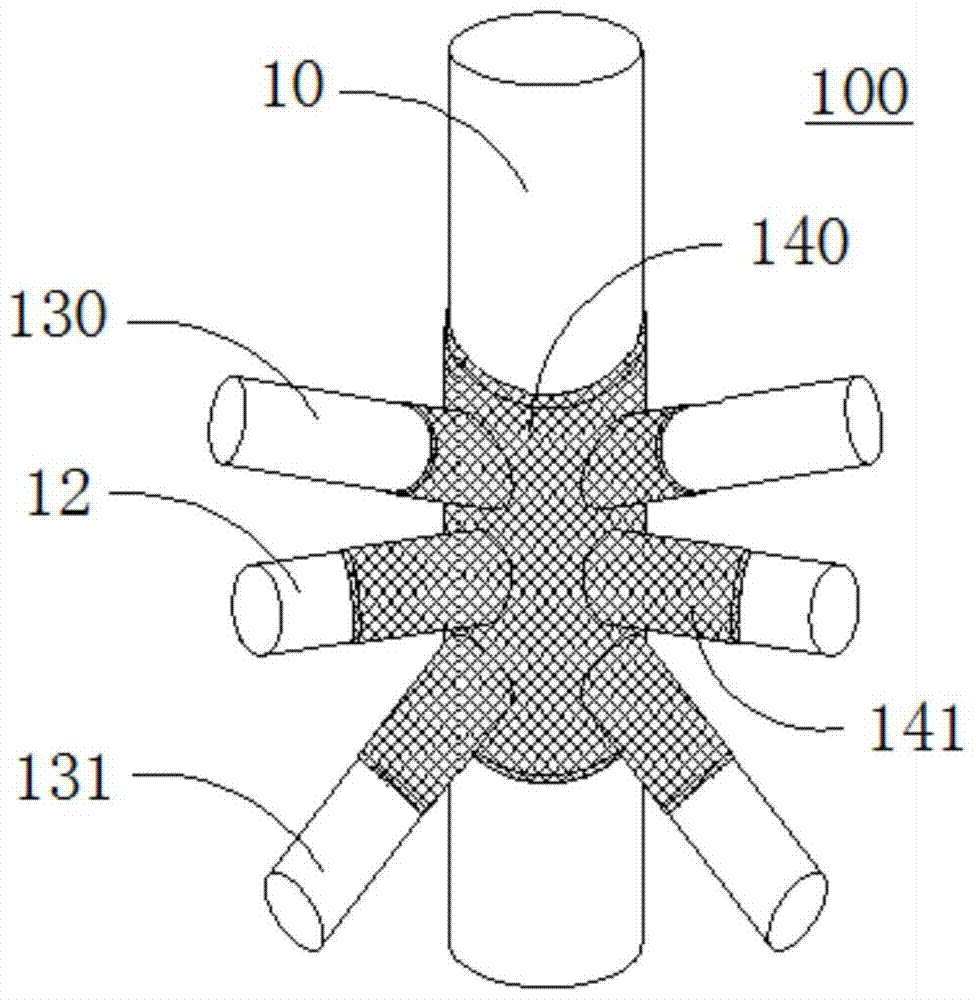

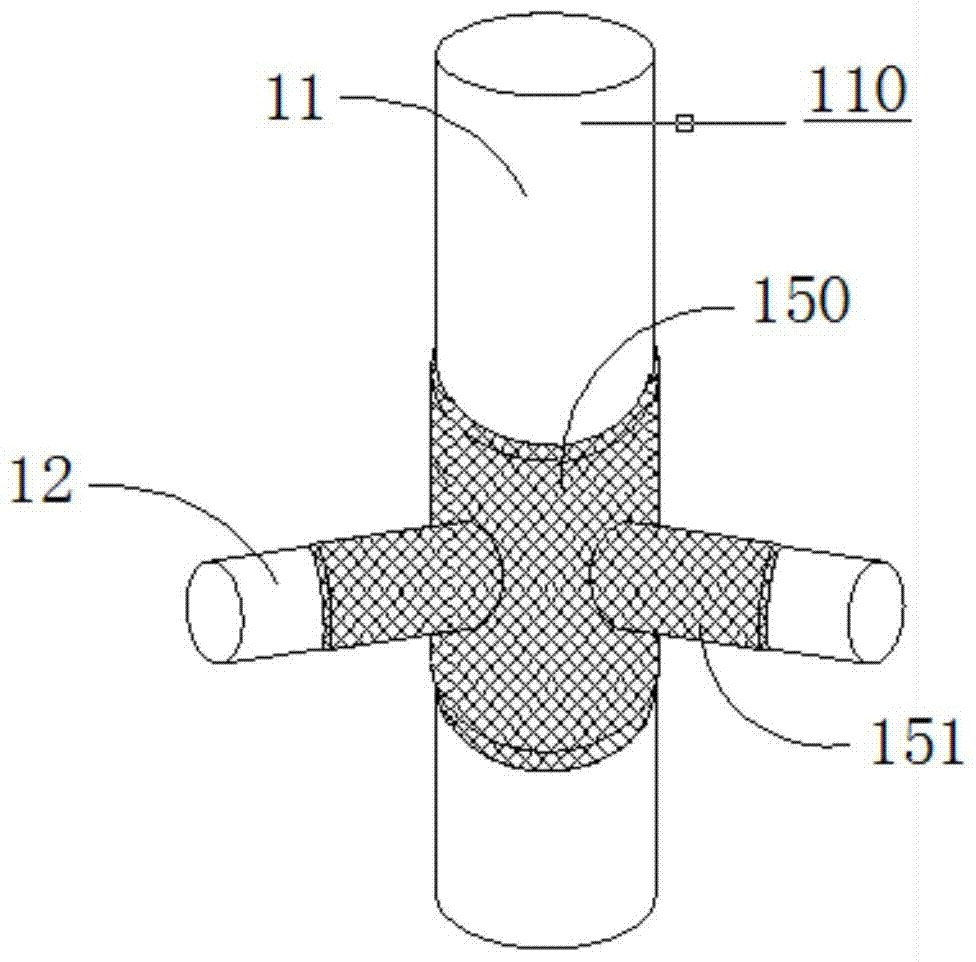

Guide pipe frame, guide pipe frame foundation platform and guide pipe frame construction method

ActiveCN105019419AImprove stabilityImprove fatigue resistanceArtificial islandsUnderwater structuresArchitectural engineeringGuide tube

The invention discloses a guide pipe frame, a guide pipe frame foundation platform and a guide pipe frame construction method. The guide pipe frame comprises at least two main guide pipes and at least two secondary guide pipes, wherein the main guide pipes and the secondary guide pipes are staggered to surround by a lap; the main guide pipes and the secondary guide pipes, close to each other, are connected through middle support rods; multiple inclined support rods are additionally arranged between the main guide pipes and the secondary guide pipes close to each other; and with connecting points of the middle support rods and the main guide pipes as first nodes, the multiple inclined support rods are connected between the main guide pipes and the secondary guide pipes in a sector form with the first nodes as centers. The guide pipe frame, the main guide pipes and the inclined support rods between two secondary guide pipes near the main guide pipes are gathered on the first nodes to facilitate to transfer the load onto the main guide pipes, so that the stability and the fatigue resistance of the guide pipe frame are improved; and as the support rods are not connected in the whole guide pipe frame, and the guide pipes are only connected with the support rods, the numbers of the support rods and the nodes are decreased, the construction is more convenient, the materials are saved, and the construction cost is reduced.

Owner:CHINA ENERGY ENG GRP GUANGDONG ELECTRIC POWER DESIGN INST CO LTD

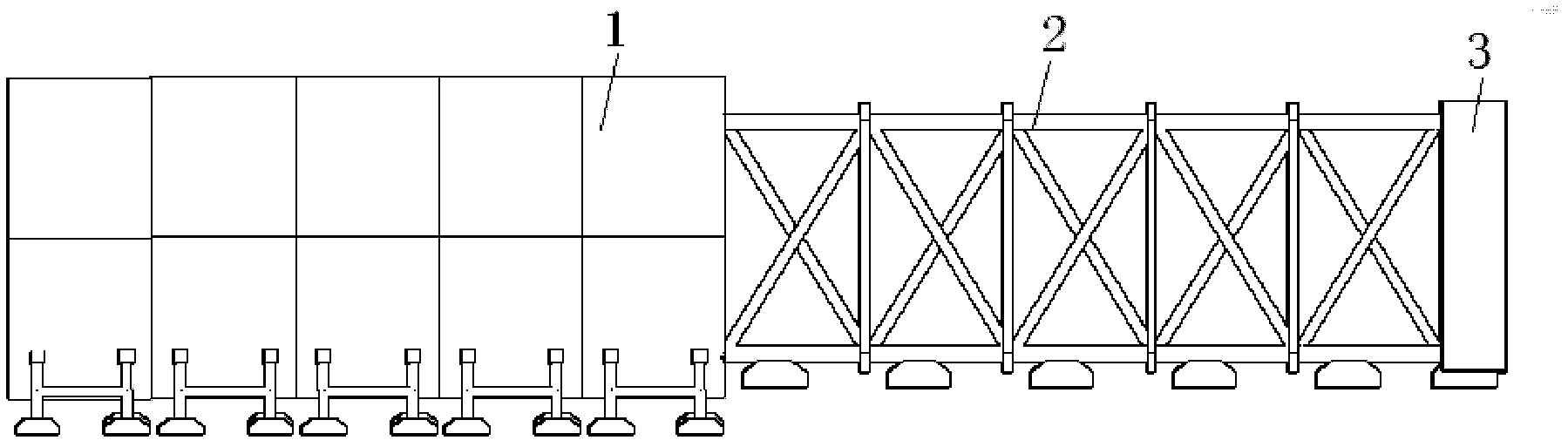

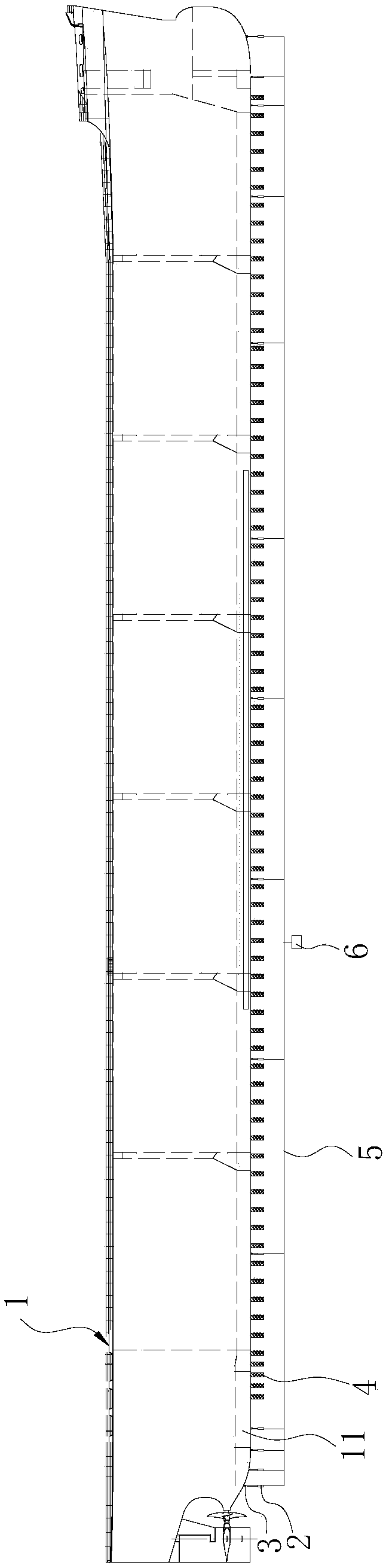

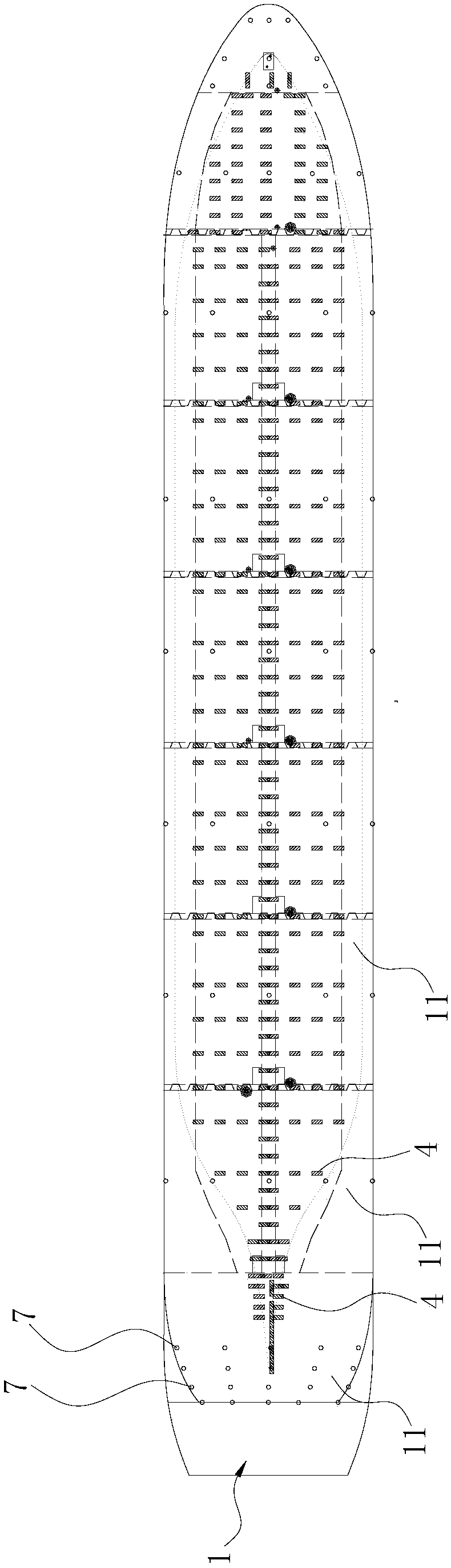

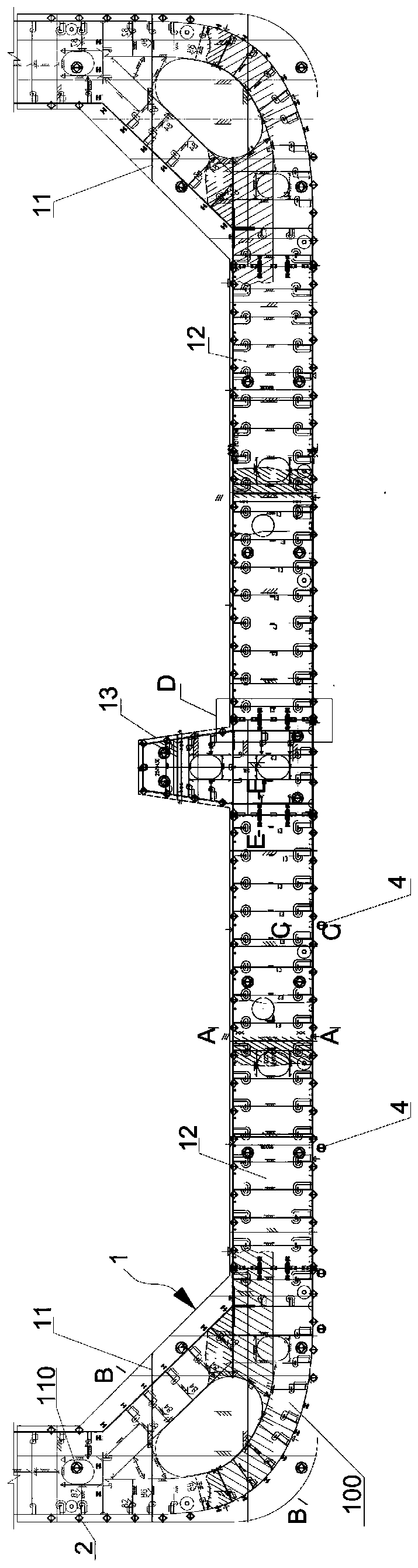

Building process for deep sea spar platform

InactiveCN102582786ARealize constructionAchieve structural closureVessel partsResource developmentArchitectural engineering

A building process for a deep sea spar platform includes the steps: firstly, respectively building an upper hard tank ring half section and a lower hard tank ring half section on a slide way; secondly, mounting lifting devices on the periphery of the upper ring half section; thirdly, continuously lifting the upper hard tank ring half section to a set position; fourthly, folding and butting the lower hard tank ring half section and the upper hard tank ring half section into an integral ring section; fifthly, leading the integral ring section to slide out of a mounting device; sixthly, repeating the step two to the step five until a plurality of integral ring sections are built; seventhly, folding and connecting the integral ring sections into an integral hard tank; eighthly, respectively mounting a truss and a soft tank on slide shoes positioned on sliders; and ninthly, completing building of a spar platform body by means of butting and folding. By the aid of the building process, building precision of the platform is improved, construction period is shortened, a building procedure is little susceptible to environment (wind) load effect, a requirement on site space is lowered, and important technical support is provided for deep-sea resource development.

Owner:CHINA NAT OFFSHORE OIL CORP +2

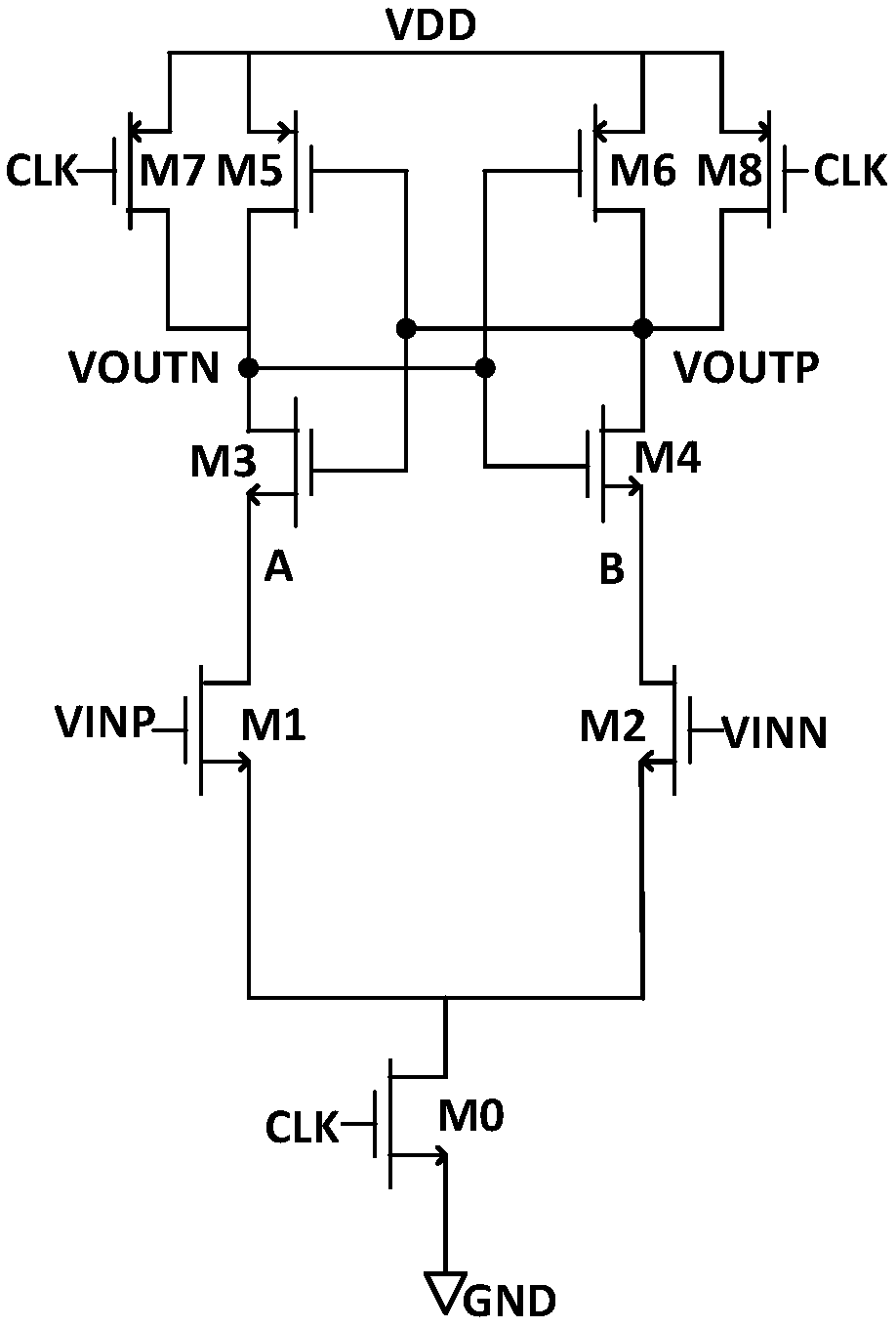

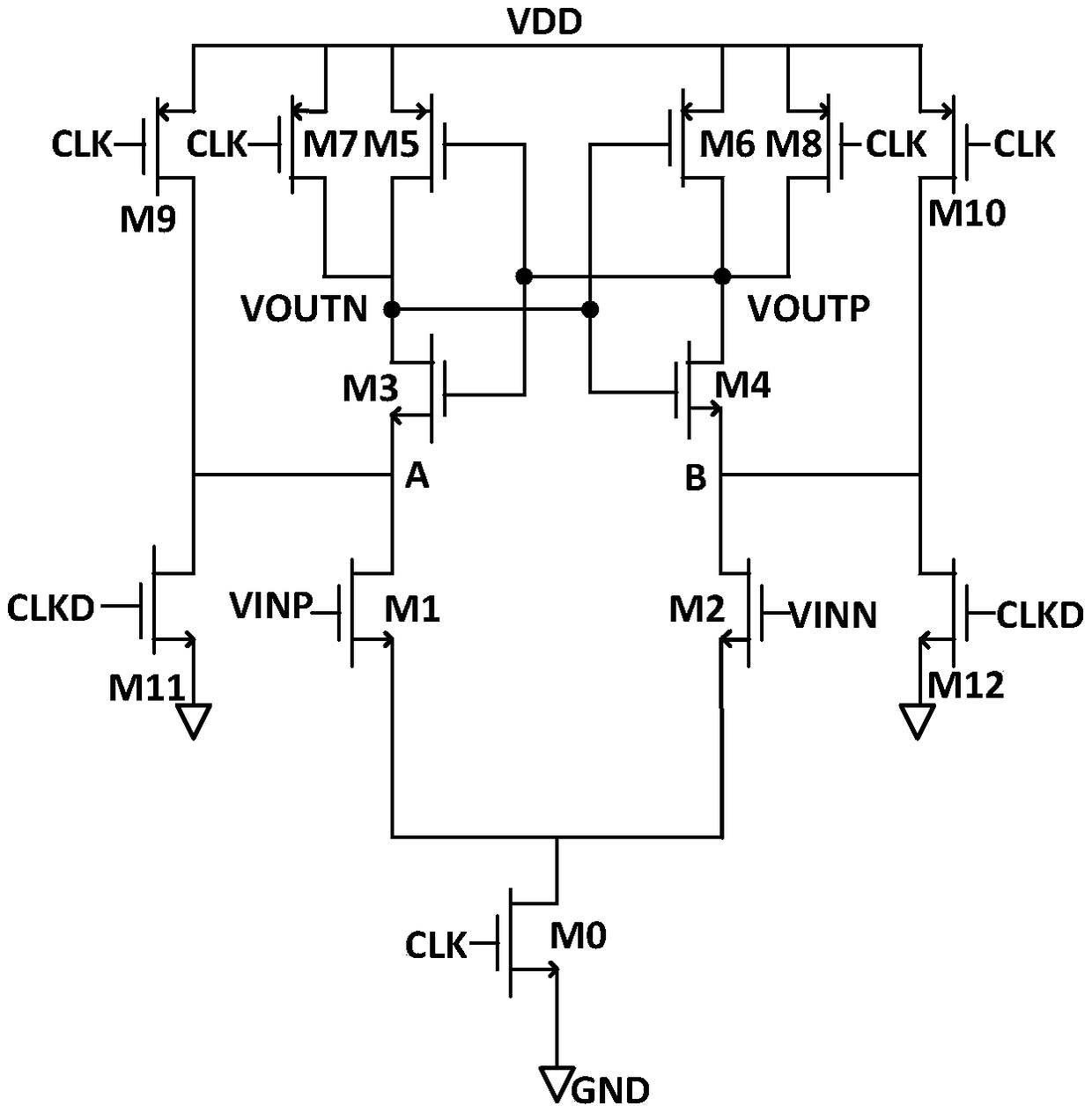

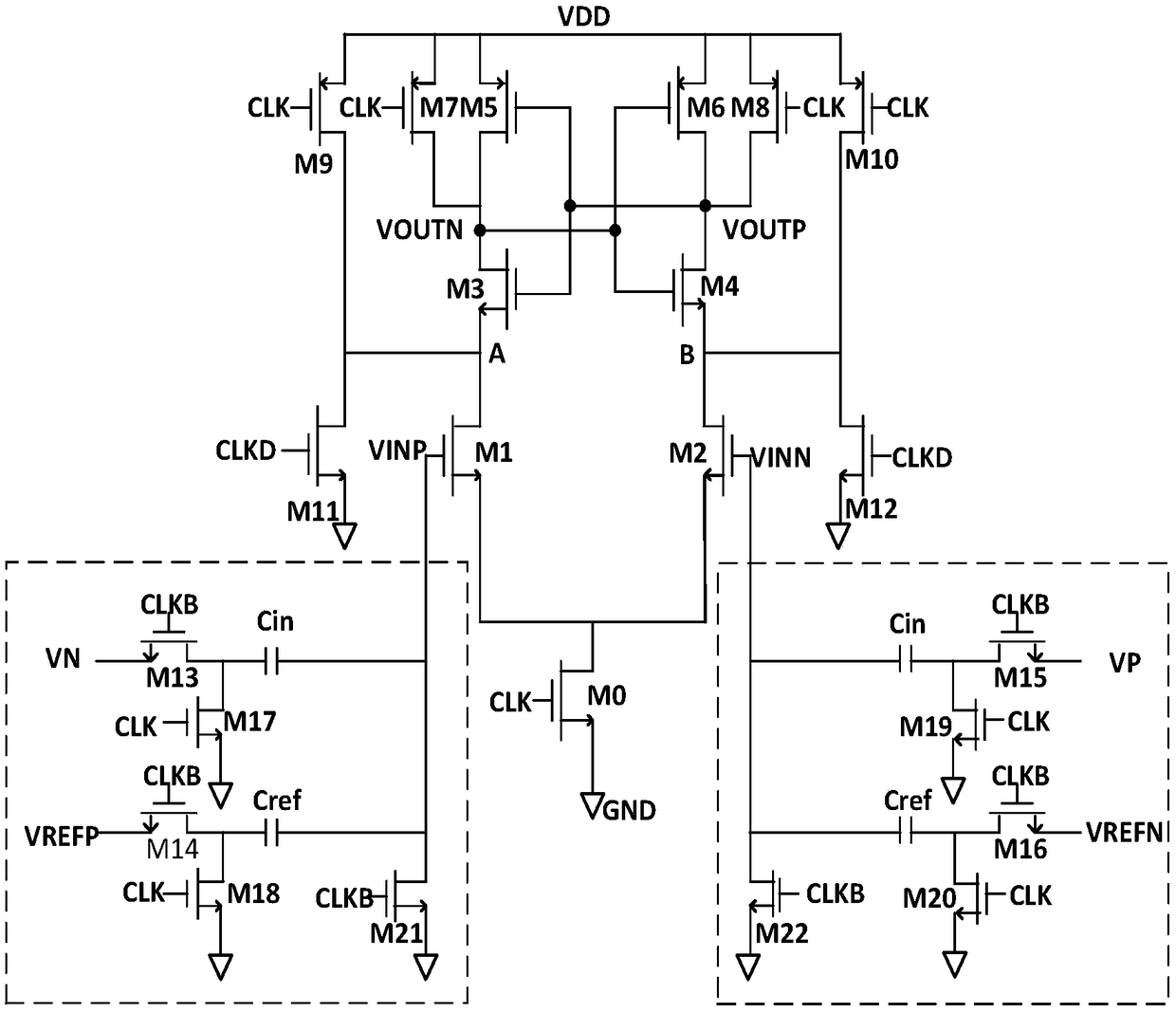

Latch circuit

InactiveCN108667447AReduce bit error rateReduce the impact of mismatch on comparison accuracyReliability increasing modificationsAnalogue-digital convertersAudio power amplifierEngineering

The invention relates to a latch circuit. The latch circuit comprises a preamplifier, a comparison latch body, a first pair of reset tubes, a second pair of reset tubes, and a pair of switch tubes, wherein the preamplifier amplifies an input differential signal, the comparison latch body is connected with the preamplifier and performs compared latch on the amplified differential signal, the firstpair of reset tubes are connected with an output of the comparison latch body and a power supply, the second pair of reset tubes are connected with a drain of an input pair tube of the preamplifier and a power supply, the drain of the input pair tube of the preamplifier is grounded through the pair of switch tubes, gates of the two pairs of reset tubes receive a clock signal, a gate of the pair ofswitch tubes receives a delayed clock signal of the clock signal, the two pairs of reset tubes are used for enabling the comparison latch body to work in a linear area when the clock signal changes from low to high, and the pair of switch tubes helps reduce one tube for the ground path of the comparison latch body in work. The impact of circuit mismatch on comparison accuracy is lowered, the working time of a comparator is reduced, and the bit error rate in design of an analog-to-digital converter caused by the latch comparator is lowered.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Construction process for lifting leg pile of offshore living platform

The invention relates to a construction process for a lifting leg pile of an offshore living platform. The construction process is characterized by comprising the following steps of joint pipe manufacturing, unit section butt joint, segment butt joint, T-shaped frame assembly and welding, external web plate assembly and welding, pile leg cylinder curved surface hole making and sealing, sand blasting coating and pile insertion assembly. According to the construction process, each pile leg segment is of a cylinder structure, a plurality of cylinder segments are spliced and assembled into a segment, the construction efficiency is improved, and the construction cost is reduced; vertical reinforcing ribs and T-shaped reinforcing rings play the roles of longitudinal and transverse fixing and reinforcing, structural pipes play the role of transverse reinforcing in cylinders, and the strength of a pile leg structure is ensured; and the construction accuracy of a rack plate is improved by restricting the main indexes such as straightness, tooth spacing and common normal spacing of the rack plate, so that the support and stability of the pile leg are improved, and welding deformation or weldcracking is avoided.

Owner:NANTONG BLUE ISLAND OFFSHORE CO LTD

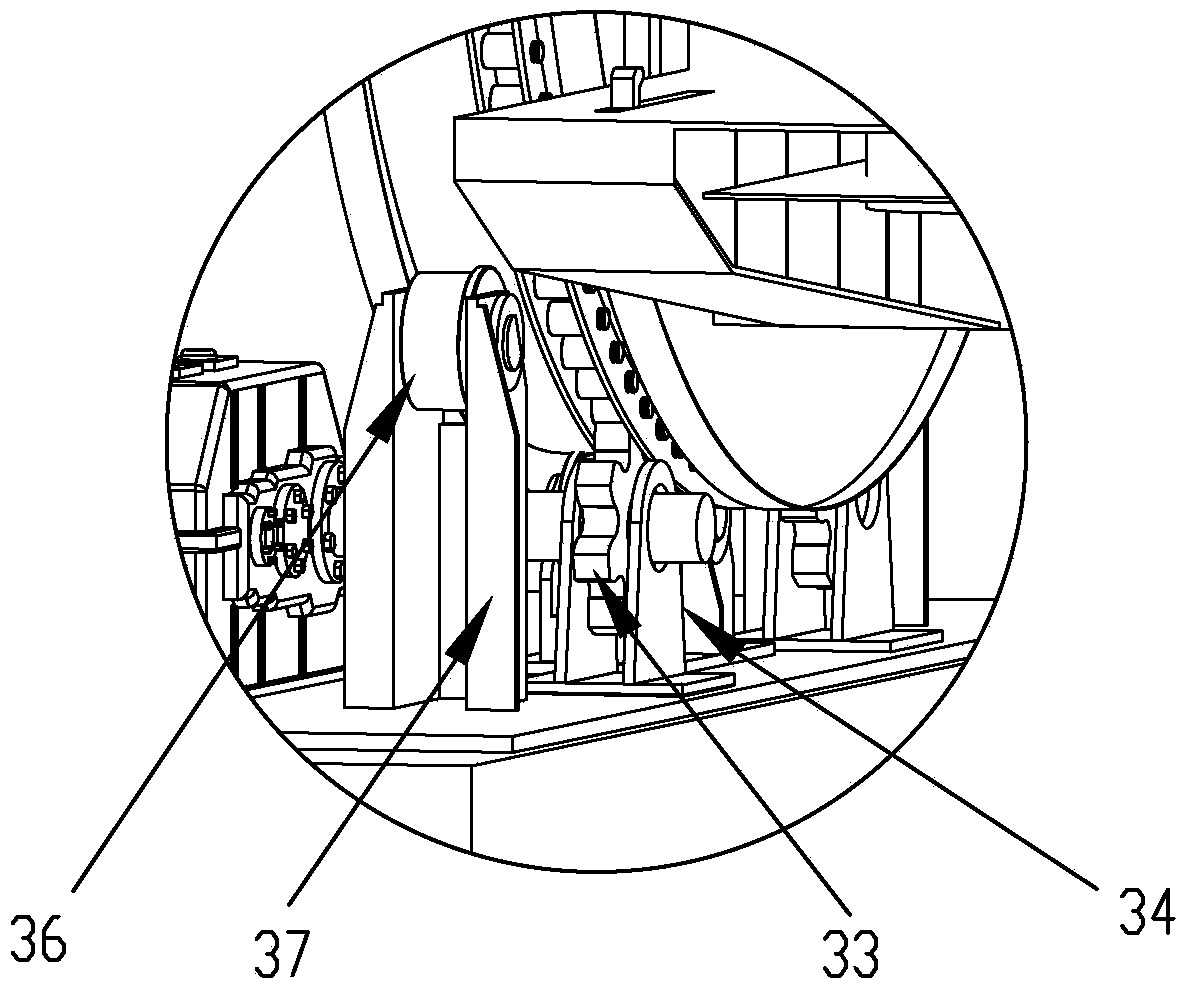

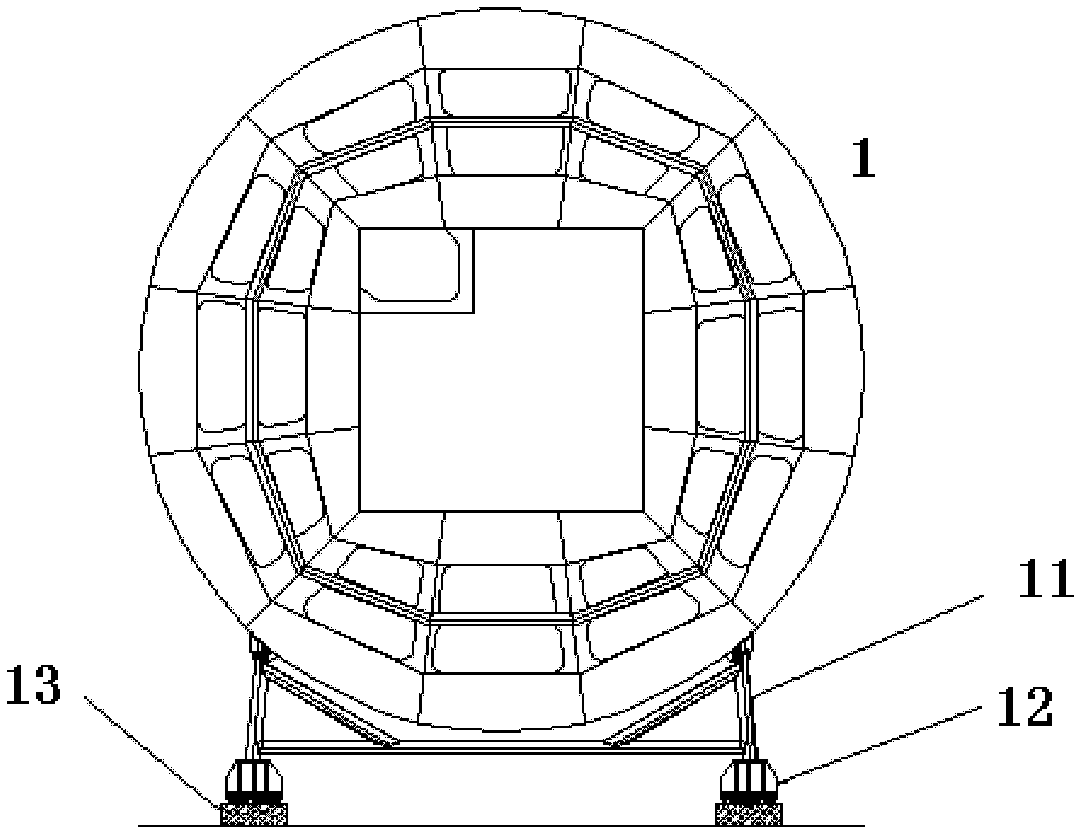

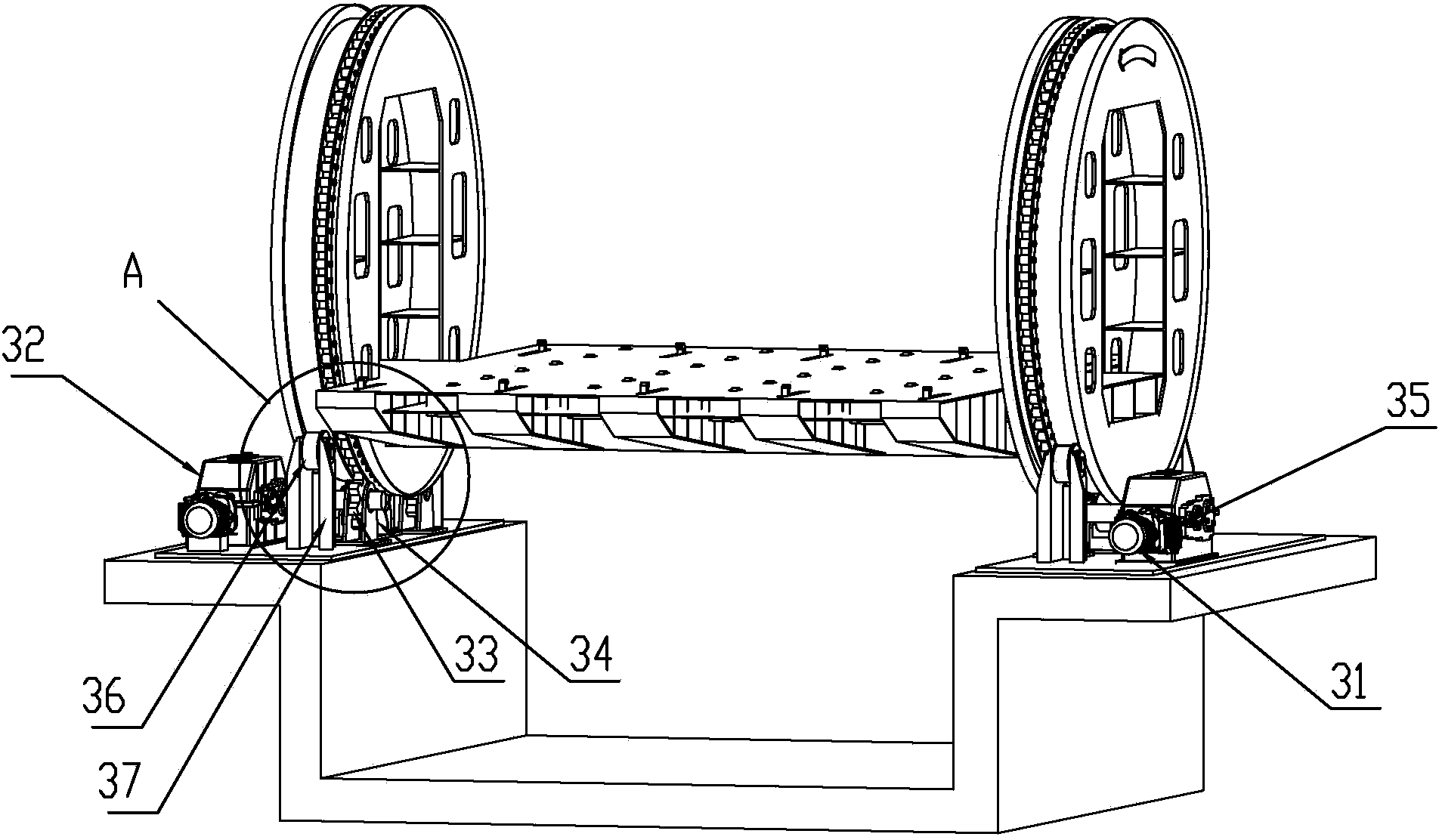

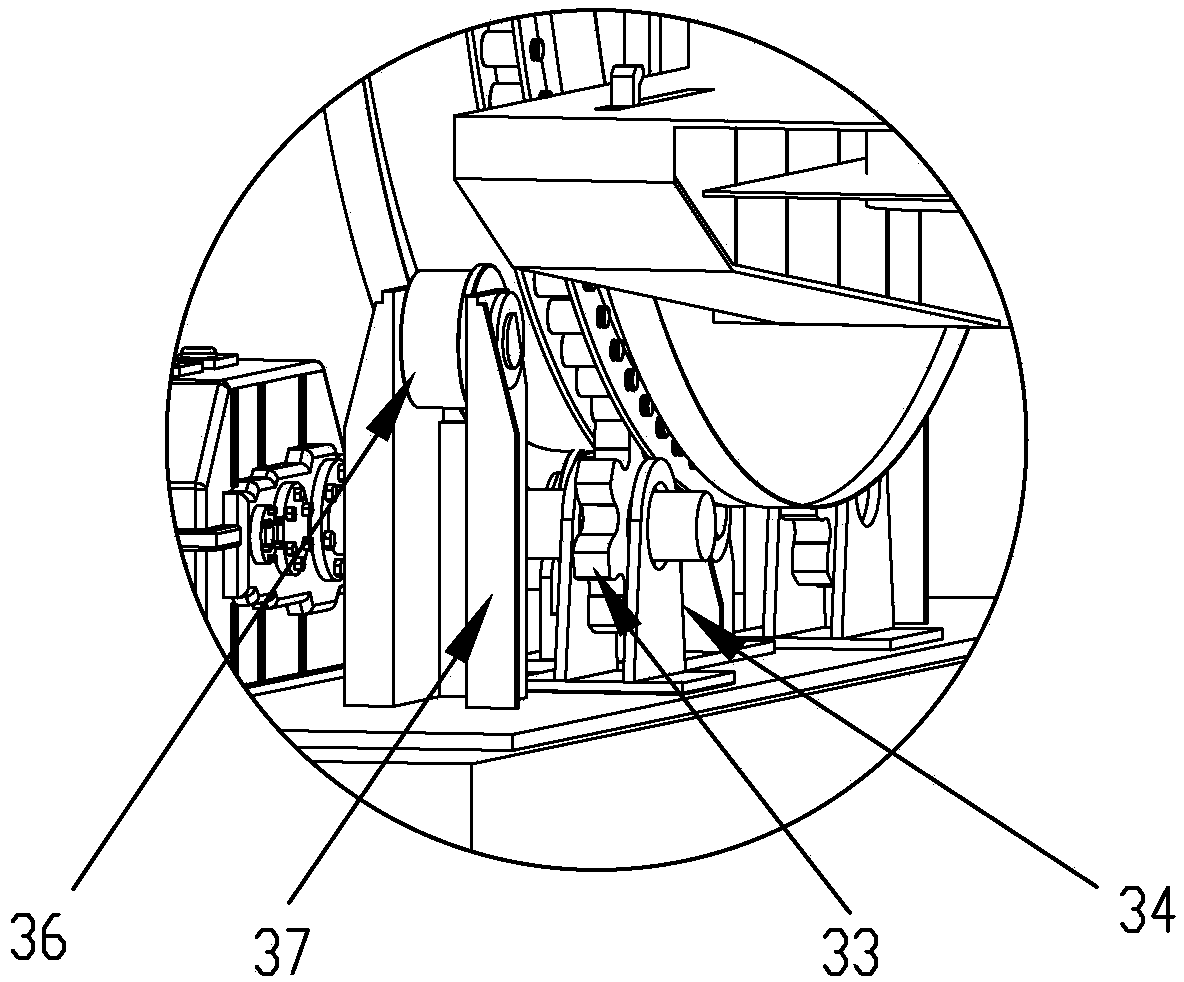

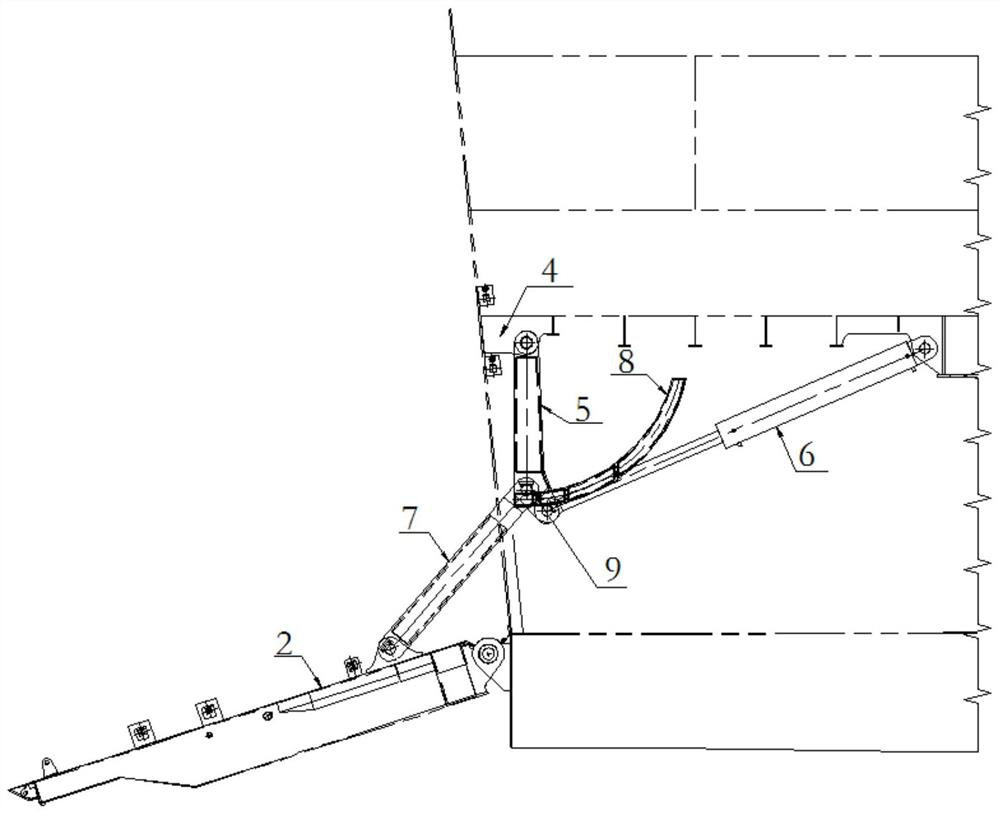

Hull block turning equipment provided with clamping and protecting mechanisms during ship construction

ActiveCN103661800AImprove build accuracyReduce secondary transportVessel partsEngineeringMechanical engineering

The invention discloses hull block turning equipment provided with clamping and protecting mechanisms during ship construction. The hull block turning equipment comprises a rotary table (11). Two sides of the rotary table (11) are fixed on rotary rings (21) used for overturning respectively. The rotary table (11) comprises an electromagnet adsorption component and a plane attached to a hull block. Each rotary ring (21) rotates together with an outer side driving gear (33). Wide slots are formed at the edge, contacting with the hull block, of the rotary table (11). Movable clamping components are arranged in the wide slots. Each movable clamping component comprises a track frame component which is perpendicular to the plane of the rotary platform and moves outwards parallelly to the plane of the rotary platform. Clamping claws are arranged in the track frame components. Each clamping claw is provided with a hydraulic component for moving the claws in two directions. By the hull block turning equipment, construction cost is greatly reduced, and construction efficiency is improved.

Owner:DALIAN SHIPBUILDING IND

Building process of upper assembly of maritime booster station

ActiveCN107401153AImprove construction efficiencyImprove build accuracyArtificial islandsTransformer housesSteel structuresBuilding process

The invention discloses a building process of an upper assembly of a maritime booster station. The building process comprises the following steps that (1) all layers of deck pieces are prefabricated and hoisted; (2) preparation is conducted before the deck pieces are hoisted; (3) the bottom deck pieces and related devices are hoisted; (4) the second layer of deck pieces and related devices are hoisted; (5) the third layer of deck pieces and related devices are hoisted; (6) the fourth layer of deck pieces are hoisted; and (7) the fifth layer of deck pieces are hoisted. When the upper assembly is built, all layers of deck pieces and segments of a steel structure building are hoisted from bottom to top and from inside to outside, land construction of the upper assembly adopts the method of segment prefabrication and integral hoisting, the land prefabrication depth is increased as much as possible, and the aerial working amount is reduced; and meanwhile, the related devices on the deck pieces are installed in place after the deck pieces are hoisted, the maritime tooling quantity is reduced, trouble caused by transportation is also omitted, the steps of the whole building process of the upper assembly are orderly, and the building efficiency and precision are greatly improved.

Owner:NANTONG BLUE ISLAND OFFSHORE CO LTD

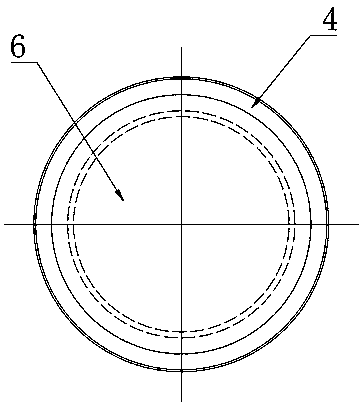

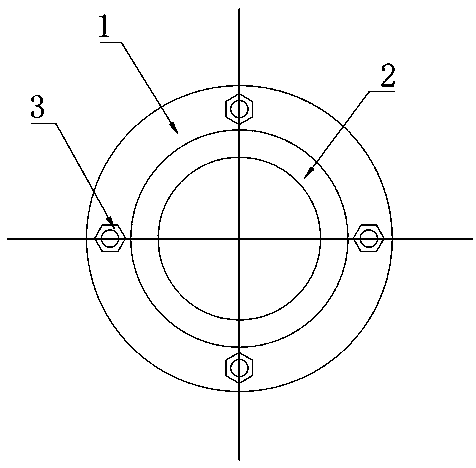

Method for installing liquid cargo pump base of duplex stainless steel chemical tank

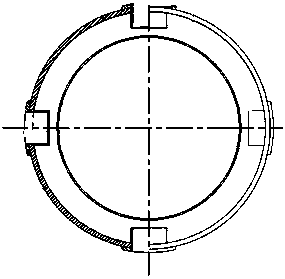

ActiveCN109606563AImprove build accuracyHigh positioning accuracyVessel designingFor bulk goodsOil wellChemical tank

The invention, which belongs to the technical field of ship construction, discloses a method for installing a liquid cargo pump base of a duplex stainless steel chemical tank. The method comprises thefollowing steps: step one, making a deck opening positioning mechanism including a first opening template and a second opening template that are circular-ring-shaped plate structures with the thicknesses of 6mm; step two, determining the center of a deck opening on the deck; step three, placing the deck opening positioning mechanism on the deck; step four, carrying out opening on the deck by using a cutting machine; step five, installing a liquid cargo pump base, hoisting the liquid cargo pump base at the deck opening, enabling indication laser of a laser plumb aligner to pass through the central point of a liquid cargo cabin bottom suction well; step six, locating and welding the deck and the liquid cargo pump base; and step seven, welding and fixing the deck and the liquid cargo pump base. With the method disclosed by the invention, a problem that the liquid cargo pump base cannot be located, welded and fixed accurately is solved.

Owner:HUDONG ZHONGHUA SHIPBUILDINGGROUP

Method for monitoring structural deformation in ship construction process

InactiveCN108528630AImprove build accuracyEnsure safetyVessel designingStructural deformationWelding residual stress

The invention discloses a method for monitoring structural deformation in a ship construction process. A bottom section located at the bottom of a ship is provided, multiple monitoring devices for monitoring deformation are installed before the bottom section is assembled with other sections of the ship, and the monitoring devices are distributed at the bottom of the bottom section according to adesign line of the ship. By installing the monitoring devices before the bottom section of the ship is assembled with other sections of the ship, deformation conditions of the bottom section in the assembly process can be monitored in time so that measures can be taken in time to prevent continuously aggravated deformation, the construction accuracy of the ship is improved, welding residual stressis reduced, and the safety of the ship after operation is ensured.

Owner:GUANGZHOU SHIPYARD INTERNATIONAL LTD

High-precision positioning and mounting method for ship stern ramp

ActiveCN113184131ARapid positioningShorten the installation cycleWaterborne vesselsHull structureStructural engineering

The invention discloses a high-precision positioning and mounting method for a ship stern ramp. The method comprises the following steps: step 1, hanging a stern door and a stern ramp to mounting point positions of a stern transom plate of a ship body; step 2, determining the mounting position of a main hinge according to the mounting position of the stern ramp, and determining the mounting position of a swing arm hinge eye plate; step 3, lifting away the stern door and the stern ramp, and installing a positioning measurement tool, wherein the positioning measurement tool comprises a swing rod, a fixing mechanism and a scribing mechanism, one end of the swing rod is connected with the fixing mechanism, and the other end is connected with the scribing mechanism; step 4, rotating the swing rod with the shaft hole as the center, and drawing mounting lines on a hull structure on the two sides in the door frame wall through the scribing mechanism; step 5, calculating the thickness cutting allowance of a swing arm track, and performing allowance cutting on a swing arm guide track; and step 6, positioning and welding the swing arm track according to a mounting line on the hull structure. The mounting position of the swing arm guide track can be quickly positioned, the personal safety of workers can be guaranteed, and potential safety hazards are avoided.

Owner:HUDONG ZHONGHUA SHIPBUILDINGGROUP

Sealing plate device of half ship floating end surface

ActiveCN110254614AReduce processing timeMeet the sealing conditionsVessel designingMarine engineeringUltimate tensile strength

The invention discloses a sealing plate device of a half ship floating end surface and belongs to the technical field of ship assembling. The sealing plate device of the half ship floating end surface comprises a sealing plate and multiple first tensioning components, wherein the sealing plate is used for sealing a closure opening of a half ship end surface; multiple first pullers are arranged on the sealing plate; one end of each first tensioning component is connected with a hull; the other end of each first tensioning component is connected with a first puller; and the lengths of the first tensioning components are adjustable. According to the sealing plate device of the half ship floating end surface, the sealing plate and the hull approach each other or are separated from each other through the first tensioning components; and therefore, the sealing plate device to be detached can avoid cutting treatment in the closure opening of the half ship end surface while the sealing condition of a hull cabin is satisfied, the treatment time of the closure opening of the half ship end surface is shortened, and the operation time is shortened; and meanwhile, the labor intensity of operation personnel is reduced.

Owner:GUANGZHOU SHIPYARD INTERNATIONAL LTD

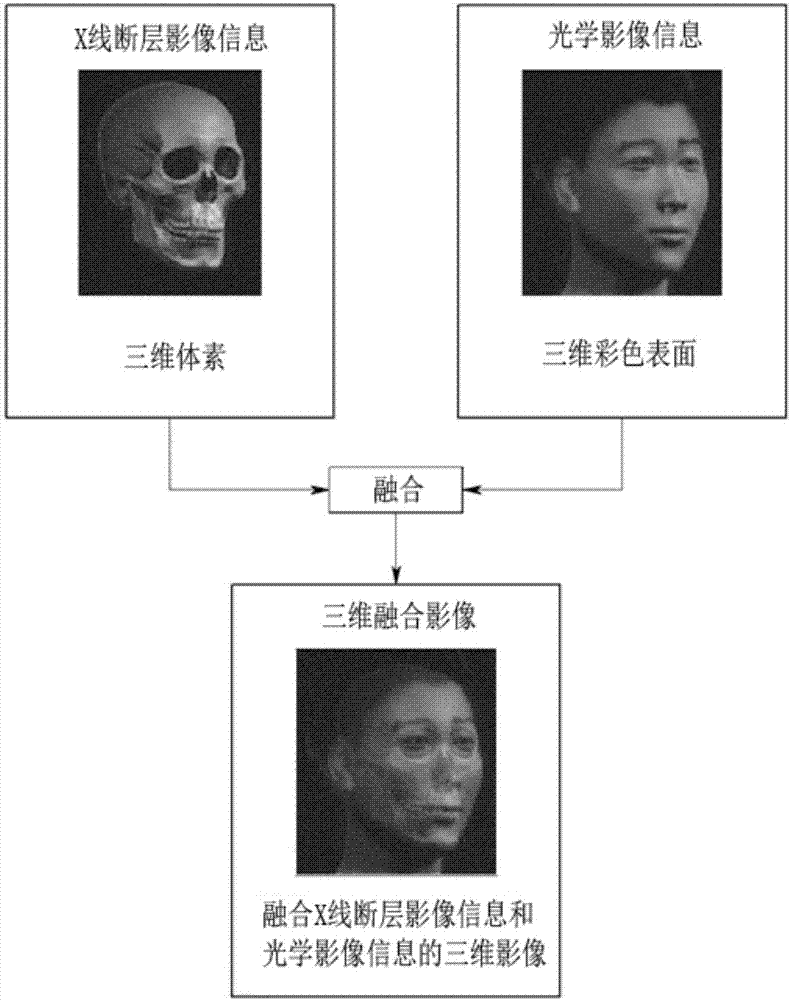

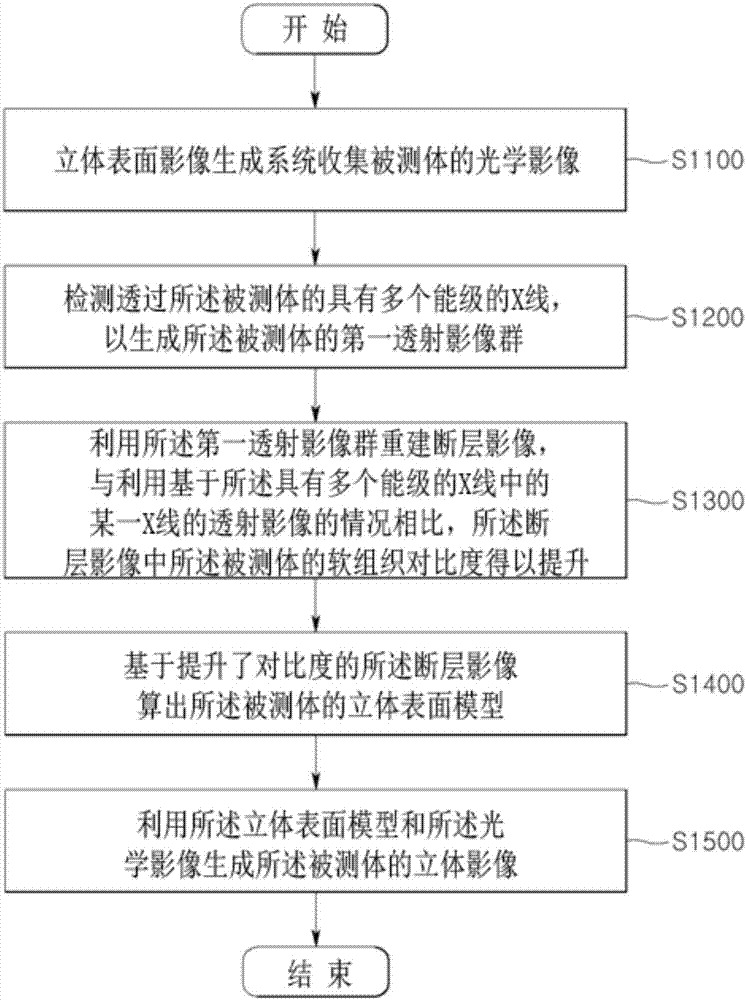

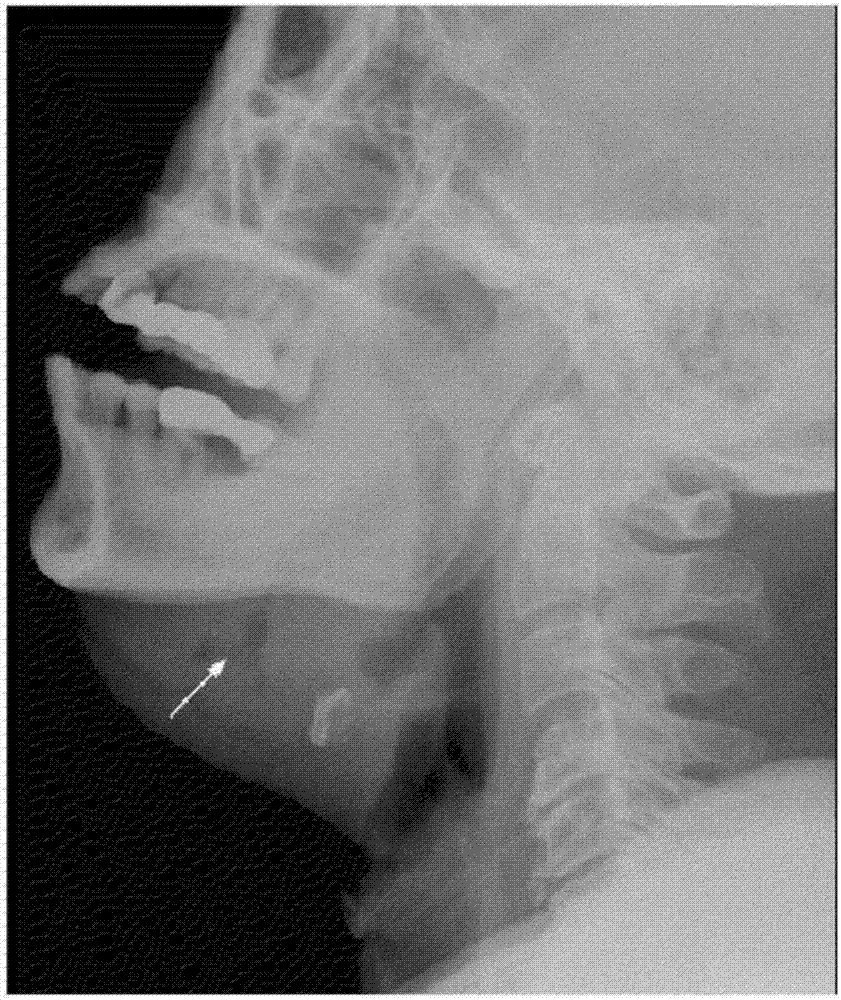

Method and system for generating three-dimensional image using multi-energy X-ray imaging and optical image

ActiveCN106982550AReduce mistakesImprove build accuracyImage enhancementReconstruction from projectionContrast levelRadiology

The present invention relates to a method and system for generating a three-dimensional surface image using multi-energy X-ray imaging and an optical image and, more particularly, to a method and system for generating a three-dimensional surface image using multi-energy X-ray imaging and an optical image, which comprises: reconstructing an X-ray tomographic image in which the contrast of a soft tissue including the skin of a subject is enhanced, using two or more pieces of multi-energy X-ray transmission data; calculating a three-dimensional surface model for the subject; and further generating a three-dimensional surface image of the subject by combining optical image information including color information and the like for the subject.

Owner:KOREA ELECTROTECH RES INST

Assembled supporting-free prefabricated light composite floor slab with ribs

The invention relates to a building floor slab, in particular to an assembled supporting-free prefabricated light composite floor slab with ribs. Longitudinal steel bars (or prestressed steel bars) and transverse steel bars are arranged at the bottom of a prefabricated slab, and prefabricated slab rib longitudinal bars (or prestressed steel bars) and stirrups or Rachel bars are further arranged at the bottom of the prefabricated slab, the steel bars are placed in a production mold of the prefabricated slab, construction members are bound with the steel bars, concrete is molded, polyphenyl plates or other light materials are placed on the concrete, plate ribs are poured, and the prefabricated portion of the supporting-free prefabricated light composite floor slab with ribs is produced; and the floor slab of the prefabricated portion is hoisted in place on site, the longitudinal steel bars and the transverse steel bars which are arranged on the upper portion of the floor slab are placed on the prefabricated portion, the concrete arranged on the upper portion of the floor slab is poured, and the supporting-free prefabricated light composite floor slab with ribs is produced. By adopting the supporting-free prefabricated light composite floor slab with ribs, the floor slab template and scaffolding work on the construction site can be basically omitted, construction material waste can be reduced in the maximum limit, floor slab industrialized production and standardized production requirements of plants can be met, and floor slab integral on-site assembly can be achieved.

Owner:沈阳易筑建材经销有限公司 +2

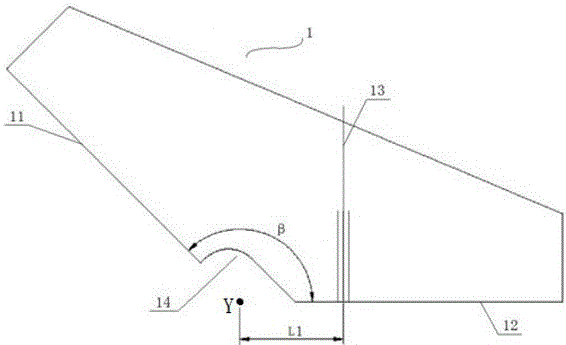

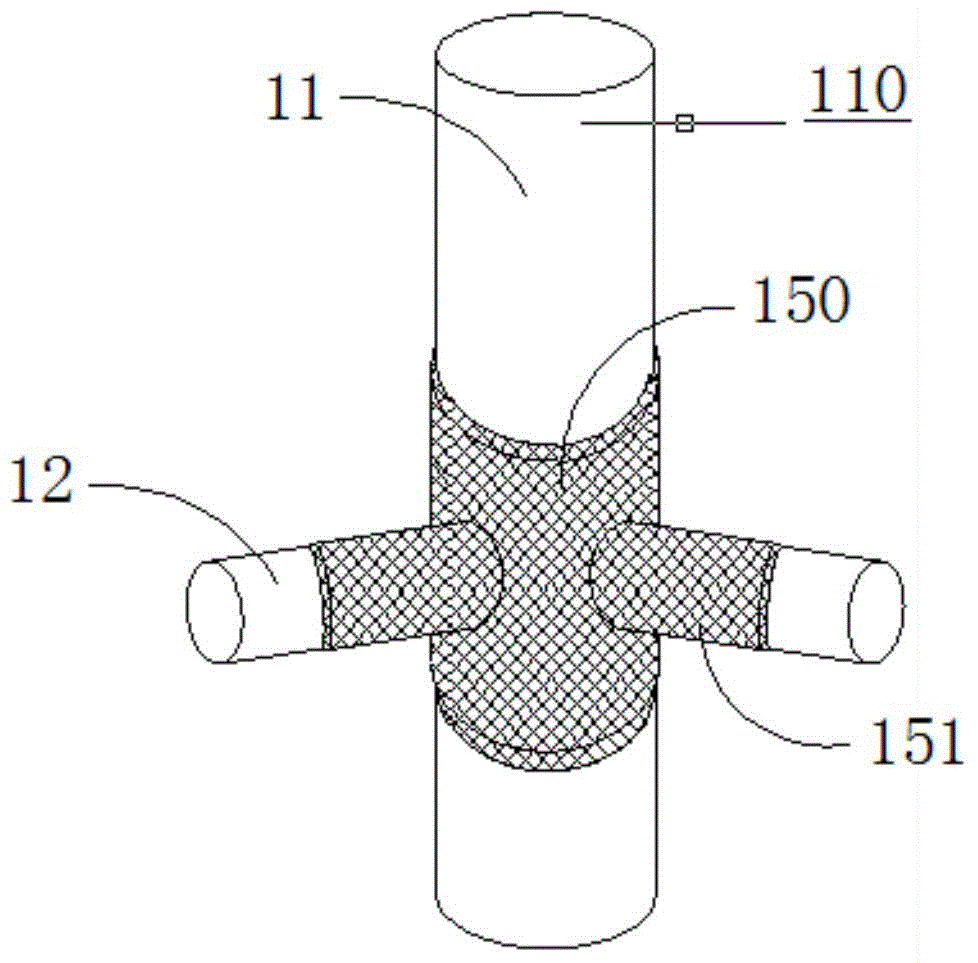

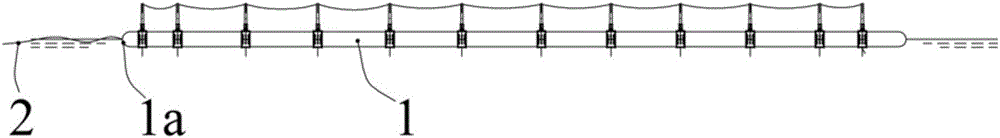

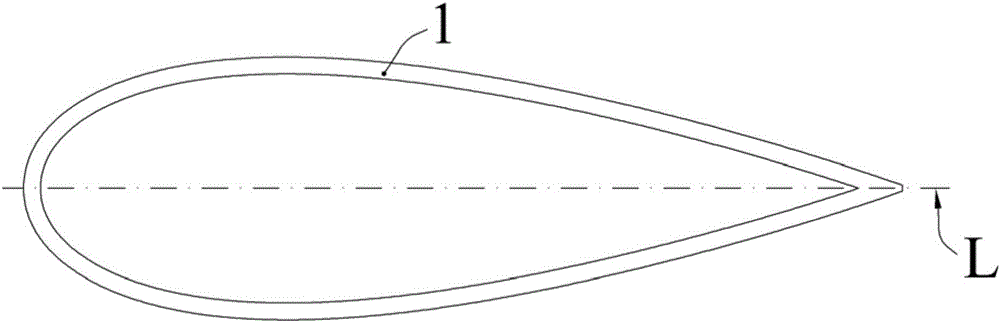

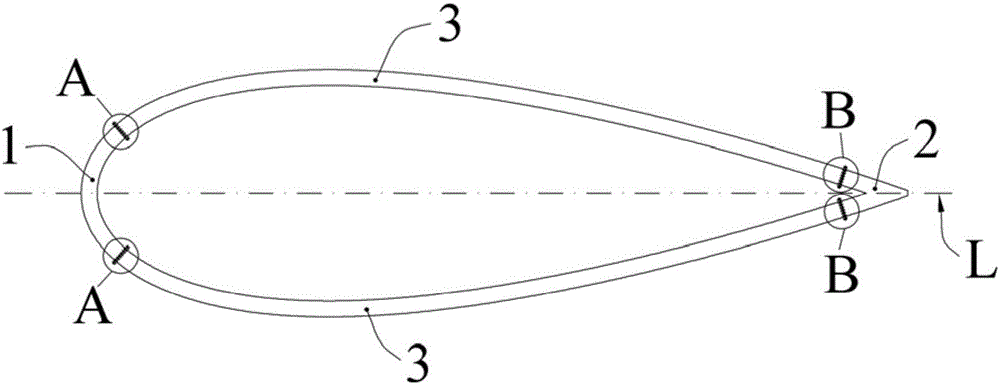

Assembling type structure of symmetric wing type net cage floating tube frame and construction method

ActiveCN106818579AHigh precisionGuaranteed accuracyClimate change adaptationPisciculture and aquariaStraight tubeSingle point mooring

The invention discloses an assembling type structure of a symmetric wing type net cage floating tube frame and a construction method. The assembling type structure is composed of a wingtip component (1), a wing tail component (2) and two wing side components (3), wherein the wingtip component (1) is provided with an arc metal tube (11) and two metal flanges (12); the wing tail component (2) is provided with a V-shaped tube (21) and two connecting flanges (22) made of the same material as the V-shaped tube (21); each wing side component (3) is provided with an HDPE straight tube (31) and two HDPE flanges (32). According to the assembling type structure, the high-precision symmetric wing type outer contour can be constructed, the structure conforms to the single point mooring using characteristic of the symmetric wing type net cage floating tube frame, and the assembling type structure has the advantage of being low in building cost; the construction method has the advantages of being high in construction precision and high in speed.

Owner:SOUTH CHINA SEA FISHERIES RES INST CHINESE ACAD OF FISHERY SCI

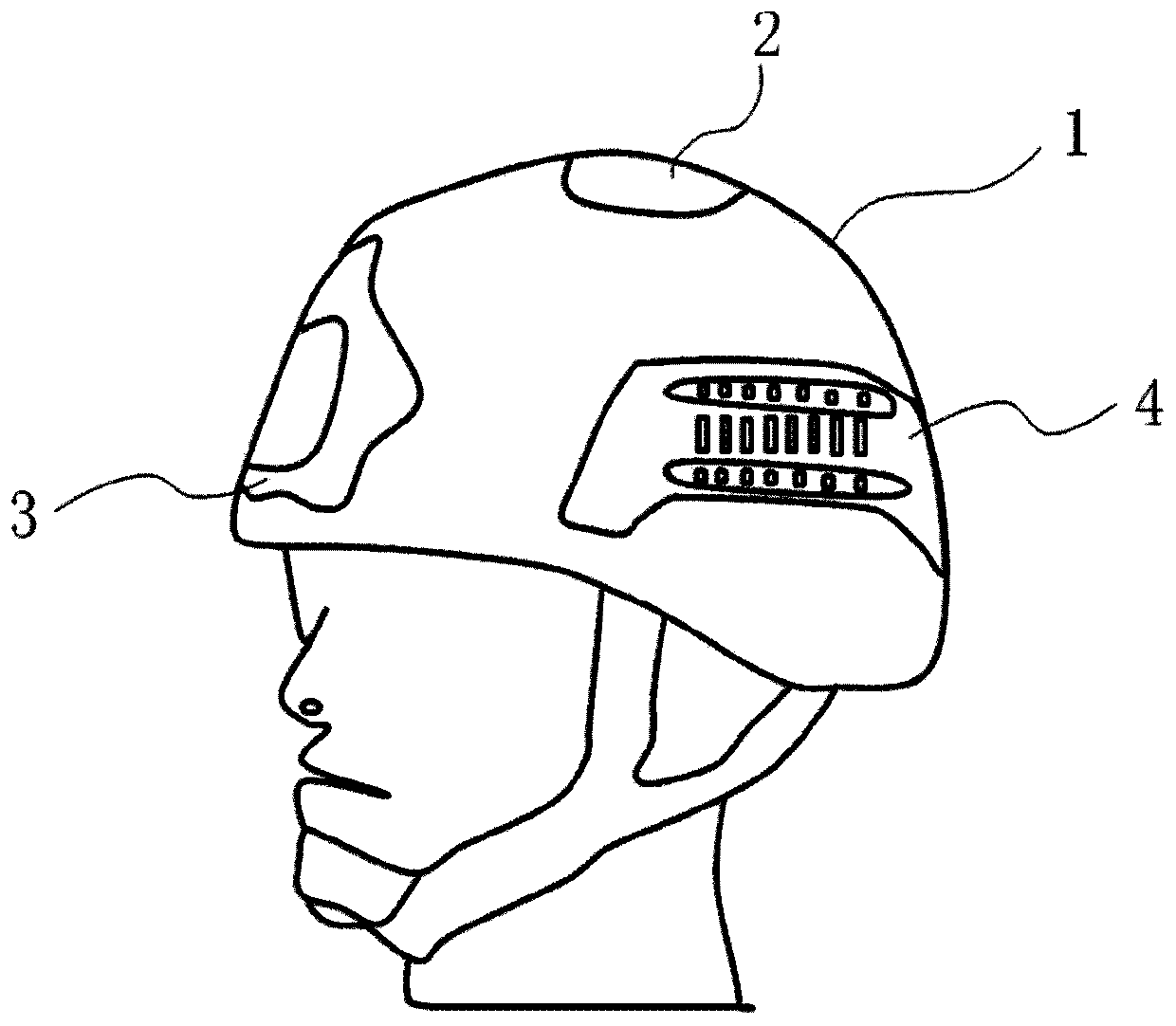

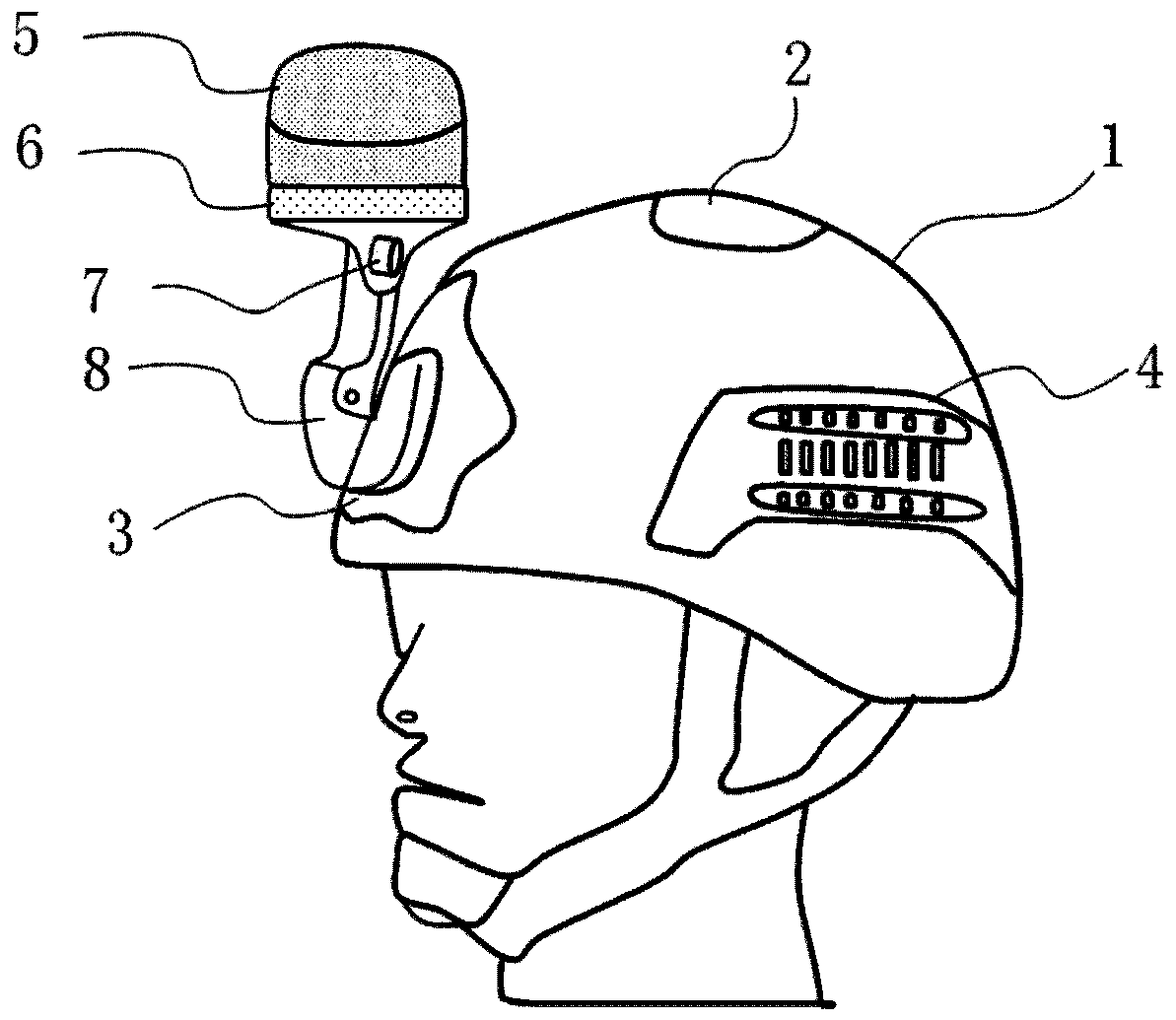

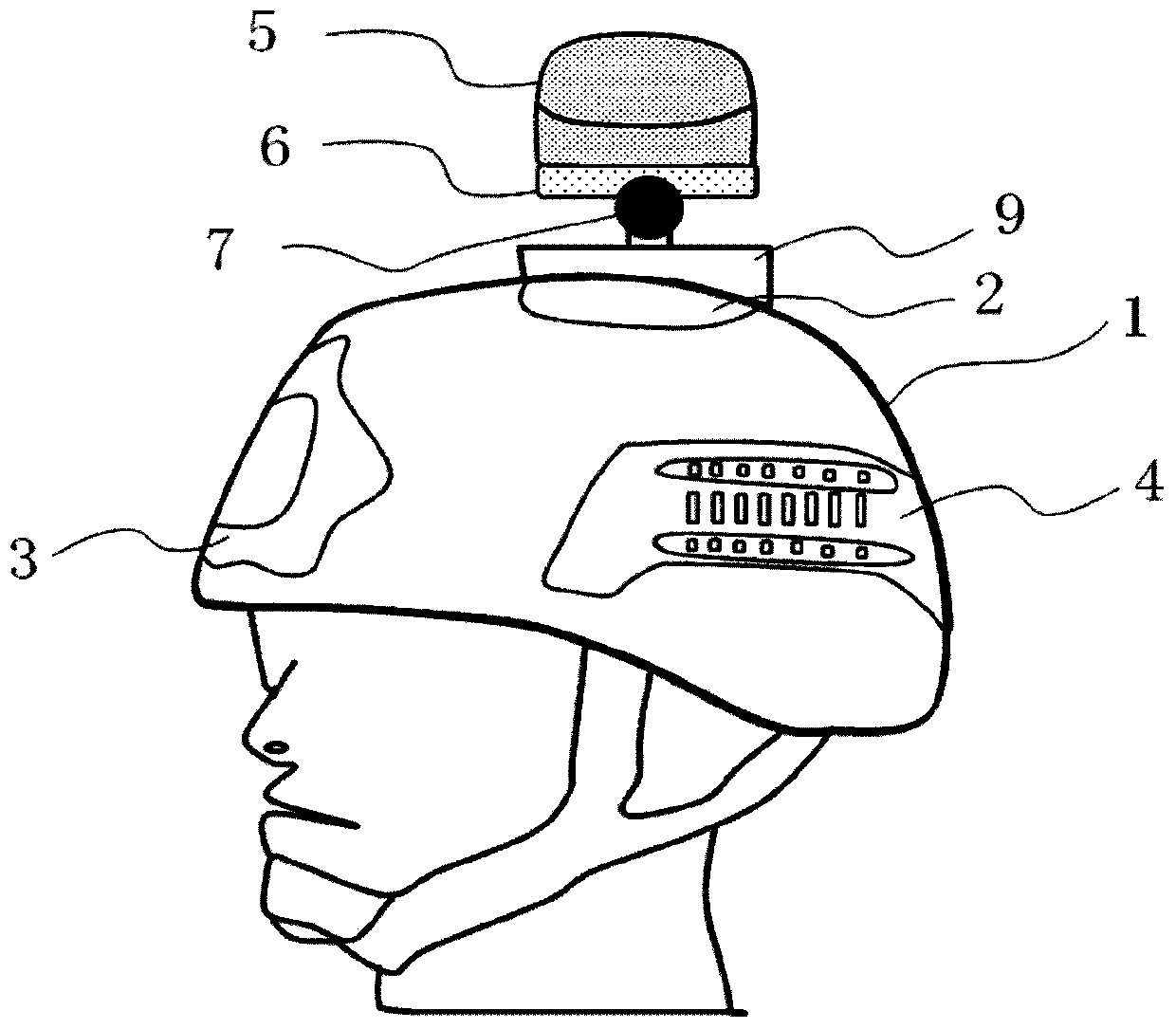

Tactical command map drawing and positioning system and helmet

The invention provides a helmet based on tactical command. The helmet comprises a helmet main body, a mounting base, a support assembly, a driving unit and a radar. The helmet body is detachably arranged on the head of a user in a sleeving mode, the mounting base is arranged on the front end face and / or the top and / or the side face of the surface of the helmet body, and the support assembly is fixedly mounted on the mounting base of the helmet body. The radar is fixedly connected with the end part of the support assembly. A transmission shaft of the driving unit is connected with the radar andfixedly installed on one side of the radar. Through the radar capable of being installed at multiple positions, multi-directional position detection can be achieved, a user does not need to hold theradar by hand for operation, and great convenience is achieved. Meanwhile, the invention further provides a map drawing and positioning system used on the helmet, information of the control unit, theradar and the remote client can be transmitted under wireless connection, the positioning accuracy of combat personnel in a complex environment and the map construction accuracy of a battlefield environment are improved, and potential safety hazards in the battlefield environment are reduced.

Owner:ENG UNIV OF THE CHINESE PEOPLES ARMED POLICE FORCE

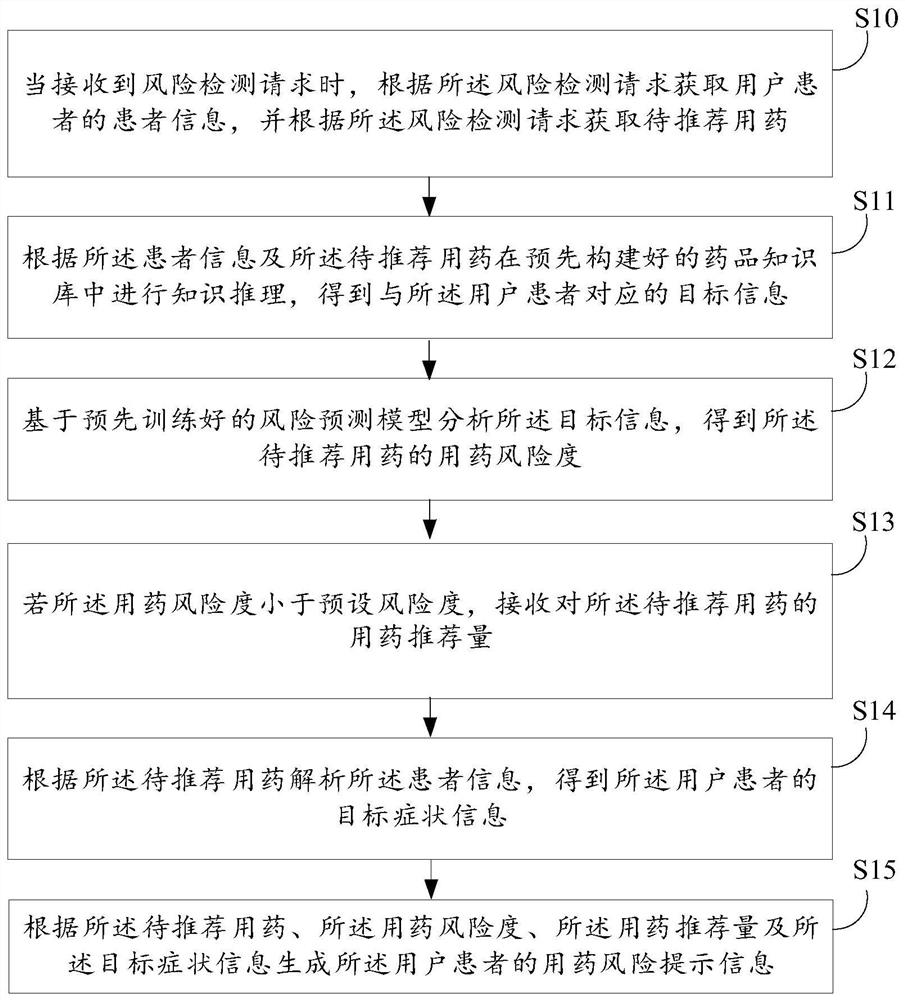

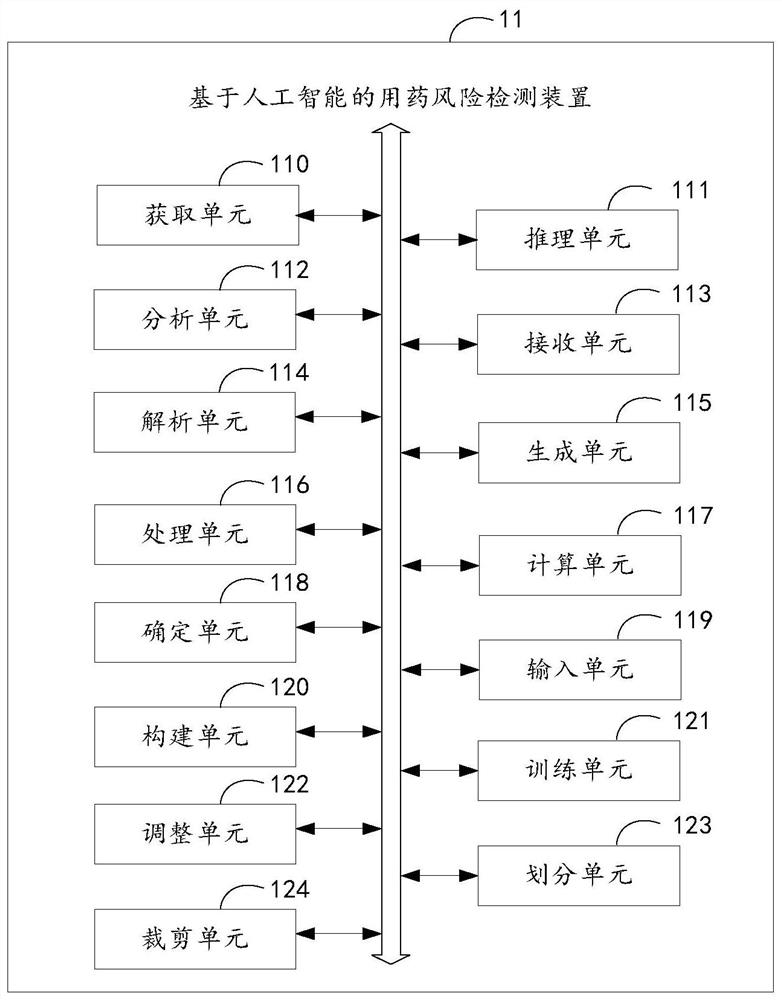

Drug use risk detection method based on artificial intelligence and related equipment

PendingCN113724830AAccurate acquisitionImprove production efficiencyDrug and medicationsNatural language data processingMedicineMedication risk

The invention relates to artificial intelligence, and provides a medication risk detection method based on artificial intelligence and related equipment. The method comprises the steps of obtaining patient information of a user patient according to a risk detection request, and obtaining a to-be-recommended medicine according to the risk detection request; performing knowledge reasoning in a medicine knowledge base according to the patient information and the to-be-recommended medicine to obtain target information corresponding to the user patient; analyzing the target information based on a risk prediction model to obtain the medication risk degree of the to-be-recommended medication; if the medication risk degree is smaller than a preset risk degree, receiving a medication recommendation amount of the to-be-recommended medication; analyzing the patient information according to the to-be-recommended medication to obtain target symptom information of the user patient; and generating prompt information of the user patient according to the to-be-recommended medicine, the medicine risk degree, the medicine recommendation amount and the target symptom information. According to the invention, the accuracy of medication risk detection can be improved. In addition, the invention also relates to a block chain technology, and the prompt information can be stored in a block chain.

Owner:深圳平安智慧医健科技有限公司

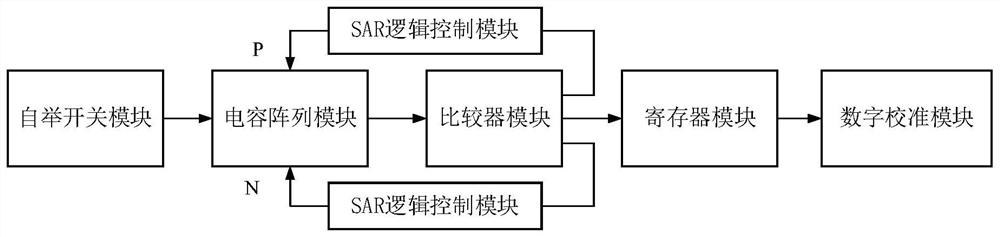

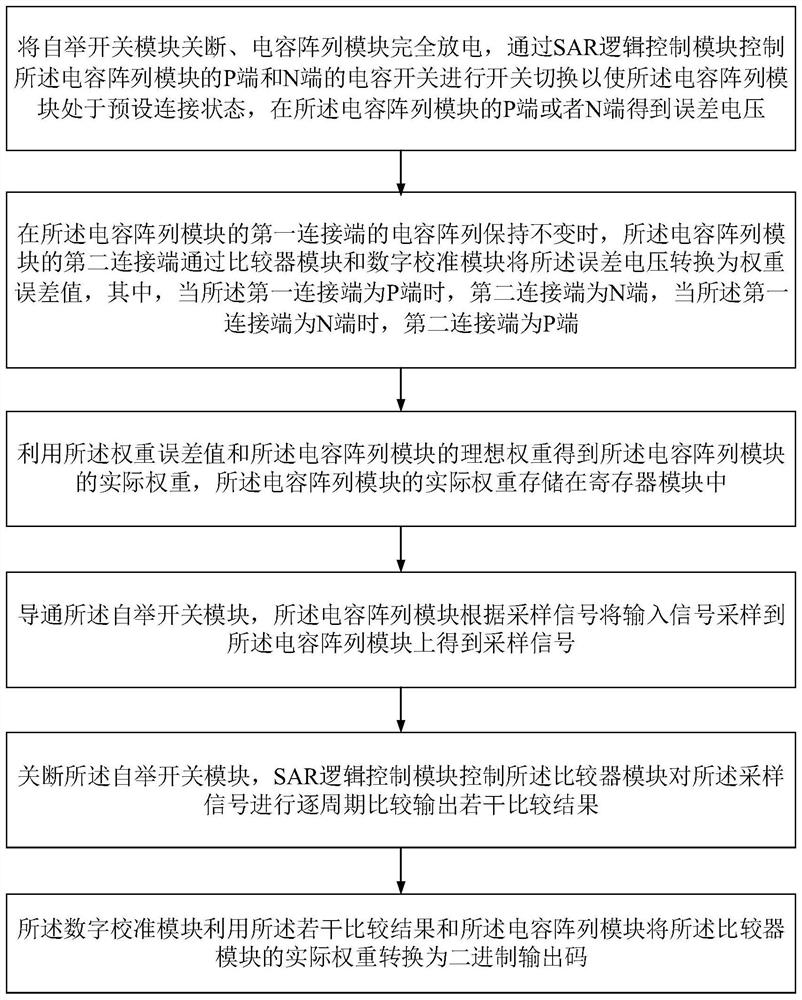

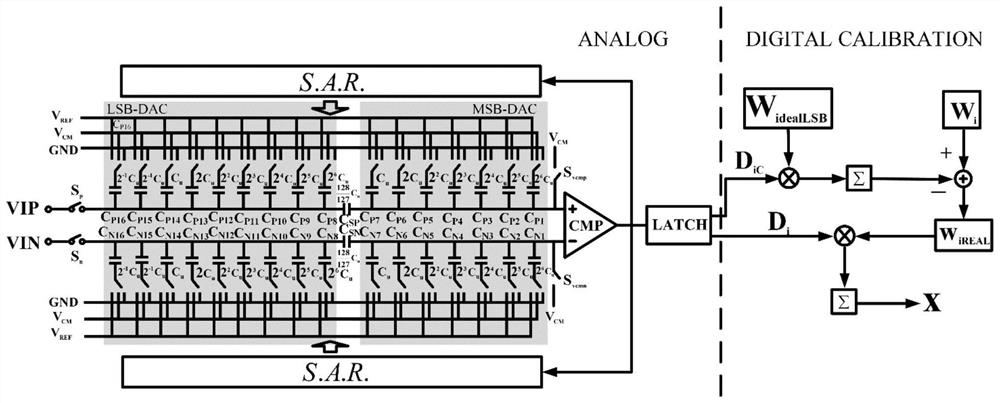

Digital background self-calibration circuit structure and method of single-channel high-speed high-precision SAR ADC

ActiveCN112290945AImprove build accuracyValid calibrationAnalogue/digital conversion calibration/testingCapacitanceData transformation

The invention discloses a digital background self-calibration circuit structure and method for a single-channel high-speed high-precision SAR ADC, and the structure comprises a bootstrap switch module, a capacitor array module, a comparator module, a register module, an SAR logic control module, and a digital calibration module. The bootstrap switch module is used for controlling the transmissionof an input signal; the capacitor array module is used for obtaining an error voltage and obtaining a sampling signal; the comparator module is used for comparing the voltages of the sampling signalsat different ends; the register module is used for storing the actual weight of the capacitor array module; the SAR logic control module is used for controlling a capacitor at the switch end of the capacitor array module to perform switch switching; and the digital calibration module is used for performing mathematical operation on an output result of the comparator module to obtain an error weight and an actual weight of the capacitor array module. According to the calibration method, the weight value of the high-weight-bit capacitor is effectively calibrated, and the establishment precisionof the high-weight-bit capacitor is improved, so that the data conversion rate is improved.

Owner:XIDIAN UNIV

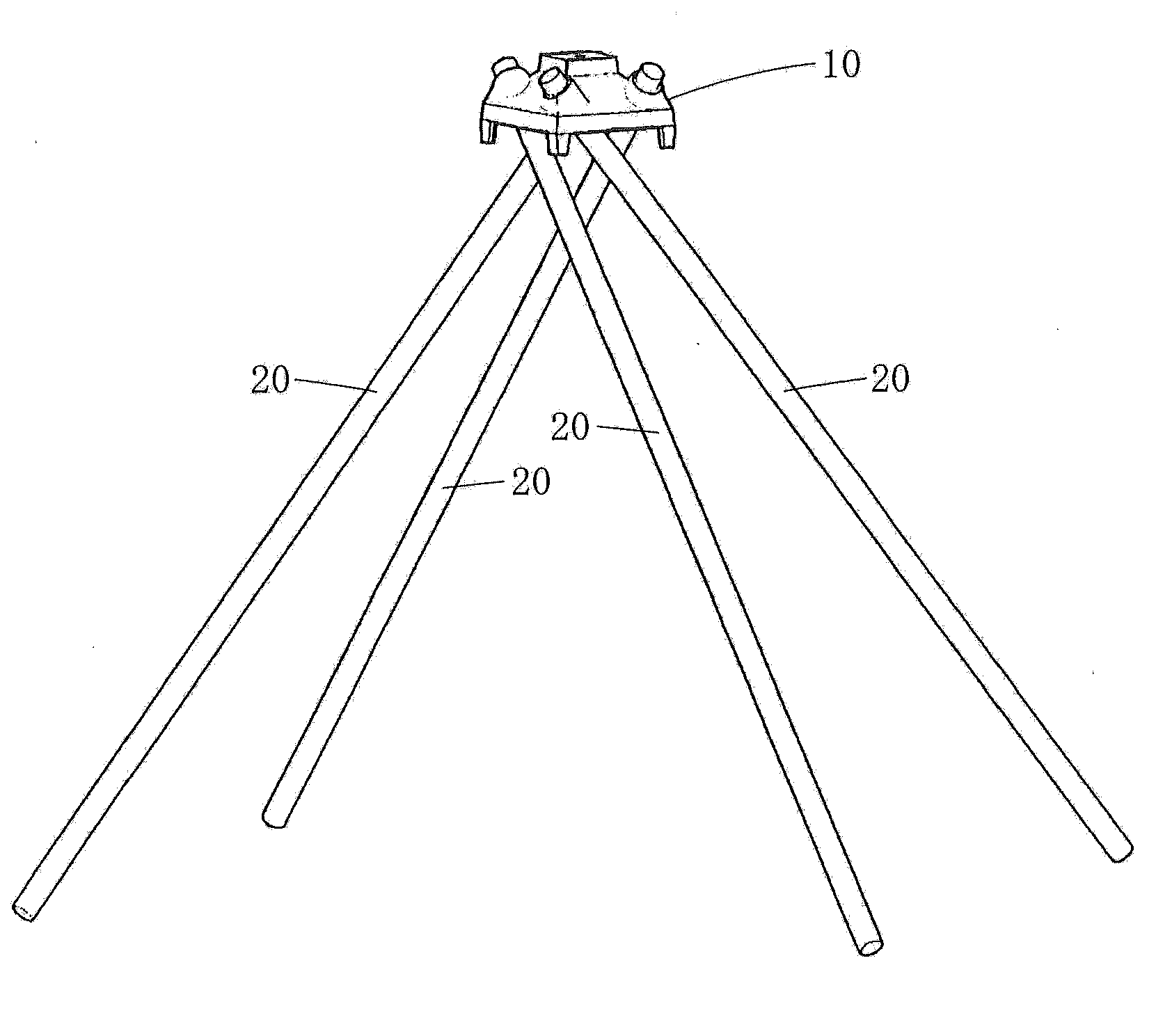

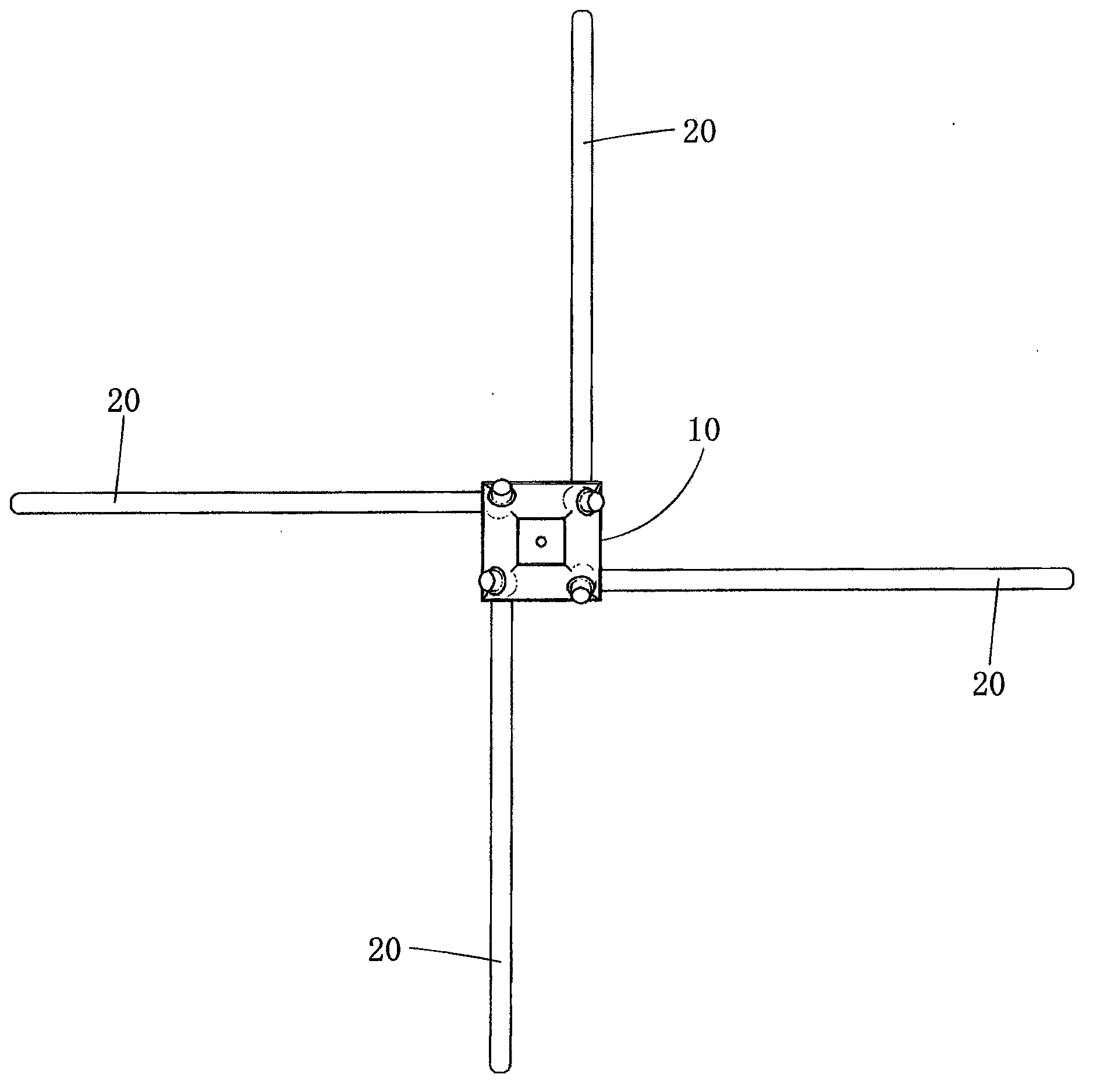

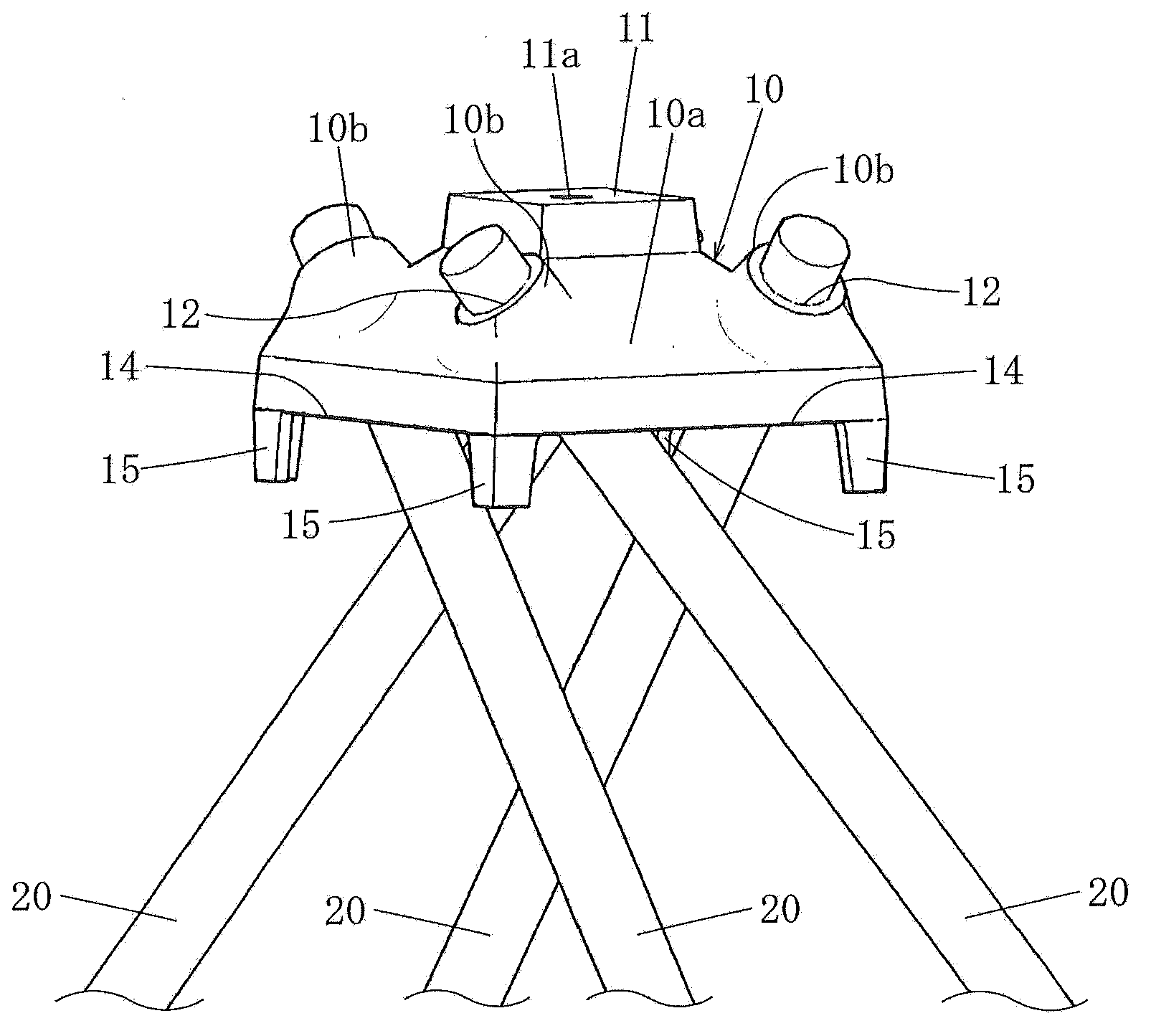

Foundation element and a complete structure produced therewith

InactiveCN103541349AEliminate bulking problemsImprove stabilityBulkheads/pilesWater useStructural engineering

The solution, the improving the stability in the mounting, and the possibility of the reduction in weight it grows serious with volume may be referred to the difficult that the in-phase problem happens. Base foundation obtaining and realizes the improvement and cost reduction of handling It is the base foundation in which there is little the concern in which the break down by the moisture freeze occurs. The completed structure water using the base foundation provides. In the base foundation, it does not interfere about the height direction with the angle and it extends as the other direction and one end is opened around the central part of the one-way of the height direction and the through-hole more than opened of the other end is prepared with another side of the height direction. The base foundation puts the respective inserted pile into the through-hole into the underground and it is installed at the land. The base foundation comprises the main body, formed in the inner portion into the bowl form overturned to form the internal space opened to another side of the height direction and the multiple partition members which is formed with the pipe shape and is prepared by the hole of the inner portion in the peripheral part of the main body to form the through-hole through the main body.

Owner:LASCO JAPAN

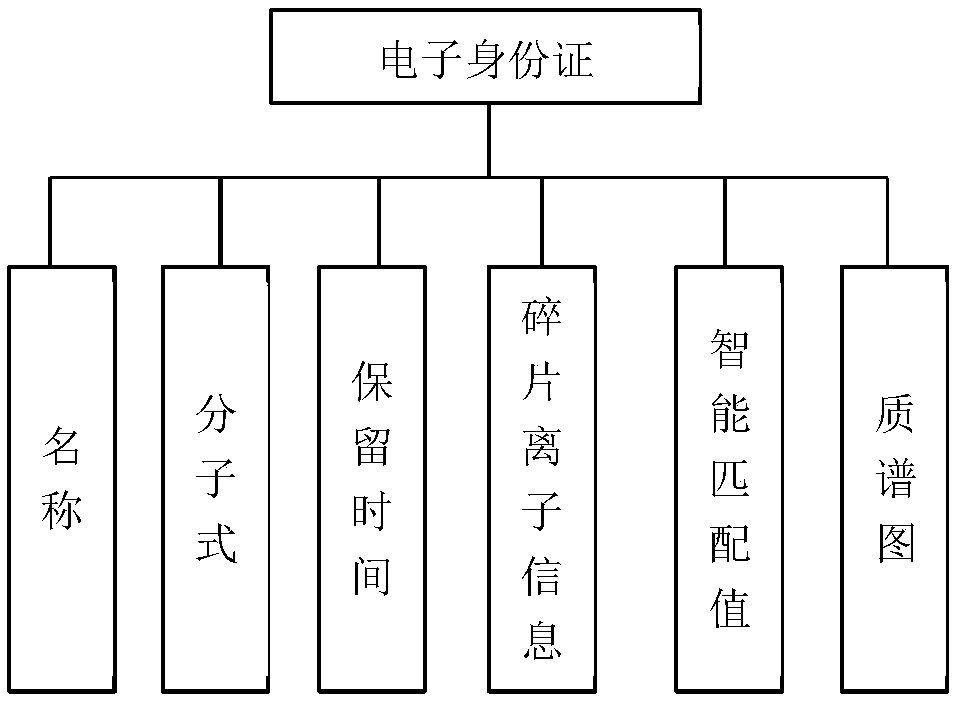

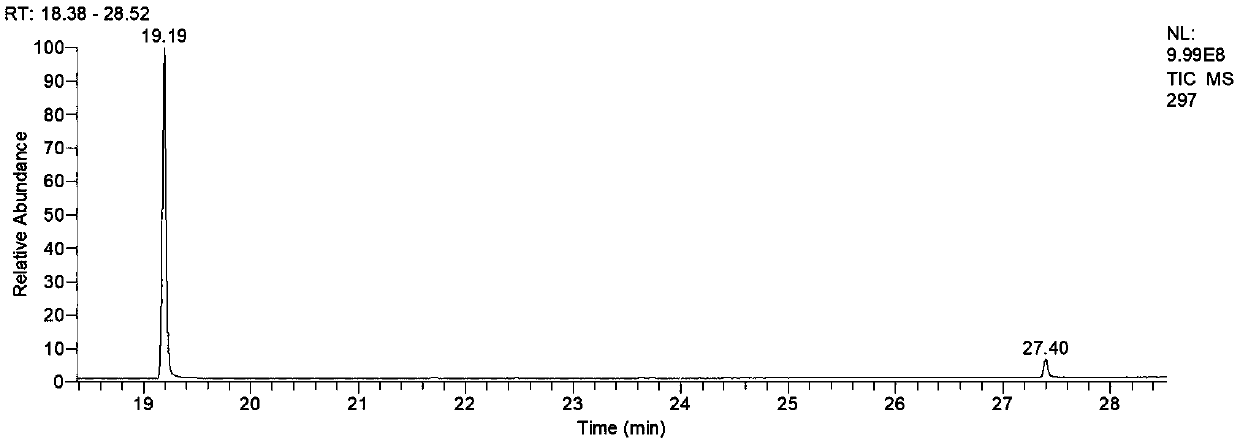

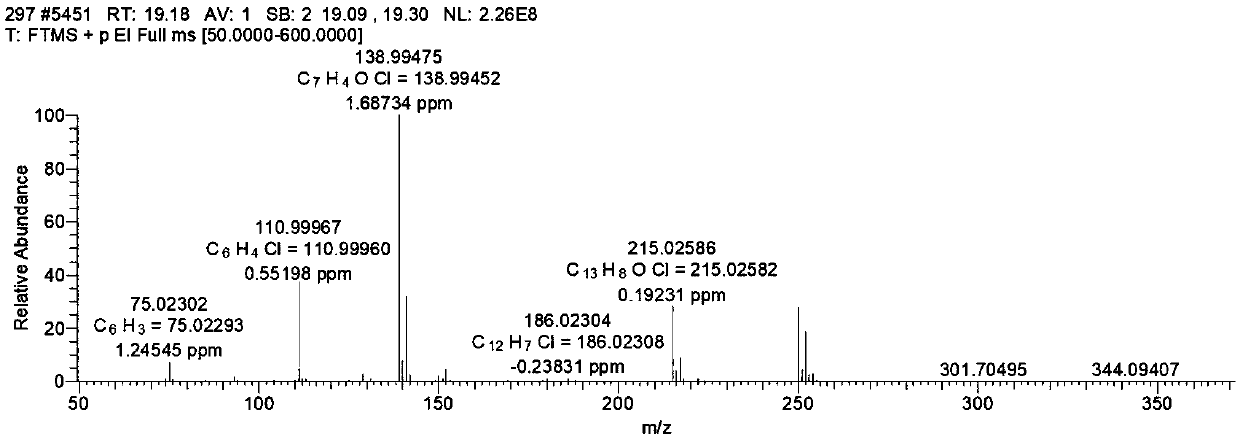

Electronic identity database and detection method of pesticide compounds in edible agricultural products based on GC-Q-Orbitrap

ActiveCN109557197AImprove accuracyImprove reliabilityComponent separationPesticide residueRetention time

The invention discloses an electronic identity database and a detection method of pesticide compounds in edible agricultural products based on a GC-Q-Orbitrap. The electronic identity database contains an information collection of electronic identity cards for a plurality of pesticide compounds and is ordered according to the retention time in the electronic identity cards. The electronic identitycard includes pesticide compound information, retention time, mass spectrum, and fragment ion information and a smart matching value. The detection method comprises the steps of sample pretreatment,GC-Q-Orbitrap operating condition setting and pesticide residue screening process in the sample. The GC-Q-Orbitrap operating condition setting comprises the step of setting appropriate chromatographicconditions and mass spectrometry conditions. The pesticide screening process comprises the steps of: first using the retention time to find a pesticide compound in the electronic identity database, and if matched, extracting information of a corresponding electronic identity card; and then comparing the smart matching value, and if less than a threshold, recording and displaying the result to complete the screening.

Owner:CHINESE ACAD OF INSPECTION & QUARANTINE +1

Jacket, jacket foundation platform and jacket construction method

ActiveCN105019419BImprove stabilityImprove fatigue resistanceArtificial islandsWind motor supports/mountsArchitectural engineeringConductor pipe

Owner:CHINA ENERGY ENG GRP GUANGDONG ELECTRIC POWER DESIGN INST CO LTD

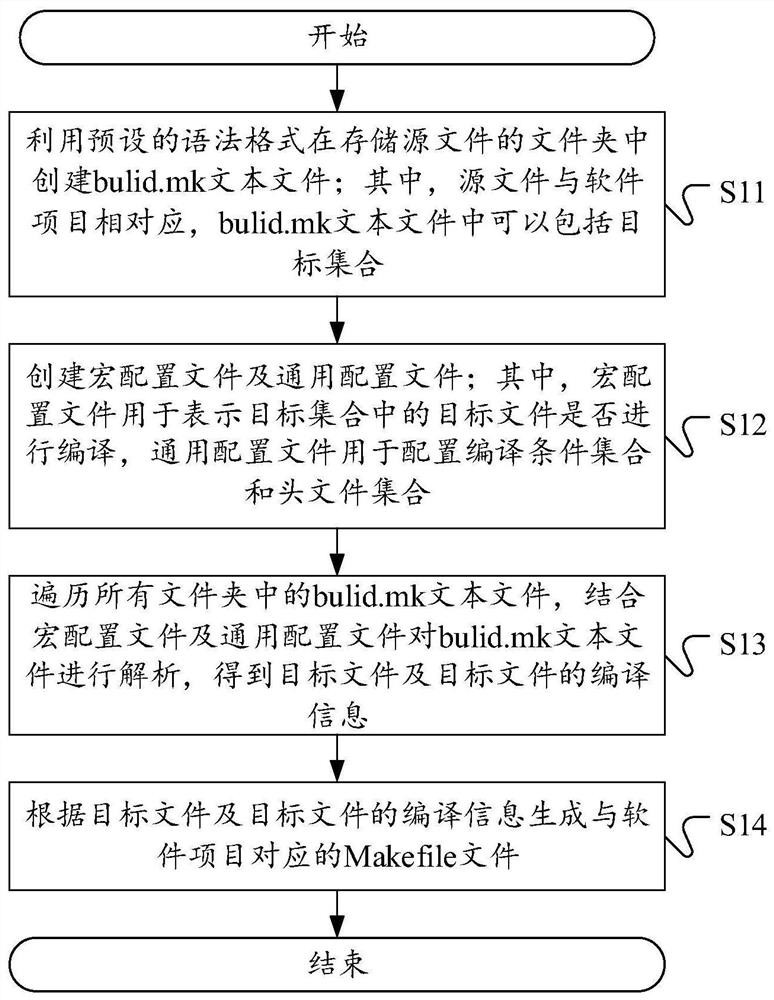

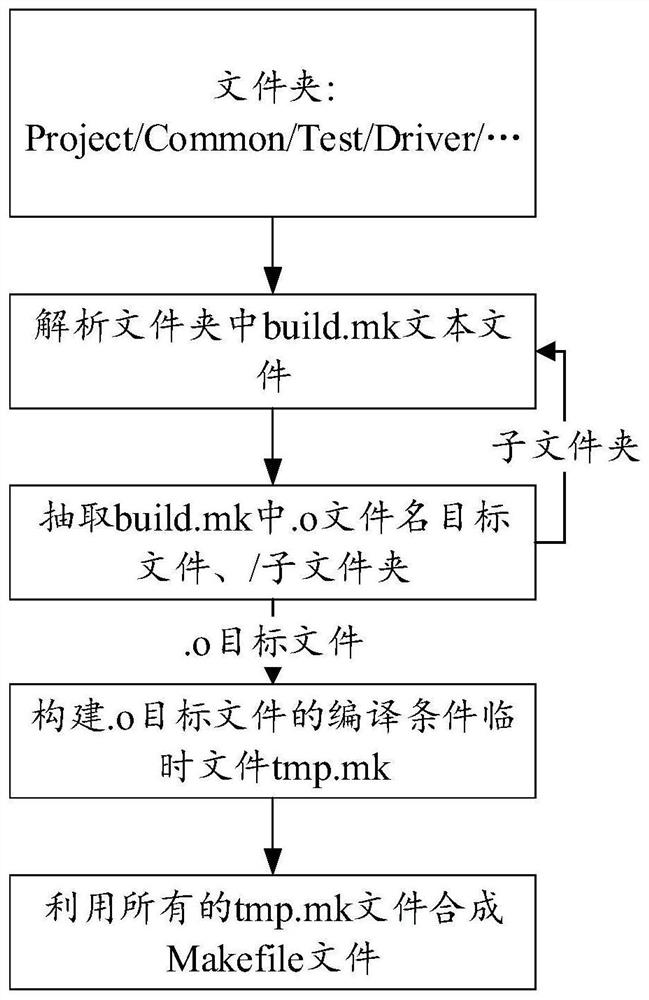

Makefile file generation method and device, equipment and medium

PendingCN111857725AReduce human involvementImprove production efficiencyProgram documentationFile/folder operationsConfigfsSoftware engineering

The invention discloses a Makefile file generation method and device, equipment and a computer readable storage medium. The method comprises the steps of creating a bulid.mk text file in a folder storing a source file by using a preset grammar format; creating a macro configuration file and a general configuration file; analyzing the bulid.mk text file in combination with the macro configuration file and the general configuration file to obtain a target file and compiling information of the target file; and generating a Makefile file corresponding to the software project. The invention discloses the technical scheme. The Makefile file is automatically generated by creating a bulid.mk text file, creating a macro configuration file and a universal configuration file and analyzing the bulid.mk text file in combination with the macro configuration file and the universal configuration file. Therefore, the generation efficiency and the generation accuracy of the Makefile file are improved.

Owner:SHANDONG YUNHAI GUOCHUANG CLOUD COMPUTING EQUIP IND INNOVATION CENT CO LTD

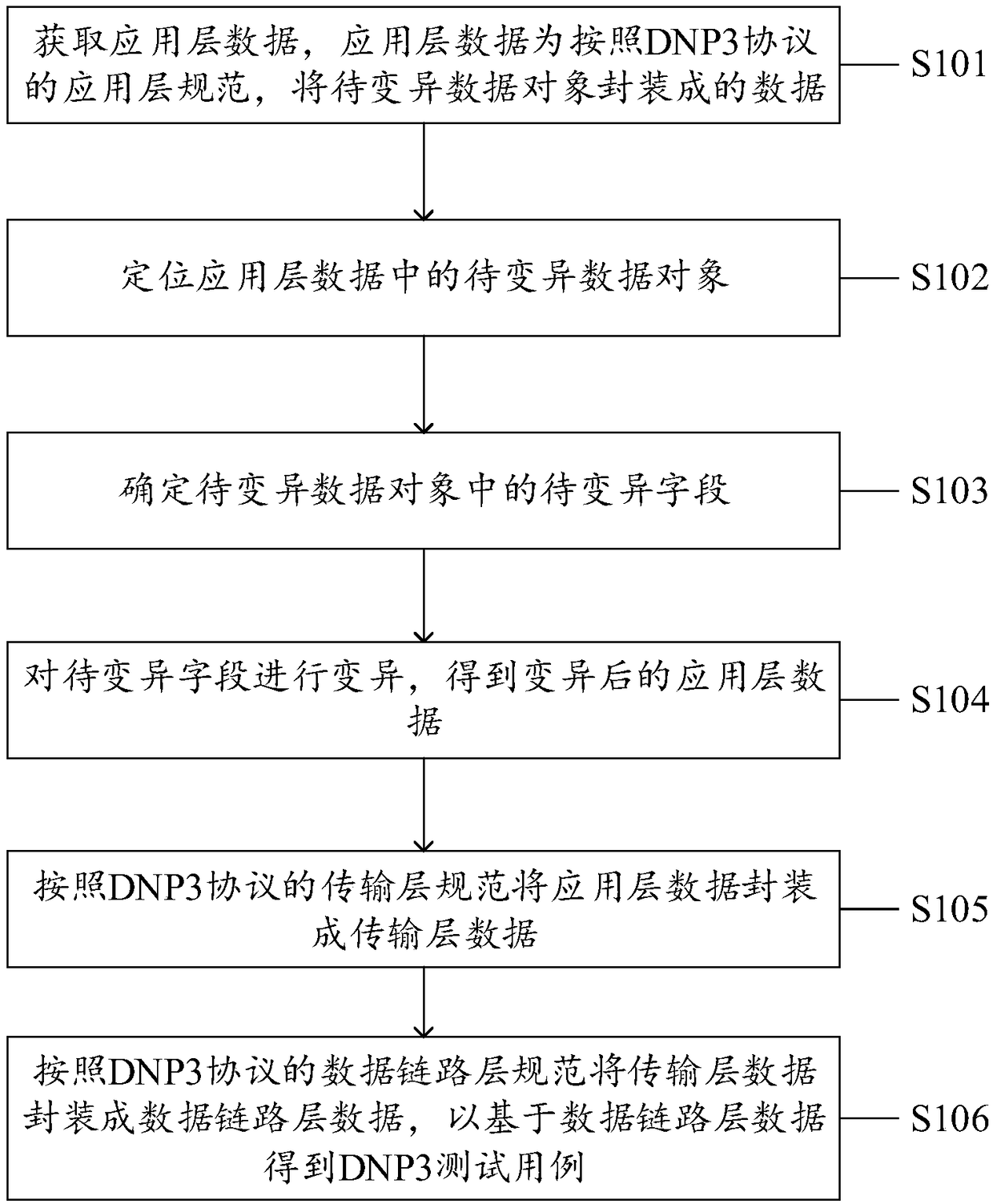

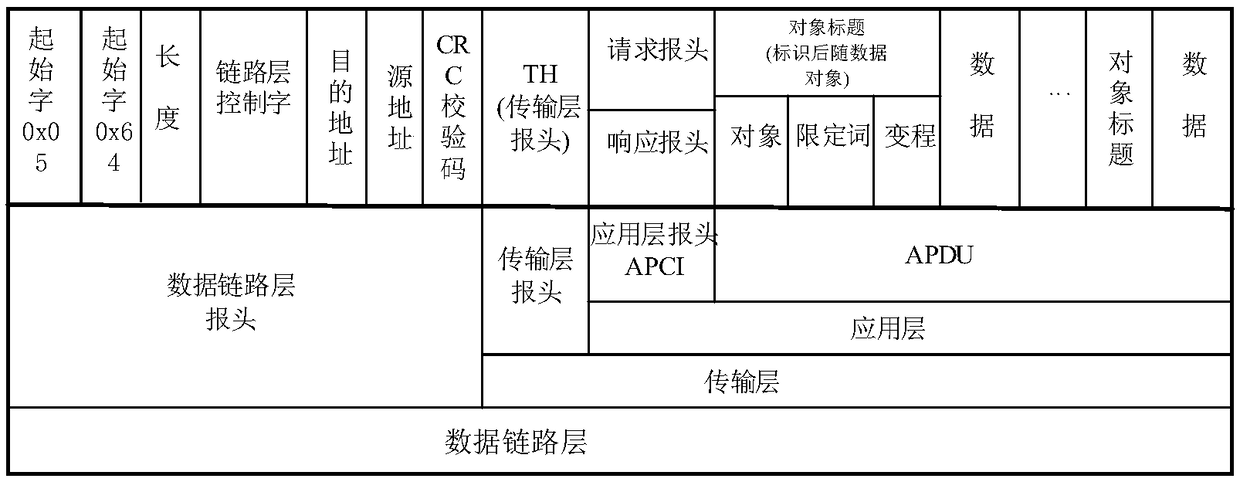

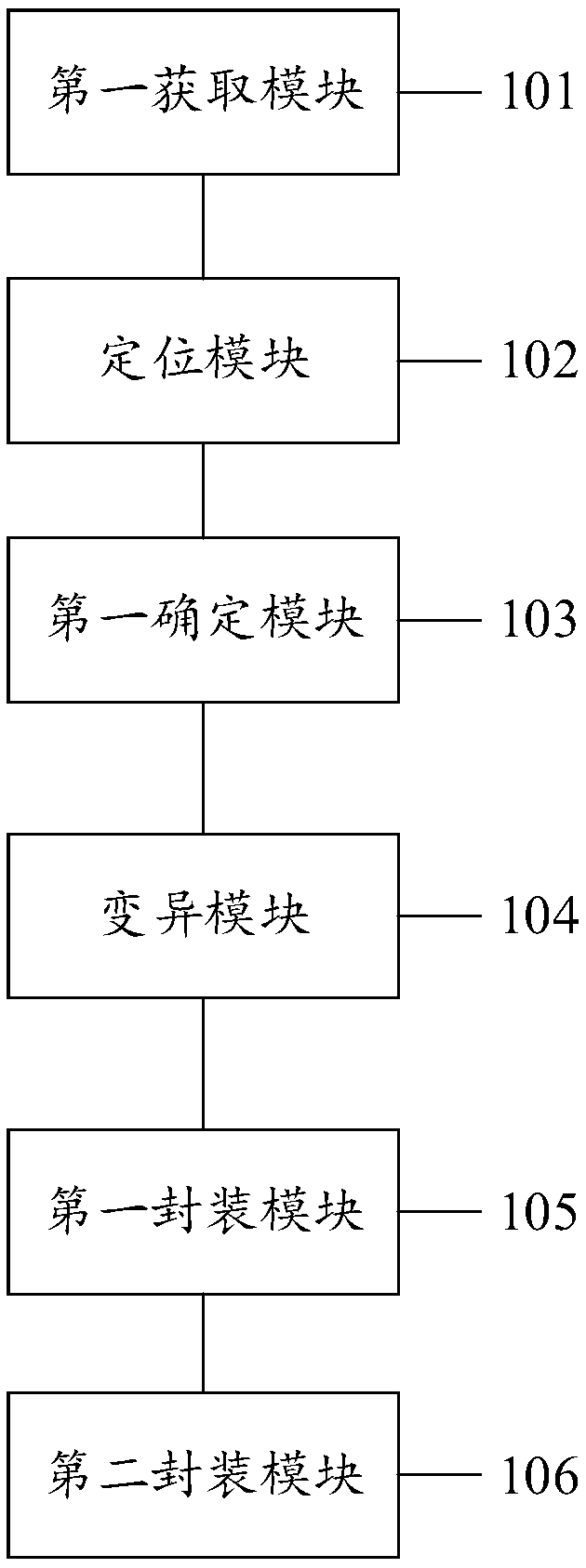

DNP3 testing case generation method, system, device and computer medium

InactiveCN109088861AImprove build accuracyImprove stabilityTransmissionTransport layerProtocol Application

The invention discloses a DNP3 testing case generation method, a system, a device and a computer medium, which are applied in the DNP3 protocol. The method comprises the following steps: obtaining application layer data, wherein the application layer data is data encapsulated by a data object to be mutated according to the application layer specification of the DNP3 protocol;locating the data objects to be mutated in the application layer data; determining a field to be mutated in the data object to be mutated; the mutation is performed on the mutated fields to obtain mutated application layerdata; according to the transport layer specification of DNP3 protocol, the application layer data is encapsulated into transport layer data. The transport layer data is encapsulated into the data link layer data according to the data link layer specification of the DNP3 protocol. The invention discloses a DNP3 test case generation method, a system, a device and a computer-readable storage medium,which ensure that the data of a data link layer must conform to the DNP3 protocol and contain fields to be mutated, and improves the generation accuracy of the DNP3 test case generation method.

Owner:HANGZHOU ANHENG INFORMATION TECH CO LTD

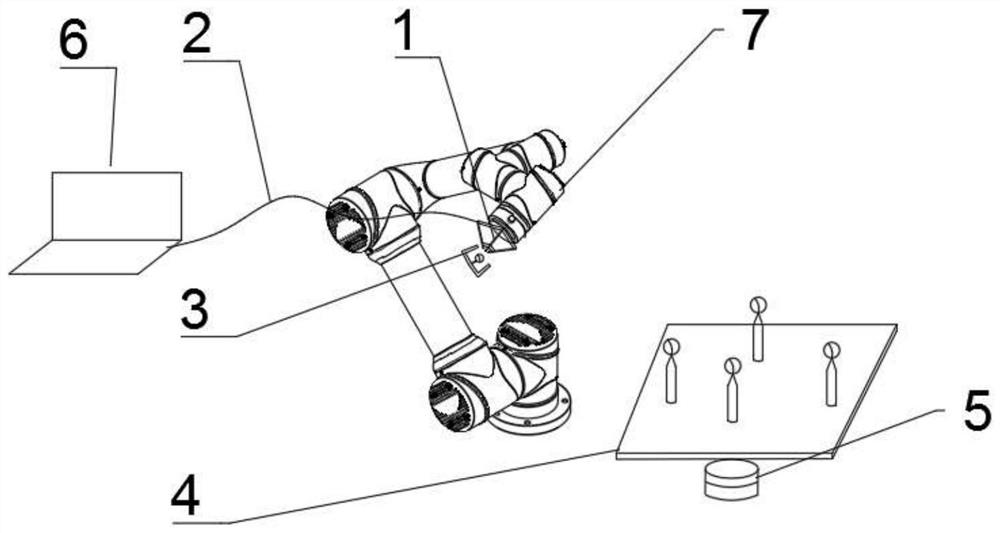

Industrial robot D-H parameter three-dimensional self-calibration correction device and method

ActiveCN113146613AGood precisionGuaranteed accuracyProgramme-controlled manipulatorSimulationData transmission

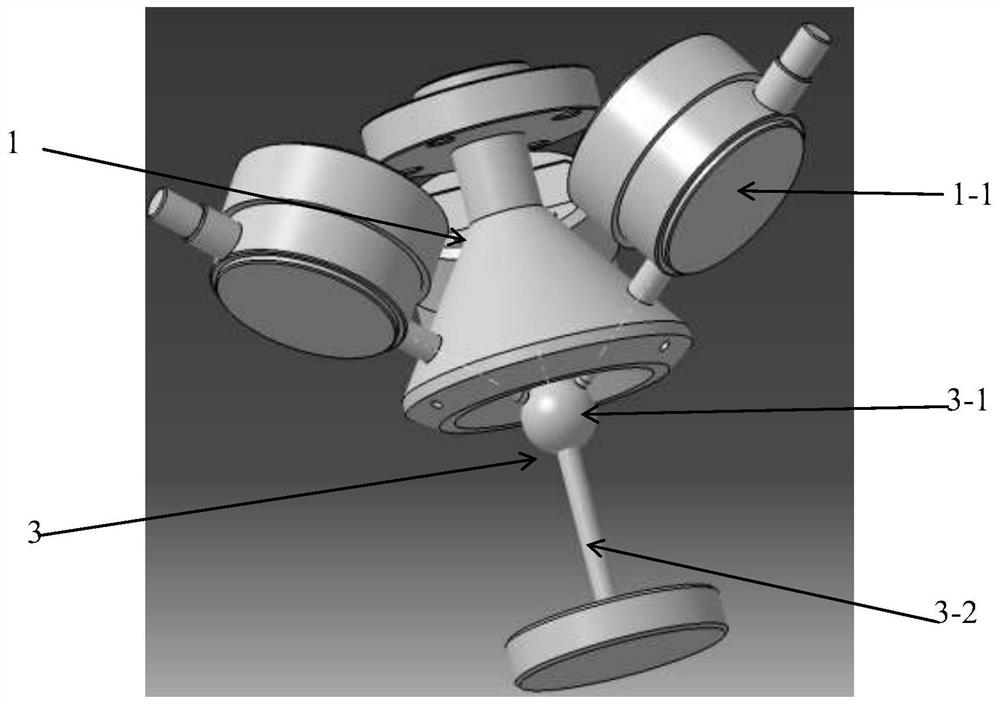

The invention discloses an industrial robot D-H parameter three-dimensional self-calibration correction device and method, relates to the field of robot correction, and aims to solve the problems in the prior art. The device comprises a three-dimensional calibrator, a data transmission cable, a zero-position rapid positioning clamp, a four-ball calibration table, a three-dimensional angle adjuster and a control computer. The three-dimensional calibrator is composed of three high-precision grating displacement sensors which are perpendicular to one another, and each high-precision grating displacement sensor is connected with the control computer through the data transmission cable. The three-dimensional calibrator is mounted at the tail end of a calibrated industrial robot, measures four standard balls on the four-ball calibration table, and performs high-precision positioning on a TCP point of the robot through the standard balls. The zero-position rapid positioning clamp is used for calibrating the three-dimensional calibrator. The three-dimensional angle adjuster is arranged below the four-ball calibration table. According to the device, the acquisition cost of the whole device can be greatly reduced while the calibration precision is ensured, the use mode is quick, simple and convenient, and the device can be widely popularized in various use units.

Owner:吉林省计量科学研究院 +1

Data query method, system and equipment and computer readable storage medium

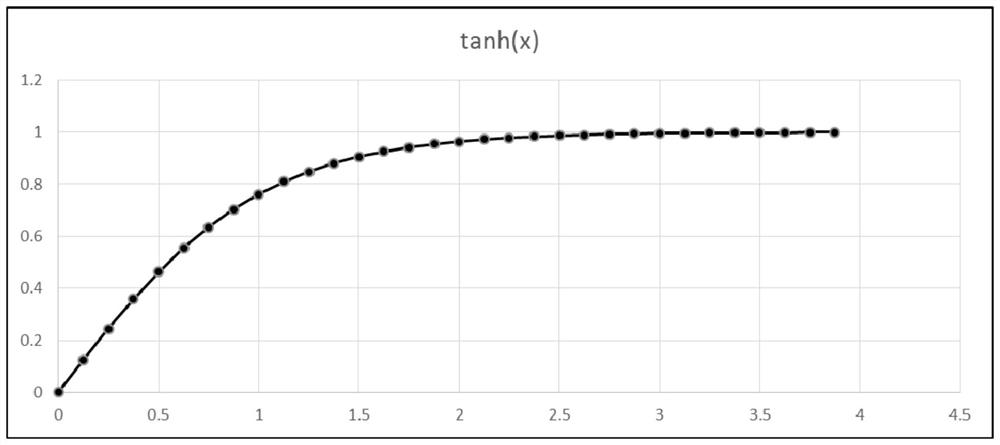

PendingCN114357375AImprove build accuracyGuaranteed accuracyComplex mathematical operationsEngineeringLookup table

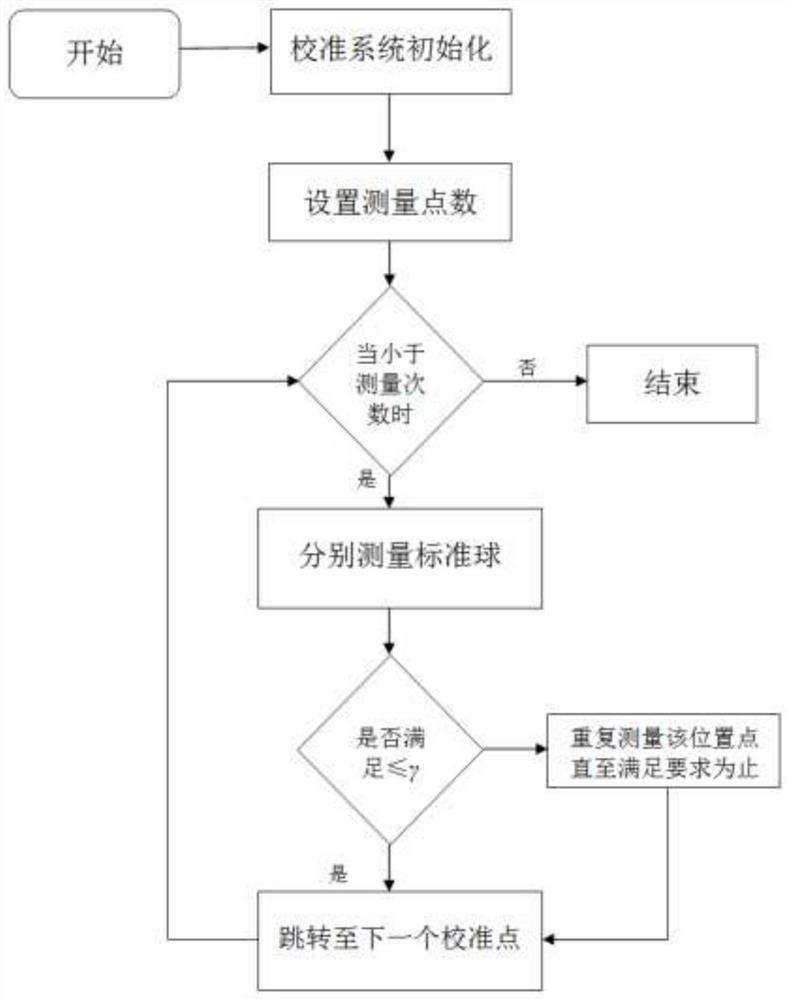

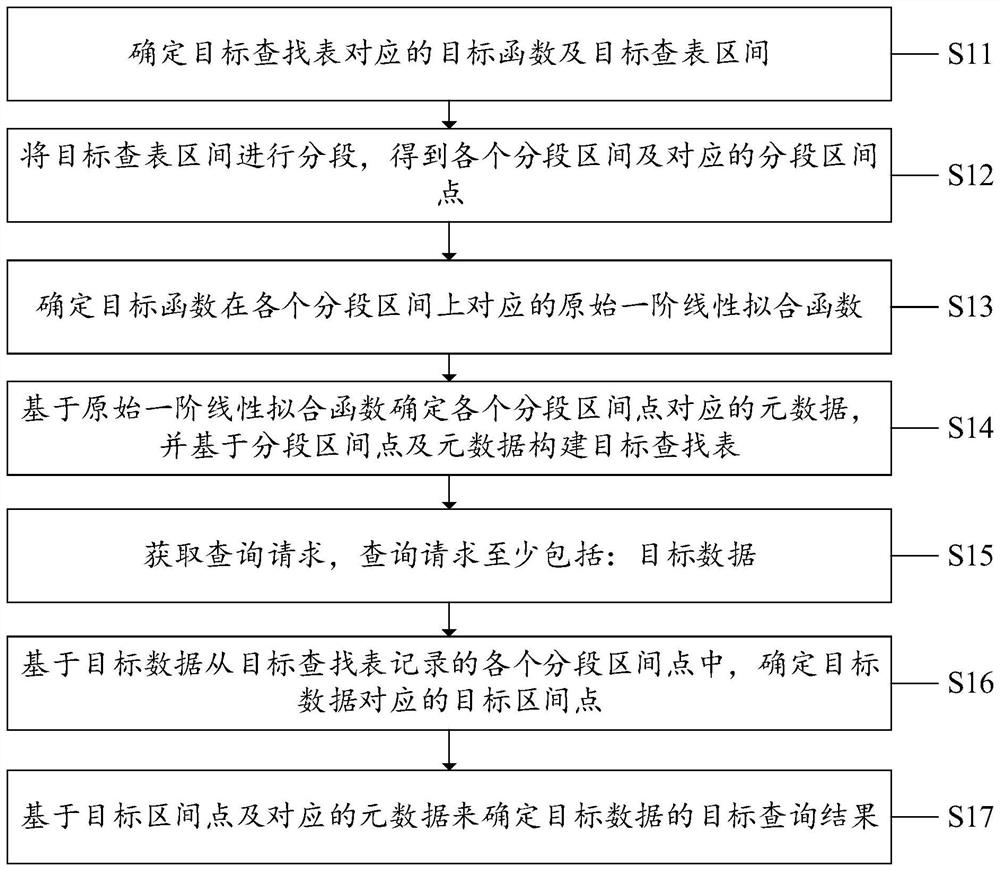

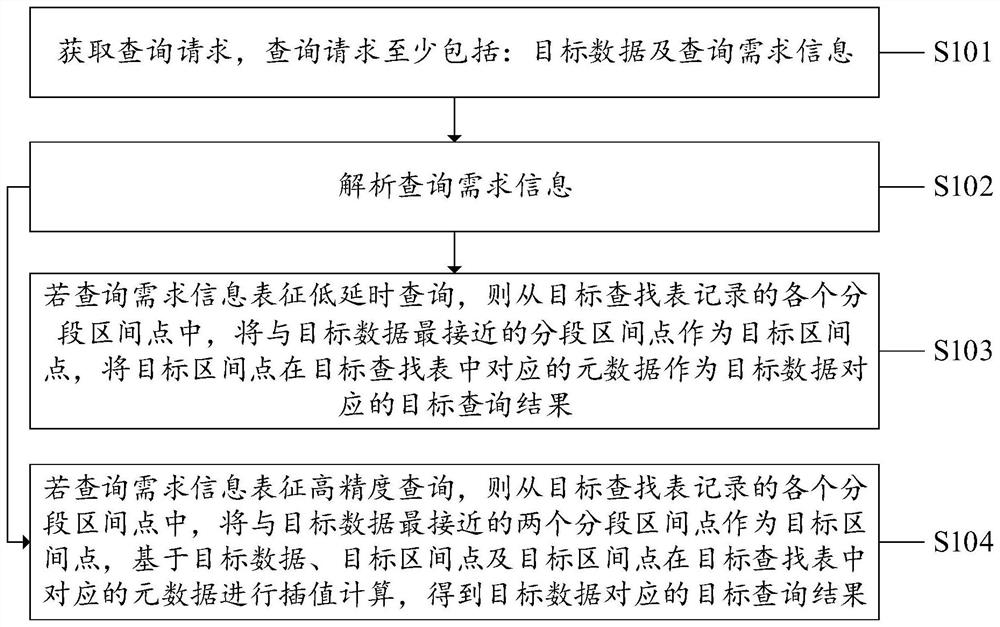

The invention discloses a data query method, system and device and a computer readable storage medium. The method comprises the steps of determining a target function and a target lookup table interval corresponding to a target lookup table; segmenting the target table lookup interval to obtain each segmented interval and a corresponding segmented interval point; determining an original first-order linear fitting function corresponding to the target function in each segment interval; determining metadata corresponding to each segment interval point based on the original first-order linear fitting function, and constructing a target lookup table based on the segment interval points and the metadata; obtaining a query request, wherein the query request at least comprises target data; determining a target interval point corresponding to the target data from each segmented interval point recorded in the target lookup table based on the target data; and determining a target query result of the target data based on the target interval point and the corresponding metadata. The metadata recorded in the target lookup table can be closer to the value of the segmentation interval point in the target function, and the data query accuracy is ensured.

Owner:SHENZHEN DAPU MICROELECTRONICS CO LTD