Novel improved butterfly unit algorithm structure for FFT processor chip design

A butterfly unit and chip design technology, applied in the field of FFT processors, can solve problems such as FFT processor condition limitations, achieve the effects of low hardware overhead, simplified control logic, and reduced hardware resource consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The following will clearly and completely describe the technical solutions in the embodiments of the present invention in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiment is only a mechanism embodiment of the present invention, not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

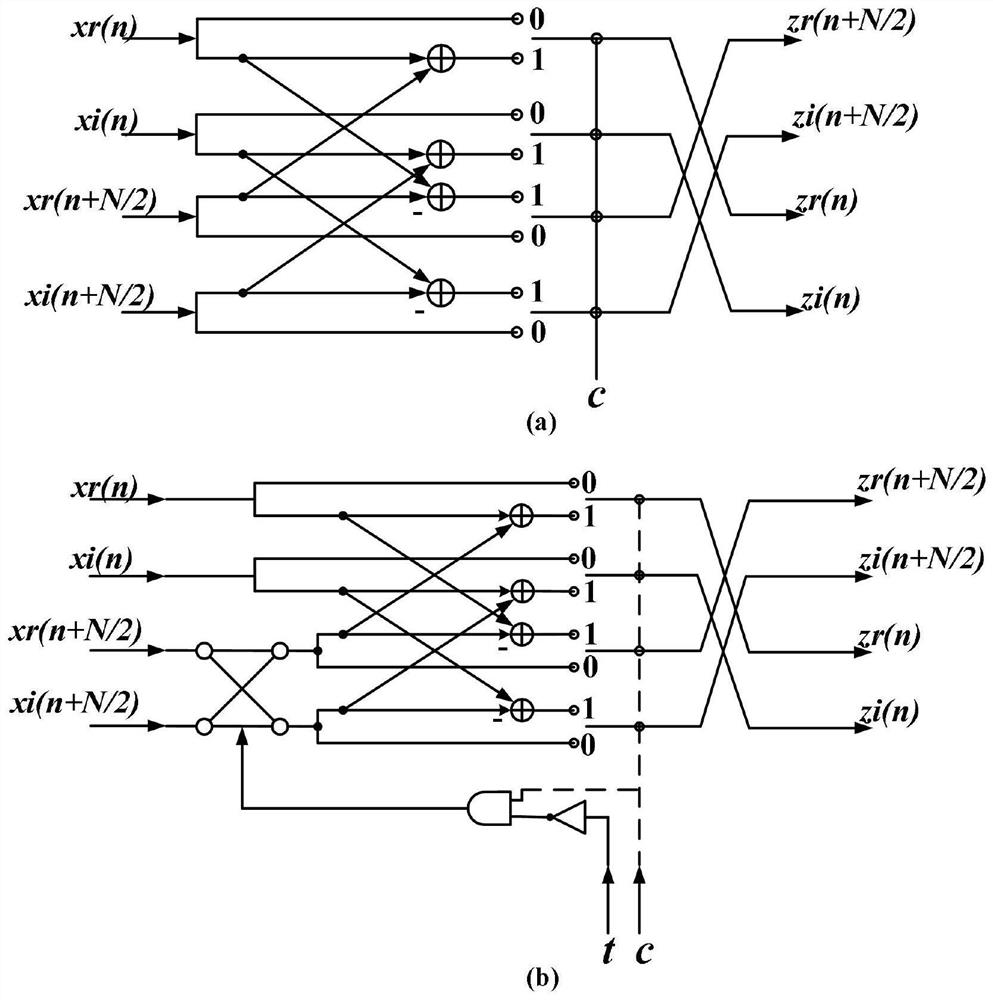

[0021] see Figure 1-Figure 4 , the present invention provides a technical solution: a new improved butterfly unit algorithm structure for FFT processor chip design:

[0022] Such as figure 1 As shown, it is the original butterfly unit structure, (a) is type I, (b) is type II, where xr(n) and xr(n+N / 2) are the real part of the input complex sequence, xi(n ) and xi(n+N / 2) are the imaginary part of the input complex sequence, zr(n) and zr(n+N / ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More