Chip packaging structure and electronic product

A chip packaging structure, chip packaging technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve problems such as easy tilt deformation, poor bonding of plastic sealing mold surface, complicated operation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

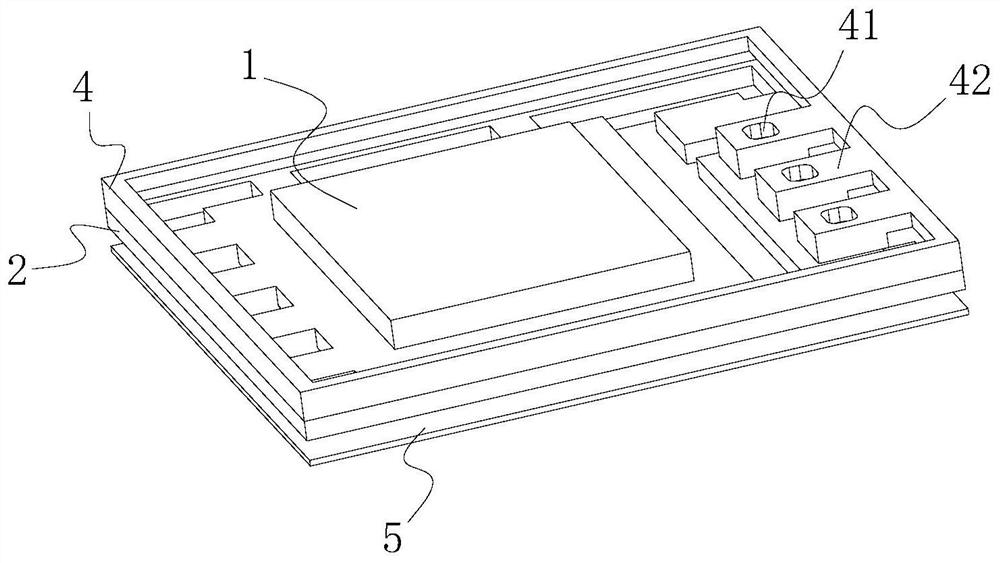

[0034] Specific embodiments of the present disclosure will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present disclosure, and are not intended to limit the present disclosure.

[0035] In this disclosure, unless stated otherwise, the orientation words used such as "upper and lower" refer to the upper and lower parts of the chip package structure installed in the electronic product and in the state of horizontal use, and the definitions of upper and lower The following are represented by A and B respectively, please refer to Image 6 shown. In addition, terms used such as "first", "second" and the like are only used to distinguish one element from another element, and do not have sequence or importance.

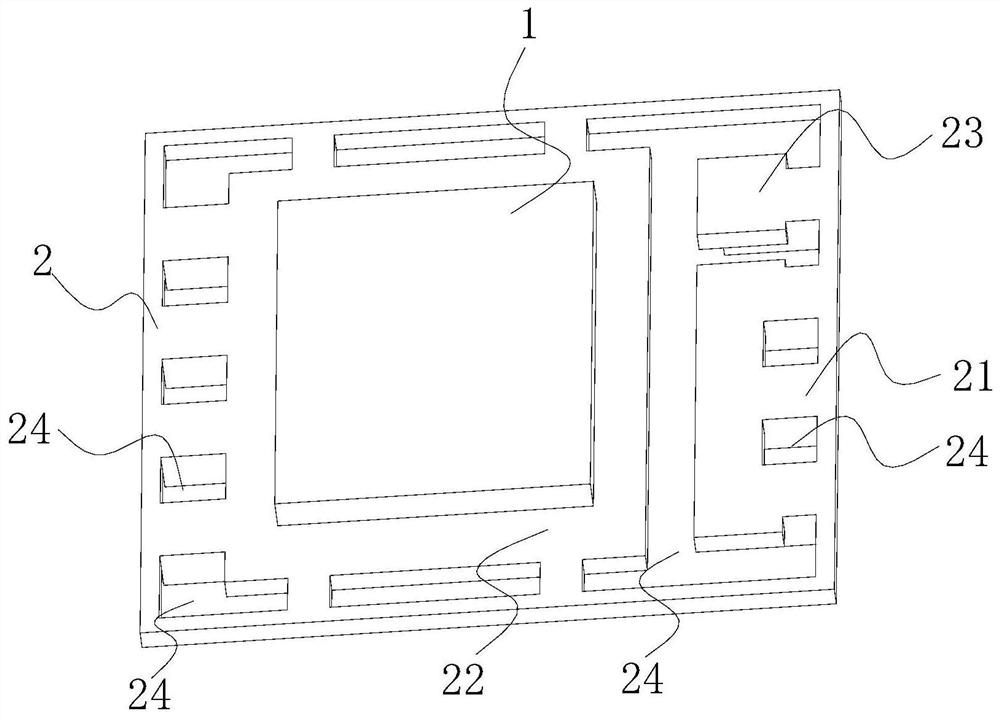

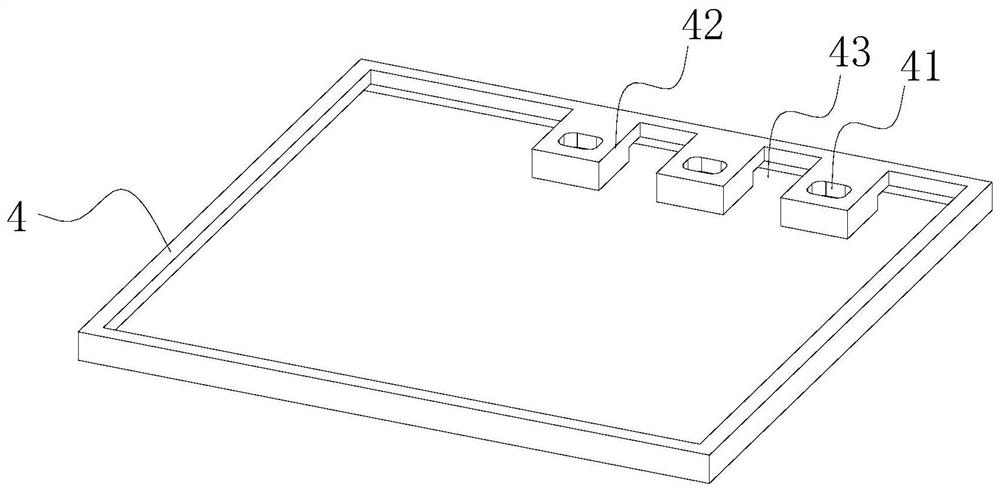

[0036] Such as Figure 1 to Figure 7 As shown, the present disclosure provides a chip packaging structure, which can be composed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More