MOS device and method for preventing parasitic transistor of MOS device from being turned on

A MOS device, body extraction technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of increased off-state leakage of MOS devices and reduced electrical characteristics of MOS devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

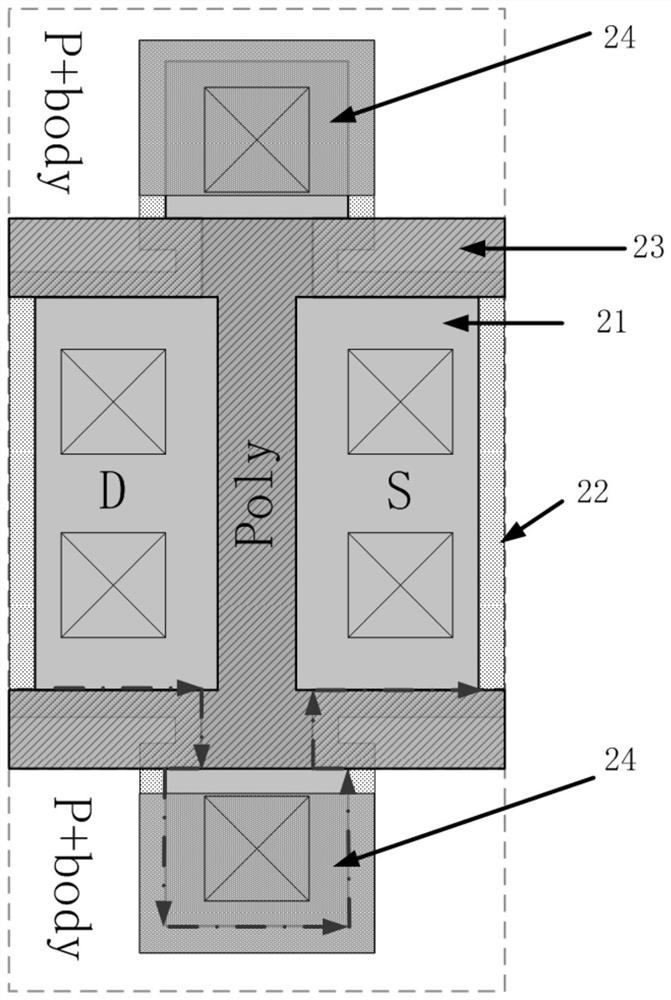

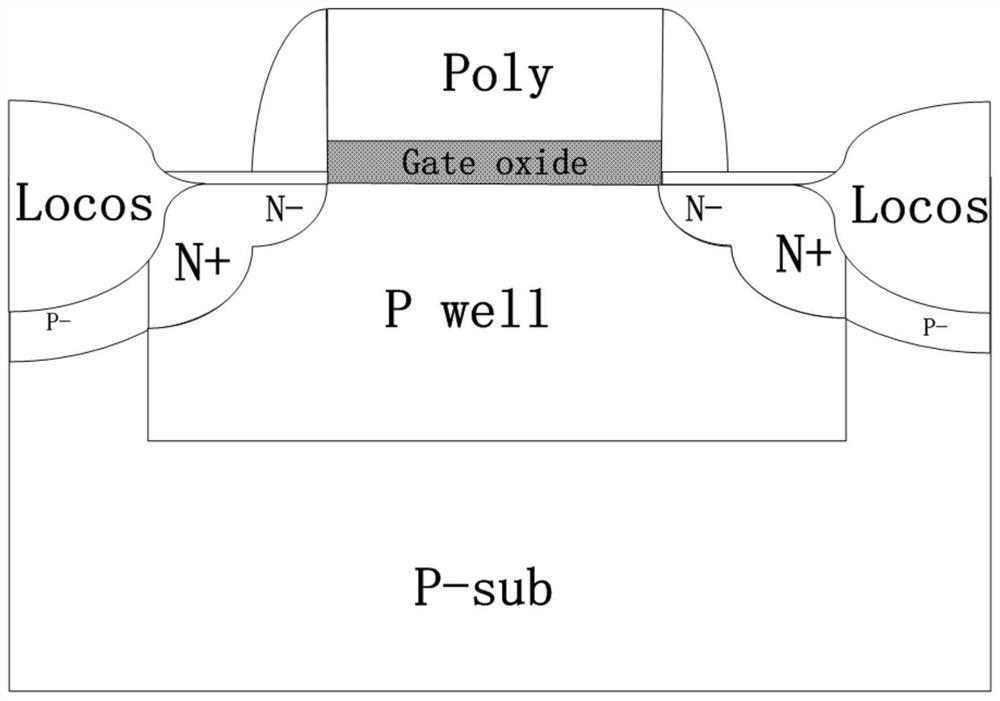

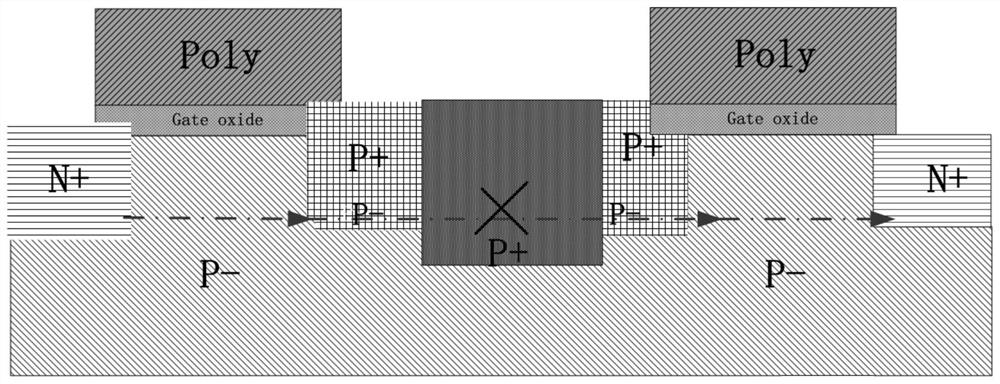

[0039] This embodiment provides a MOS device. The MOS device may include an NMOS device or a PMOS device. When the MOS device is an NMOS device, such as figure 1 and figure 2 As shown, the MOS device includes: a silicon substrate P-sub, a field oxygen region, an active region 21, a well region P well, a body lead-out region P+body, a gate dielectric layer Gate oxide, an H-type gate bar 23 and an active Field injection region 22 at region edge 21 .

[0040] Wherein, the active region 21 includes a source region S, a drain region D and a channel region, and the body lead-out region is arranged on one side in the width direction of the H-shaped gate bar;

[0041] An implantation window is set on the body lead-out region, and the interface region between the back of the field oxygen region and the silicon substrate is a heavily doped region; the doping concentration of the heavily doped region is higher than that of the well region; the secondary ion implantation The depth is g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More