Circuit structure and method for preventing I2C interface from mistakenly waking up SOC system

A technology with circuit structure and interface errors, applied in the direction of electrical digital data processing, instruments, etc., can solve the problem of chip wake-up error, waste of energy and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

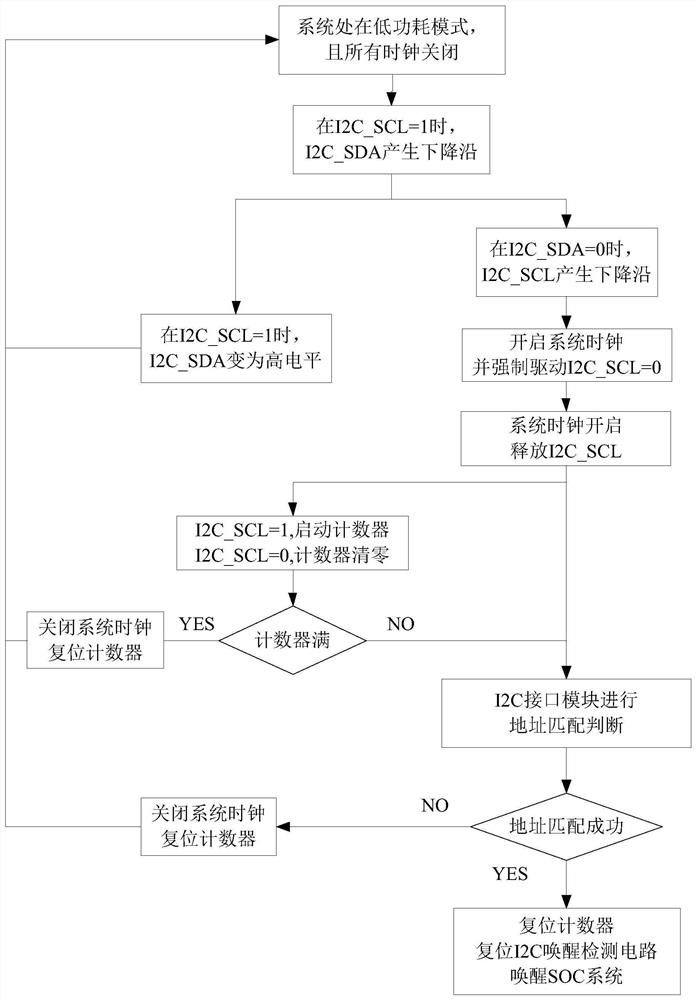

[0025] combine figure 1 , a schematic diagram of the circuit structure of the present invention, illustrating the circuit structure of the present invention.

[0026] The I2C bus signal (101) conforms to the standard I2C bus protocol, and is directly connected to the interface of the host.

[0027] Glitch filtering circuit (108), including I2C_SDA falling edge detection register (102), I2C_SDA rising edge detection register (103) and I2C_SCL falling edge detection register (104), respectively detects the rising edge of I2C_SDA, I2C_SDA falling edge and I2C_SCL falling edge.

[0028] The output end of the above-mentioned I2C_SDA falling edge detection register (102) is respectively connected to the reset end of the I2C_SCL falling edge detection register (104) and the reset end of the rising edge detection register (103) of I2C_SDA.

[0029] The output of the rising edge detection register (103) of I2C_SDA is connected to the reset terminal of the I2C_SCL falling edge detecti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com