A method of fabricating super junction mosfet with enhanced uis capability

A manufacturing method and capability technology, applied in the field of super-junction MOSFET manufacturing to improve UIS capability, can solve problems such as smaller injection window, unsatisfactory P+deepbody area, and limited super-junction MOSFET UIS capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention.

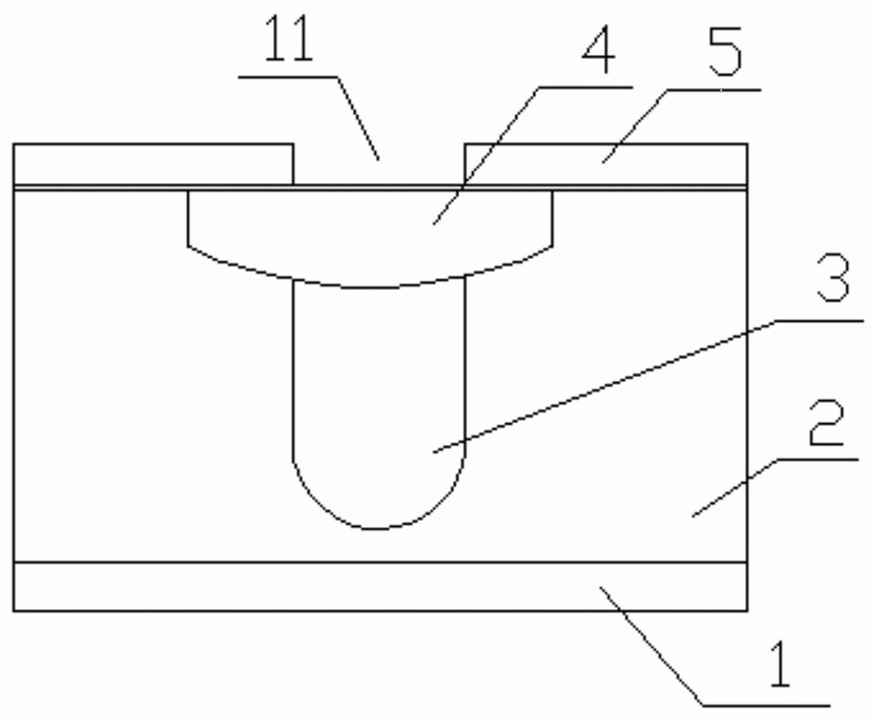

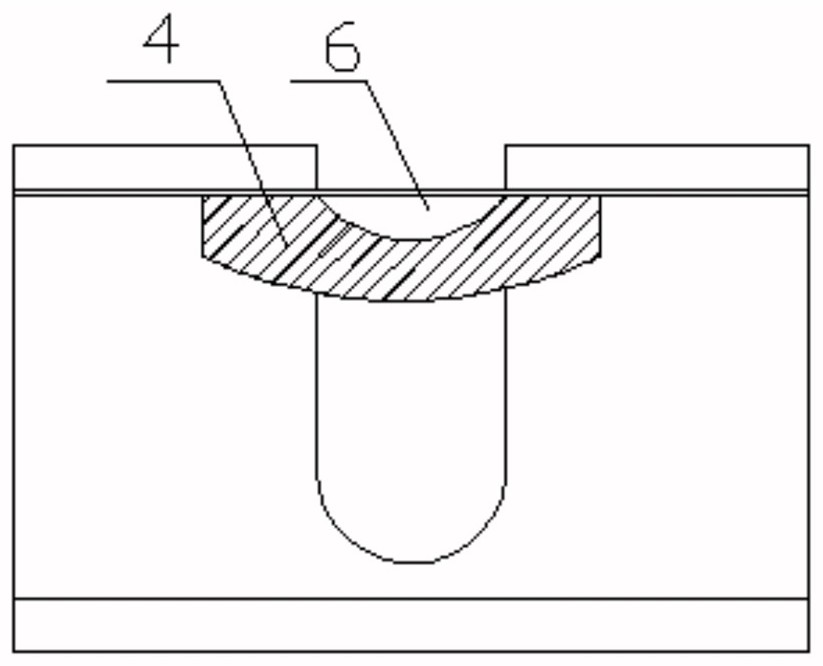

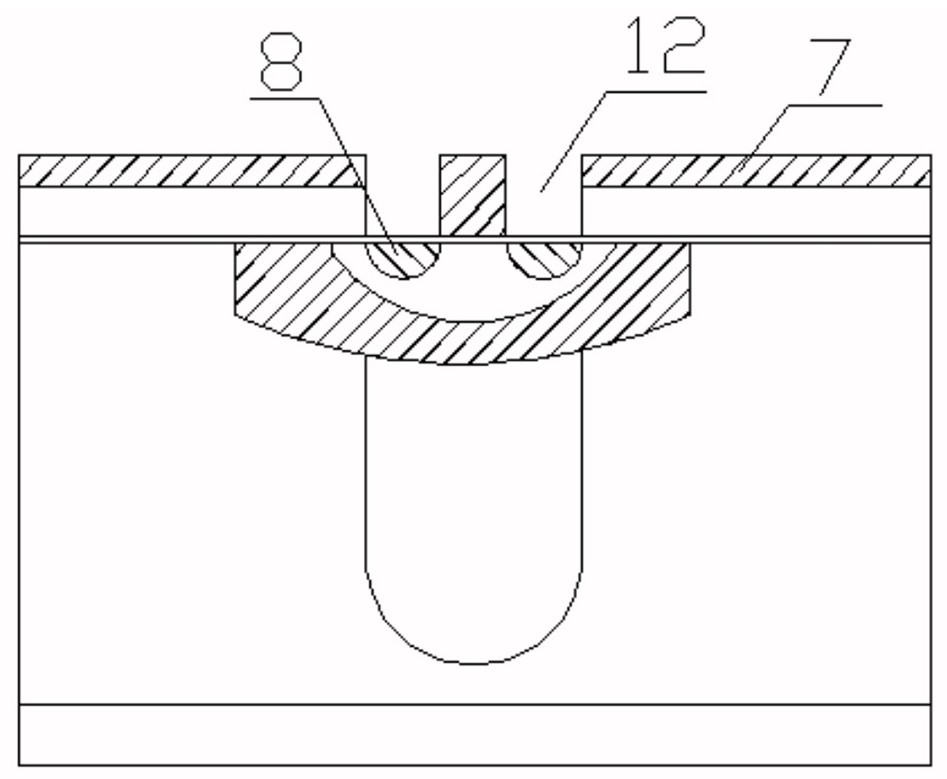

[0029] This embodiment discloses a method for manufacturing a super-junction MOSFET with improved UIS capability, in which part of the content of this embodiment is omitted for the conventional process steps of manufacturing a super-junction MOSFET in the prior art, and this embodiment only focuses on the process related to the purpose of the invention The key points of the link are explained. The super-junction MOSFET mentioned in this embodiment is an example of a planar gate deep-trench super-junction MOSFET, and its manufacturing process is as follows: Figure 5 As shown, the device structure formed at different stages in the fabrication process exhibits the Figure 1 to Figure 4 shown.

[0030] First select the semiconductor substrate 1, and then form an epitaxial layer 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com