Substrate preparation method, substrate structure, chip packaging method and chip packaging structure

A substrate preparation and substrate technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problem that the depth of opening is not easy to control, affects the yield of chip packaging structure, and easily damages the conductive circuit of the chip To achieve the effect of improving the stability of interface bonding, improving the efficiency of opening holes, and reducing warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0104] The chip packaging method of this embodiment includes the following steps:

[0105] S10. Prepare the first sub-substrate:

[0106] S10a, providing a first glass substrate 11, pasting a first photosensitive dry film on one side of the first glass substrate 11, forming several windows after exposure and development;

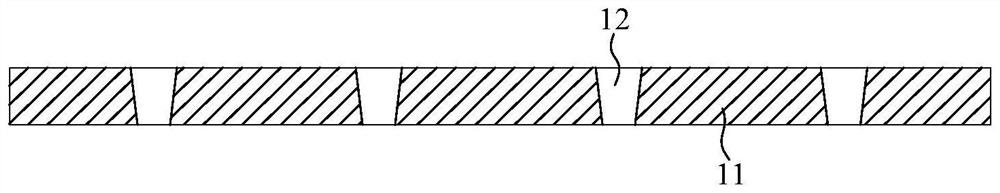

[0107] S10b. Perform laser focus modification on the first glass substrate 11 exposed to the window, and then use a hydrofluoric acid solution to etch the laser focus modification area to obtain a TGV through hole 12 penetrating through the first glass substrate 11, refer to figure 1 ;

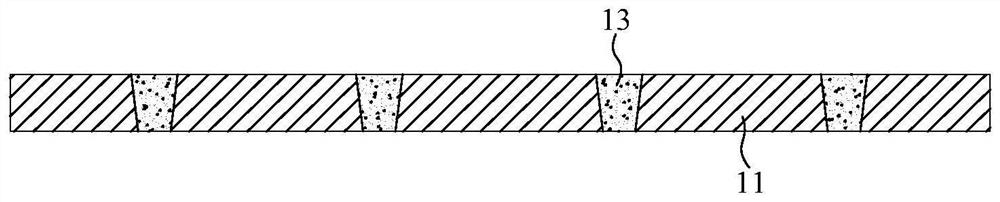

[0108] S10c, making the first conductive post 13 in the TGV through hole 12 by electroplating, and making the two ends of the first conductive post 13 respectively flush with both sides of the first glass substrate 11, and then removing the remaining first photosensitive dry film ,refer to figure 2 ;

[0109] S20. Prepare the second sub-substrate:

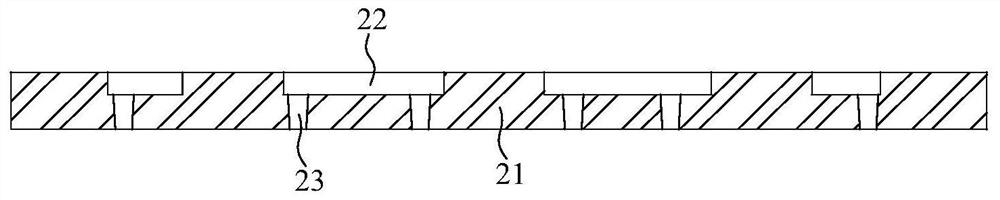

[0110] S20a, provide...

Embodiment 2

[0139] The chip packaging method of this embodiment is basically the same as the first embodiment above, the difference lies in the substrate preparation method, and the substrate preparation method specifically includes the following steps:

[0140] S10. Prepare the first sub-substrate:

[0141] S10a, providing a first glass substrate 11, pasting a first photosensitive dry film on one side of the first glass substrate 11, forming several windows after exposure and development;

[0142] S10b. Perform laser focus modification on the first glass substrate 11 exposed to the window, and then use ammonium bifluoride solution to etch the laser focus modification area to obtain a TGV through hole 12 that runs through the first glass substrate 11. Refer to figure 1 ;

[0143] S10c, making the first conductive column 13 in the TGV through hole 12 by electroplating, and making one end surface of the first conductive column 13 flush with one side of the first glass substrate 11, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More