Semiconductor package structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor device, semiconductor/solid-state device components, etc., can solve the problem of the increase of the residual copper ratio of the substrate, the mismatch of the thermal expansion coefficient between the substrate and the chip, and the overall semiconductor packaging structure. Volume increase and other issues to achieve the effect of reducing volume and avoiding expansion and contraction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

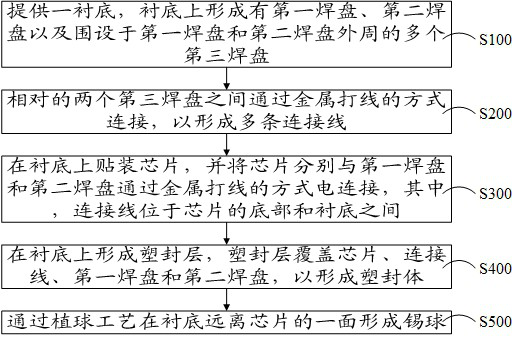

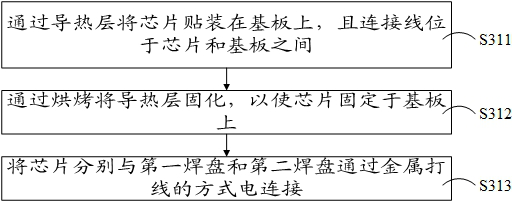

[0044] Please refer to figure 1 , the present embodiment provides a manufacturing method of a semiconductor package structure, the manufacturing method comprising:

[0045] S100 , providing a substrate on which a first pad 11 , a second pad 12 and a plurality of third pads 13 surrounding the first pad 11 and the second pad 12 are formed.

[0046] Wherein, both the first pad 11 and the second pad 12 are functional bonding pads of the chip 20 , and are used to realize the functional connection of the chip 20 . It should be understood that the first pad 11 and the second pad 12 should be electrically connected to corresponding functional pads on the chip 20 in one-to-one correspondence.

[0047] In addition, it should be noted that the number of the first bonding pads 11 and the second bonding pads 12 should be the same as the number of the corresponding functional bonding pads on the chip 20 , and there is a one-to-one correspondence.

[0048] The third pad 13 surrounds the ou...

no. 2 example

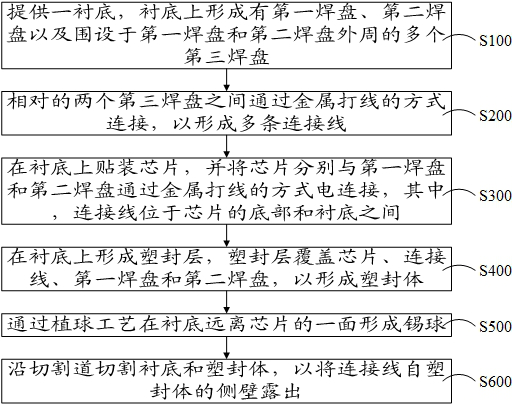

[0074] Compared with the first embodiment, the present embodiment differs in that, in the present embodiment, the above-mentioned plurality of third pads 13 are all provided on the dicing lines of the substrate (specifically, the substrate 10A).

[0075] In this way, please combine the reference image 3 , optionally, after forming the solder balls 40 on the side of the substrate away from the chip 20 through the ball planting process, the method further includes:

[0076] S600 , cutting the substrate and the molded package 30 along a dicing line, so as to expose the connecting wire 14 from the sidewall of the molded package 30 .

[0077] Such as Figure 7 As shown, after cutting the substrate and the plastic package 30 along the dicing line, the following can be obtained Figure 10 In the shown structure, at this time, a plurality of connecting wires 14 will be exposed from the side wall of the plastic package 30, thereby exposing the connecting wires 14 on the peripheral w...

no. 3 example

[0082] Compared with the first embodiment, this embodiment differs in that the lead frame 10B is used as the substrate in this embodiment (the substrate 10A is used as the substrate in the first embodiment).

[0083] In this embodiment, the substrate is a lead frame 10B, and a hollow area 15 is formed in the central area of the lead frame 10B by etching, and a plurality of third bonding pads 13 are arranged around the hollow area 15 . Please refer to Figure 13 as shown, Figure 13 What is shown is a schematic structural view of the lead frame 10B.

[0084] It should be noted that the hollow area 15 is formed in the central area of the lead frame 10B by etching, which may be by etching off the base island of the existing lead frame (the area produced after the base island is etched is the above-mentioned The hollowed-out area 15 ), thereby forming the lead frame 10B without base islands.

[0085] Please refer to Figure 11 Optionally, before the two opposite third pads...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More