Method for forming semiconductor device

A semiconductor and dielectric layer technology, applied in the field of semiconductor device formation, can solve the problems of increasing contact resistance and inability to fully conform to the

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

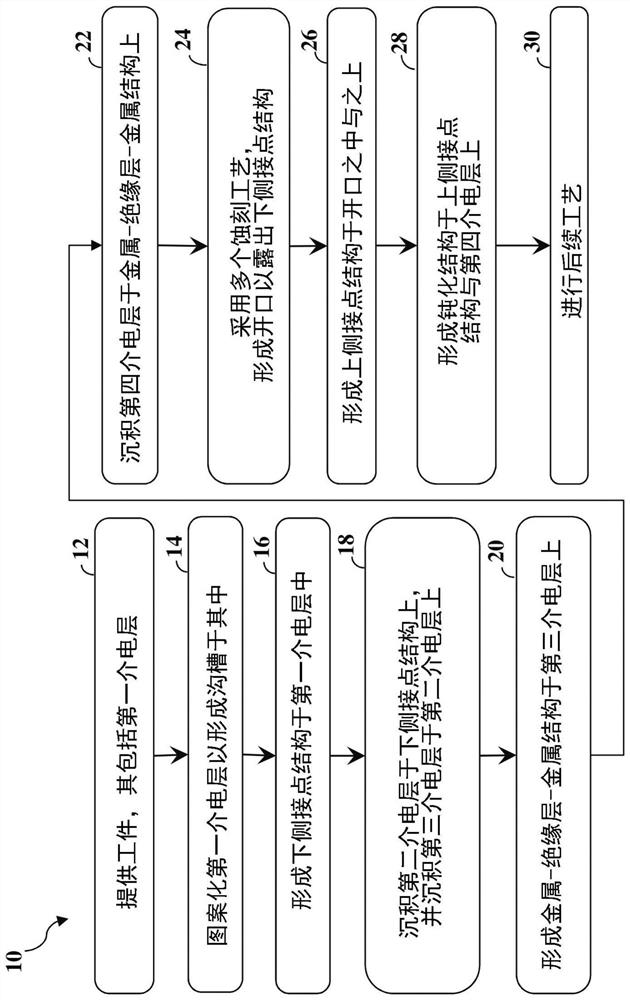

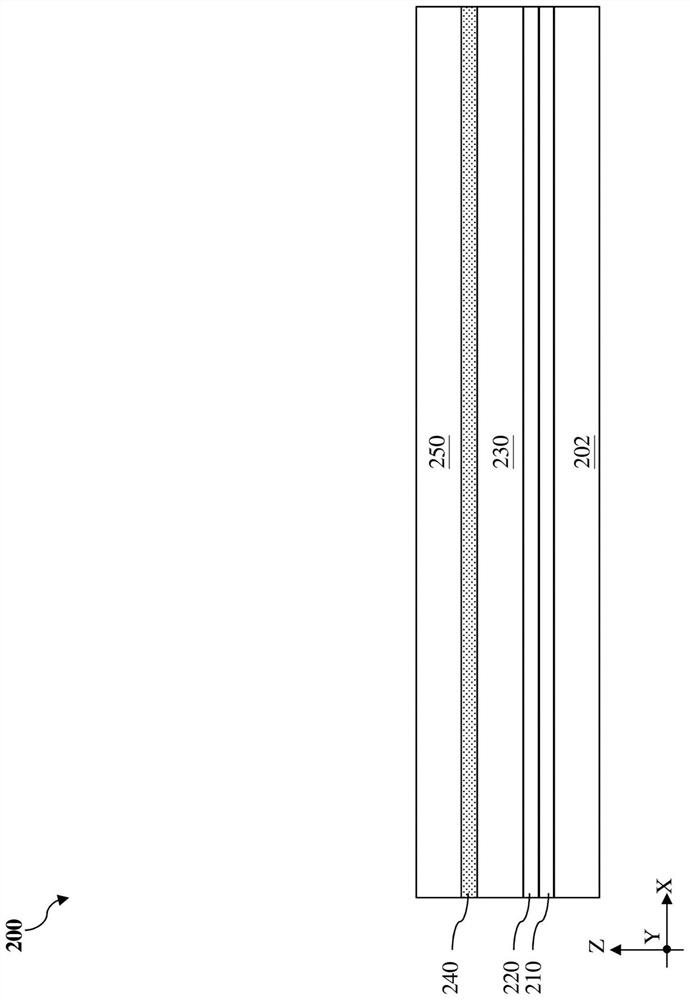

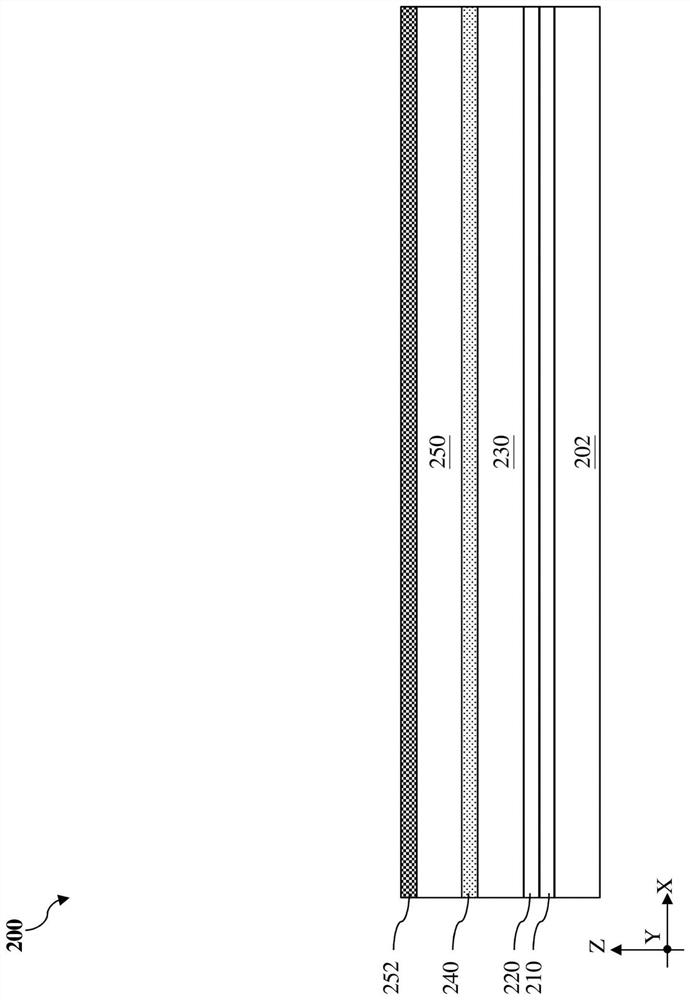

[0048] The following detailed description can be accompanied by accompanying drawings to facilitate understanding of various aspects of the present invention. It is worth noting that various structures are used for illustration purposes only and are not drawn to scale, as is the norm in the industry. In fact, the dimensions of the various structures may be arbitrarily increased or decreased for clarity of illustration.

[0049] Different embodiments or examples provided in the following content can implement different structures of the embodiments of the present invention. The examples of specific components and arrangements are used to simplify the disclosure and not to limit the invention. For example, the statement that the first component is formed on the second component includes that the two are in direct contact, or there are other additional components interposed between the two instead of direct contact. In addition, various examples of the present invention may rep...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More