An antifuse memory unit and its data read and write circuit

A storage unit and anti-fuse technology, applied in information storage, static memory, read-only memory, etc., can solve the problems of lower reading speed and reliability, large area of anti-fuse memory, large on-resistance, etc., to achieve Improve data reading speed, reduce design difficulty, and reduce the effect of on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

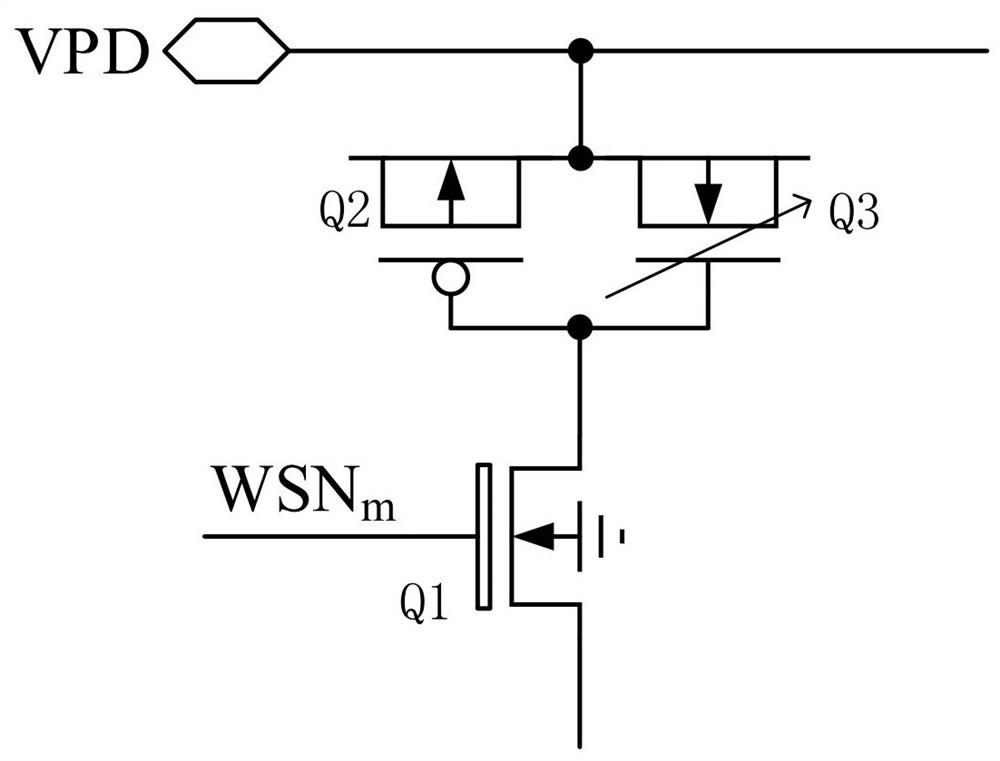

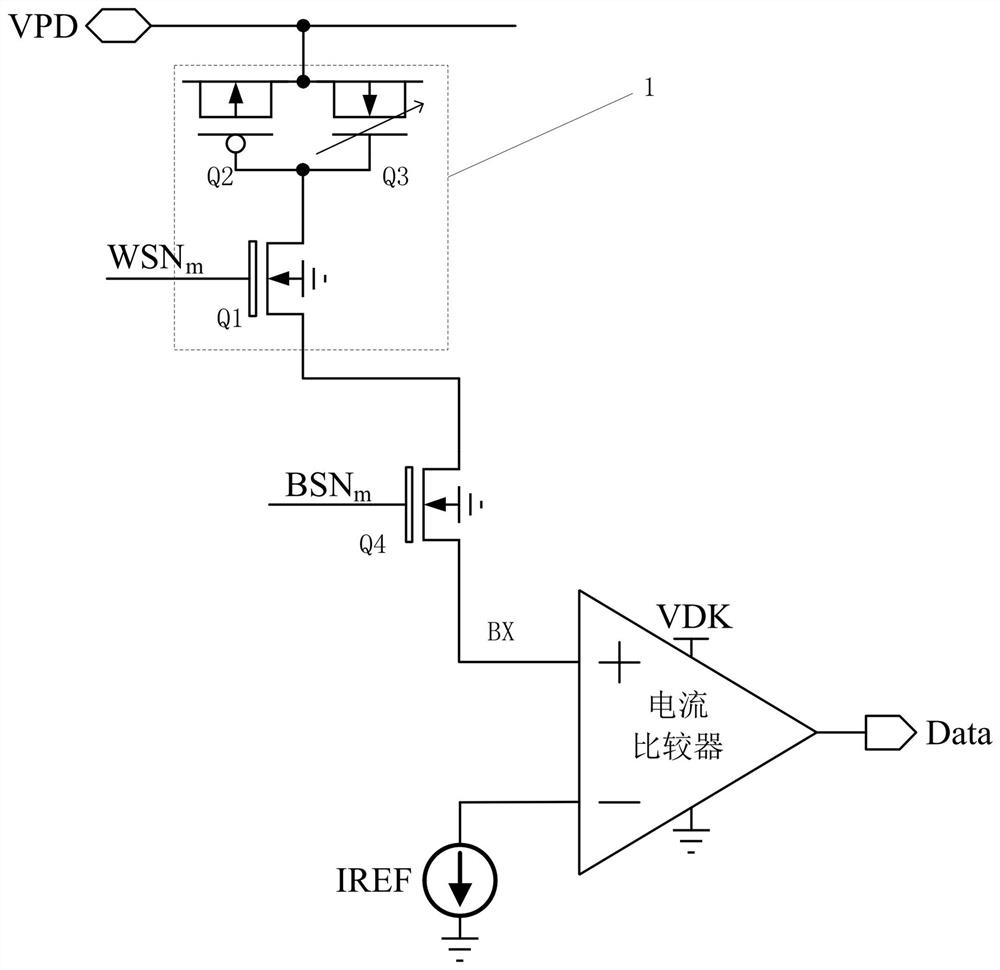

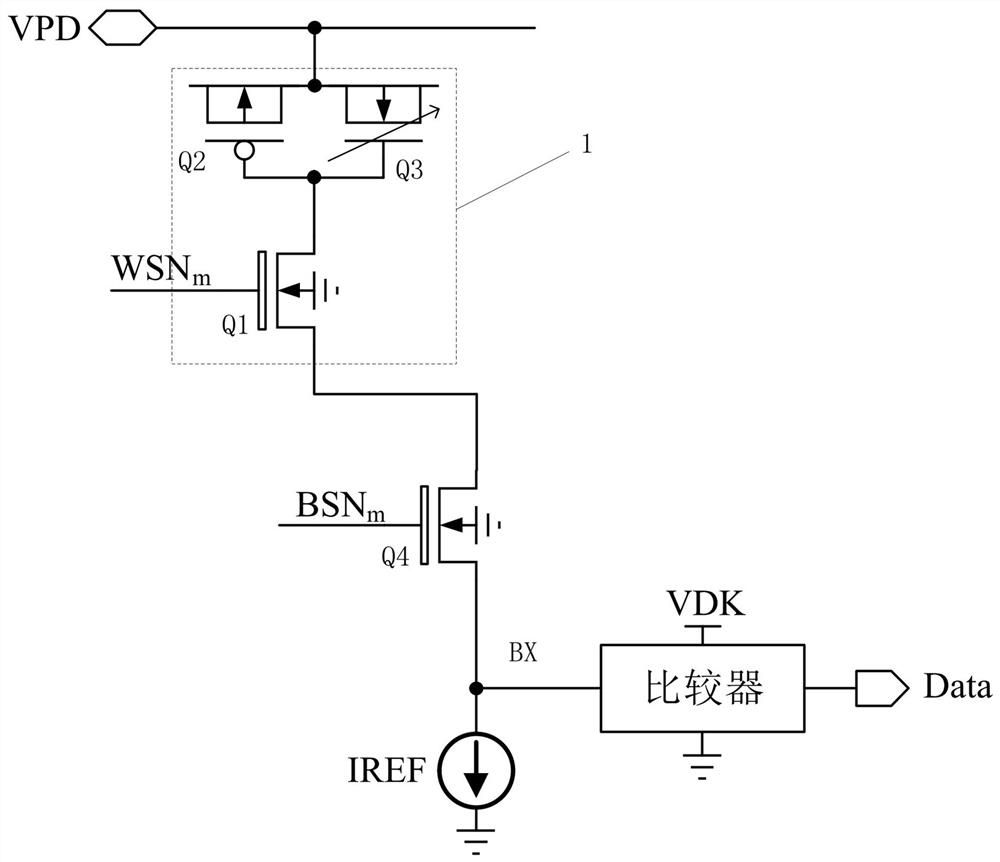

[0042] Such as figure 1 As shown, an antifuse memory unit includes a first NMOS transistor Q1, a PMOS transistor Q2 and a capacitor transistor Q3, an N well, a drain electrode of the PMOS transistor, a source electrode, a substrate, and a drain electrode, the source electrode of the capacitor transistor, The substrates are all connected to the controllable power supply VPD. The gates of the PMOS transistor and the capacitor transistor are connected to the drain of the first NMOS transistor, and the gate of the first NMOS transistor is input with a first strobe signal WSNm. The first NMOS tube Q1 adopts IO devices or 2.5V~5V high-voltage process devices, such as 2.5V / 3.3V / 5V, which can withstand the high programming voltage during occasional programming for a short time. The PMOS tube and capacitor tube use CORE core devices or 0.7V~1.8V low-voltage process devices, such as 0.9V / 1.0V / 1.2V / 1.5V / 1.8V.

[0043] From the layout point of view, as Figure 4As shown in , for ease o...

Embodiment 2

[0057] The difference between Embodiment 2 and Embodiment 1 is that in the read-write circuit of the antifuse memory unit, the source BX point of the second NMOS transistor is also connected with a pull-up transistor and a pull-down transistor. To write a valid value memory cell, except that the first strobe signal WSNm and the second strobe signal BSNm of the target cell are both set to high level, the BX point is pulled down to 0V low potential; Or write to a memory cell with an invalid value, pull up the BX point to a high potential such as 4.3V (VPD-0.7V). All the other parts are the same as the first embodiment.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More