Memory device and manufacturing method thereof

A technology of memory element and manufacturing method, which is applied in the fields of semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of poor electrical performance of memory cells, increased distribution width of memory cells, unstable gate coupling rate, etc. , to achieve stable gate coupling rate, narrow distribution width, and avoid bird's beak effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

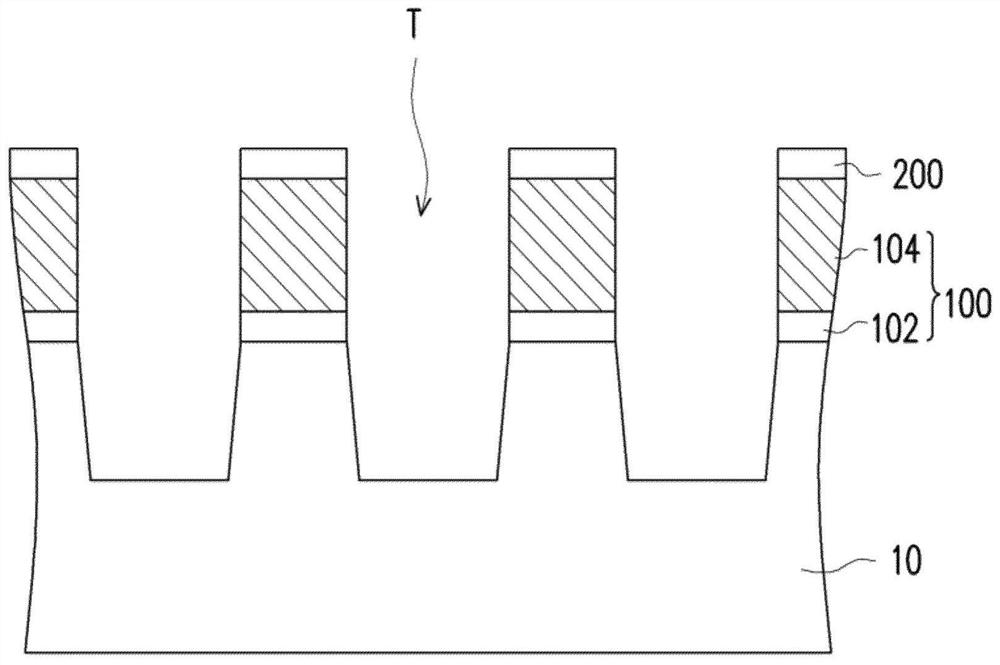

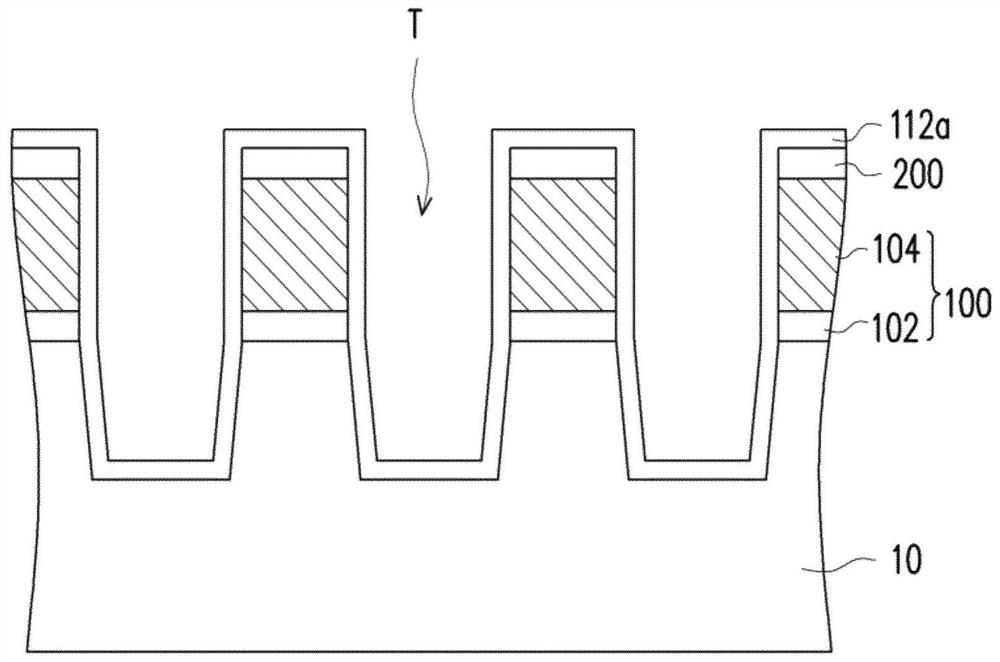

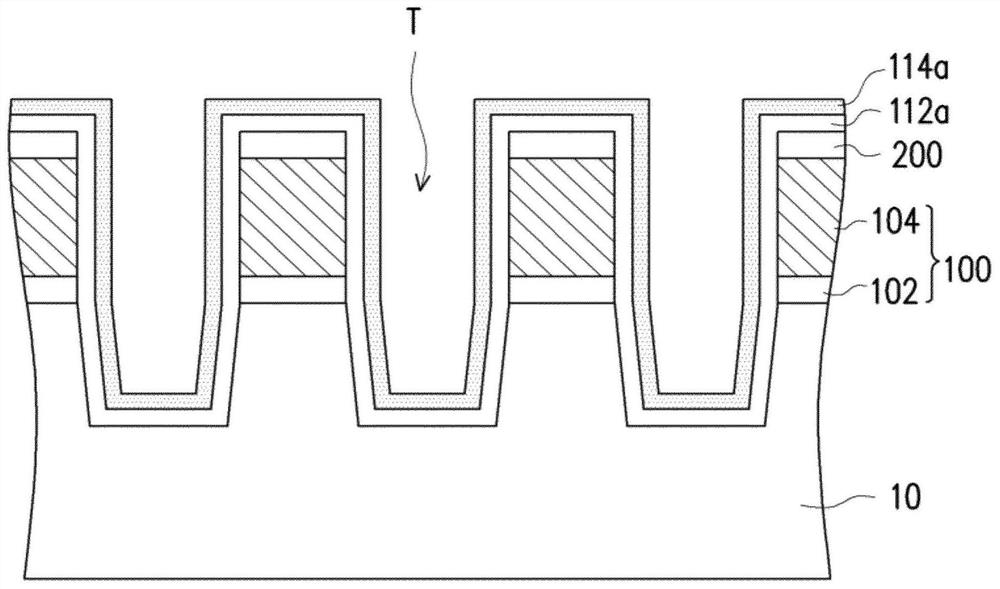

[0050] Figure 1A to Figure 1J is a schematic diagram of a method of manufacturing a memory element according to an embodiment of the present invention.

[0051] Please refer to Figure 1A , firstly, a substrate 10 is provided. The substrate 10 is, for example, a semiconductor substrate, a semiconductor compound substrate, or a semiconductor over insulator (SOI) on a dielectric layer. The aforementioned semiconductors are, for example, atoms of group IVA, such as silicon or germanium. The aforementioned semiconductor compound is, for example, a semiconductor compound formed of atoms of group IVA, such as silicon carbide or silicon germanium, or a semiconductor compound formed of atoms of group IIIA and group VA, such as gallium arsenide.

[0052] Please continue to refer to Figure 1A, and then, forming a plurality of stacked structures 100 on the substrate 10 . In this embodiment, each stack structure 100 includes a tunneling dielectric layer 102 and a floating gate 104 ....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More