Delay modulation method based on ferroelectric transistor

A technology of ferroelectric transistors and modulation methods, which is applied in digital memory information, instruments, biological neural network models, etc., can solve the problems of high hardware cost and power consumption, and achieve the effect of reducing hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be further elaborated below through specific embodiments in conjunction with the accompanying drawings.

[0023] This embodiment uses Hf 0.5 Zr 0.5 o 2 Ferroelectric materials realize conventional ferroelectric transistors FeFETs.

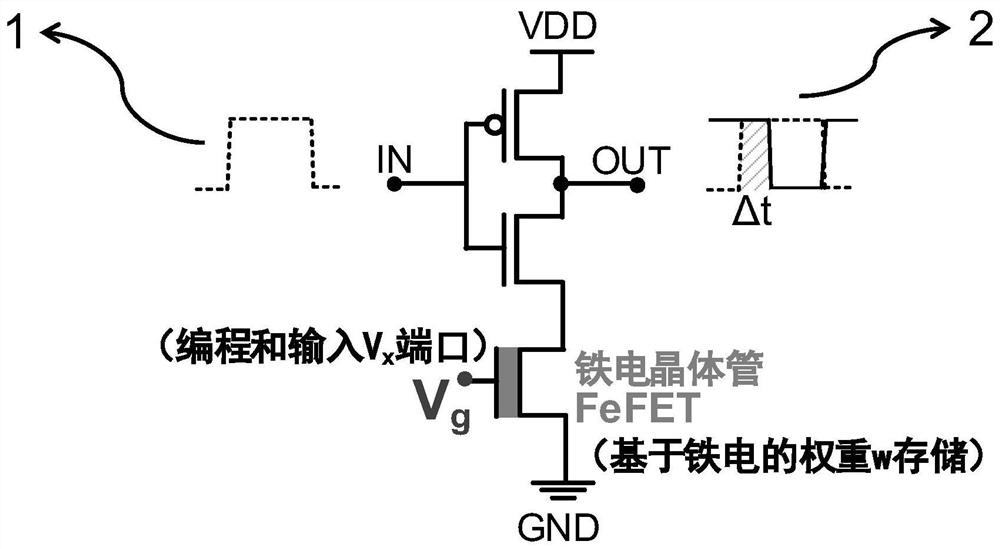

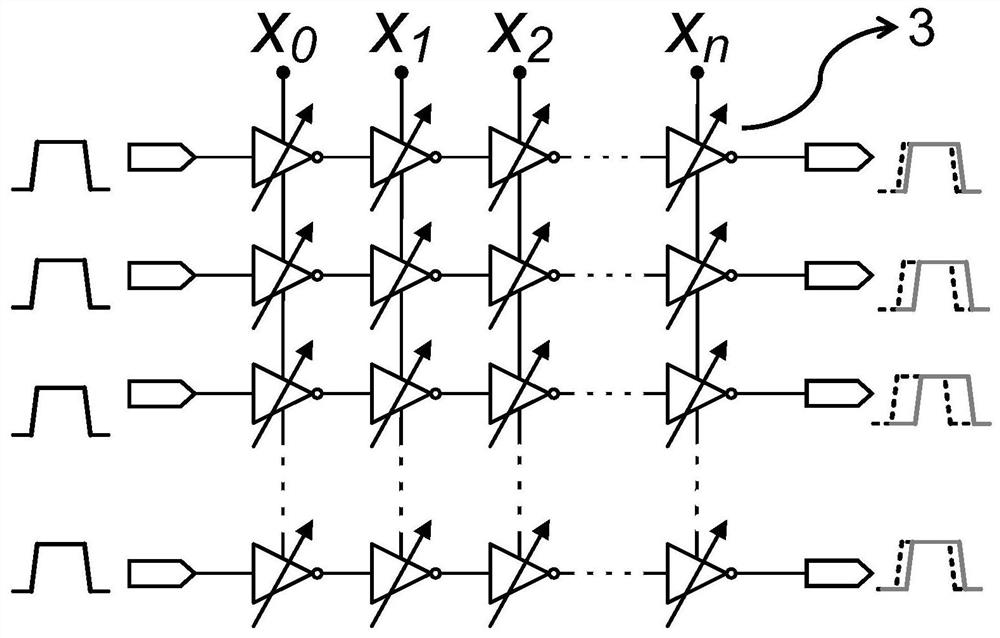

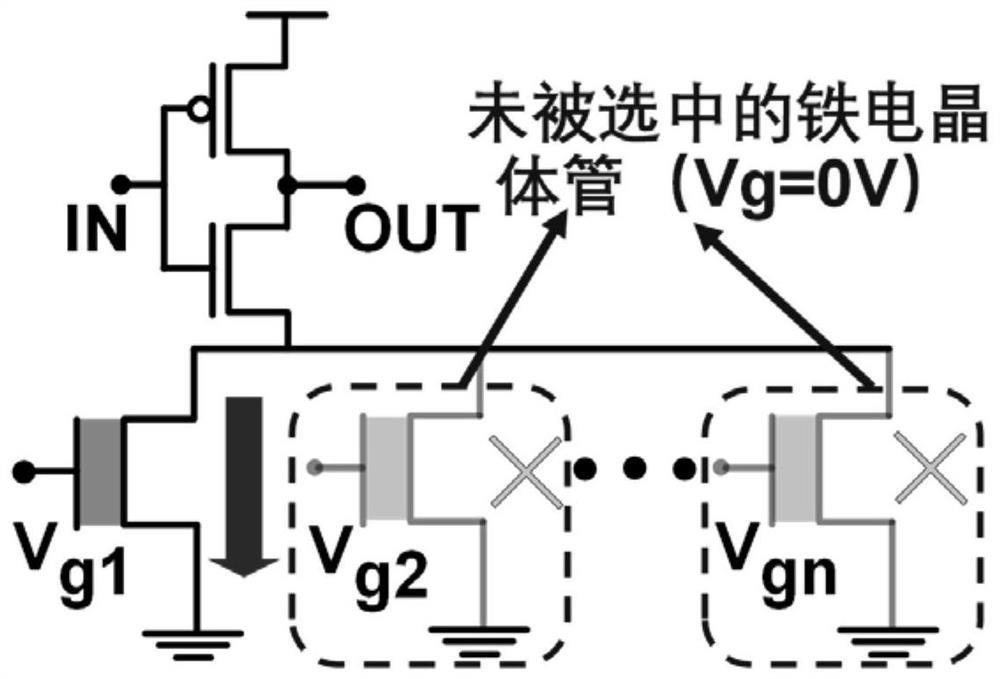

[0024] like figure 1 As shown, the present embodiment is a delay modulation unit circuit based on ferroelectric transistors, including FeFET, NMOS and PMOS; wherein NMOS and PMOS form an inverter structure; the drain end of FeFET is connected to the source end of inverter NMOS, and the FeFET The source of the source is connected to GND, and the gate is used as the weight programming port and the input port of the neural network; in the programming weight stage, the ferroelectric coercive voltage (V C ) programming voltage acts on the FeFET gate to adjust the threshold voltage of the FeFET, that is, the weight; in the time domain calculation stage, the neural network input x takes the voltage V x Acting on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More