Power semiconductor device and manufacturing method thereof

A technology of power semiconductors and manufacturing methods, which is applied to semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of low utilization rate of silicon carbide chips, large loss of freewheeling diodes, and low channel mobility, etc., to avoid dual Extremely degraded effect, improved surge capability, enhanced robustness effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0059] Step 1: Using an epitaxial process, an N-type epitaxial layer 2 is formed on a silicon carbide N-type substrate 1, wherein the resistivity of the N-type substrate 1 is 0.01-0.03Ω.cm, and the thickness is 200-400 μm. The doping concentration of layer 2 is 5e14~5e16cm -3 ;

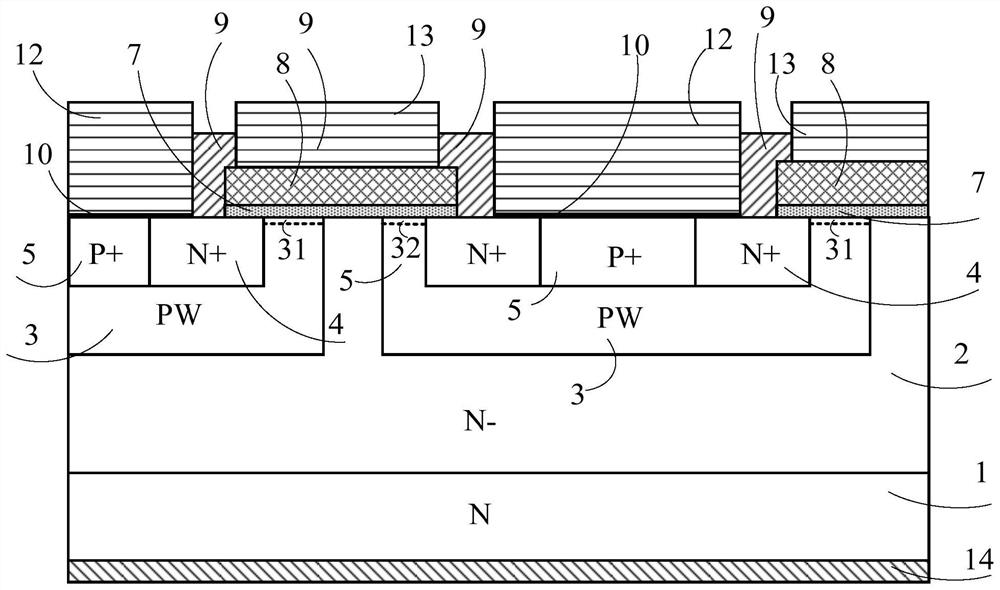

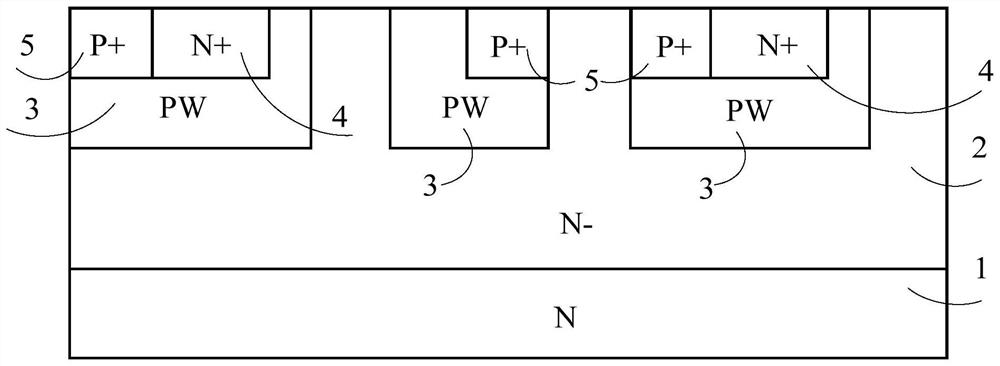

[0060] Step 2: Form a P base region 3 above the N-type epitaxial layer 2 by using photolithography and ion implantation technology, the junction depth of the P base region 3 is 0.6-1.5um, and the peak doping concentration is 1e18-5e19cm -3 , forming an N+ source region 4 in the P base region 3, with a junction depth of 0.2-0.5um and a peak doping concentration of 5e18-5e20cm -3 , forming a P+ source region 5 in the P base region 3, the junction depth is 0.2-0.5um, and the doping concentration is 5e18-5e20cm -3 , and activate the impurities in the above-mentioned implanted regions by high-temperature annealing, such as image 3 shown;

[0061] Step 3: Deposit a layer of insulating dielectric materi...

Embodiment 2

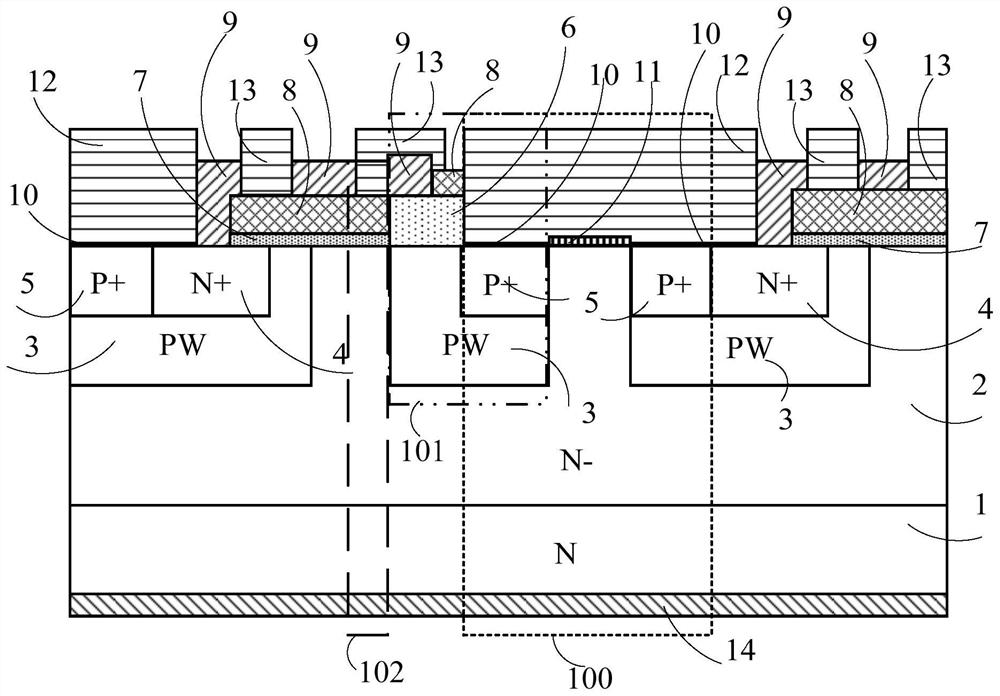

[0071] Same as Embodiment 1, all utilize MOSFET half-cells to integrate MPS ( Figure 8 Middle dotted line frame 200); The difference from Embodiment 1 is that by removing a piece of polysilicon 8 ( Figure 8 There is no polysilicon 8 in the dotted line frame 201) and the size of the working gate is reduced, the gate charge is reduced, and the PMOS capacitor is not formed in the MPS part, as Figure 8 shown.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Knot deep | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More