Semiconductor power device and preparation method thereof

A power device and semiconductor technology, applied in the field of semiconductor power devices and their preparation, can solve the problems of SGTMOS incompatibility, high manufacturing cost, and difficulty in integration, and achieve the effects of easy integration, easy process compatibility, and reduced on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

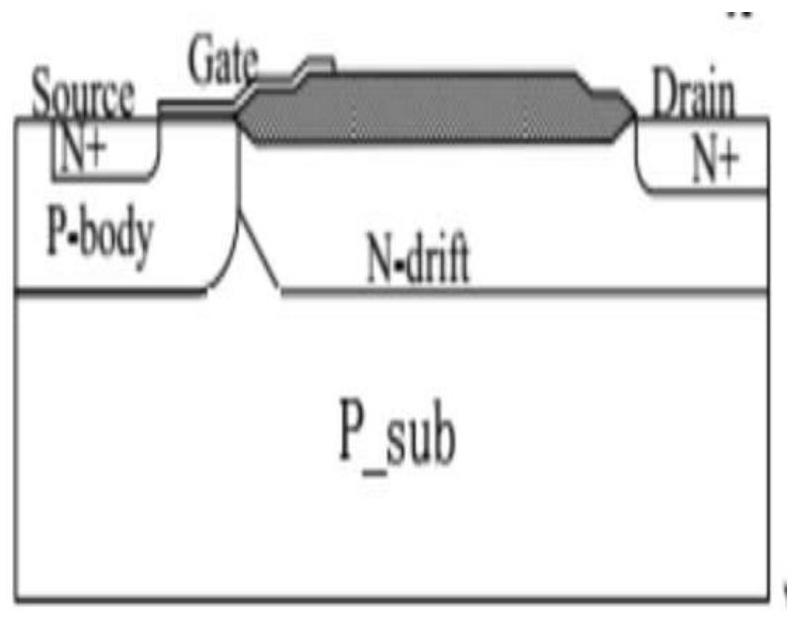

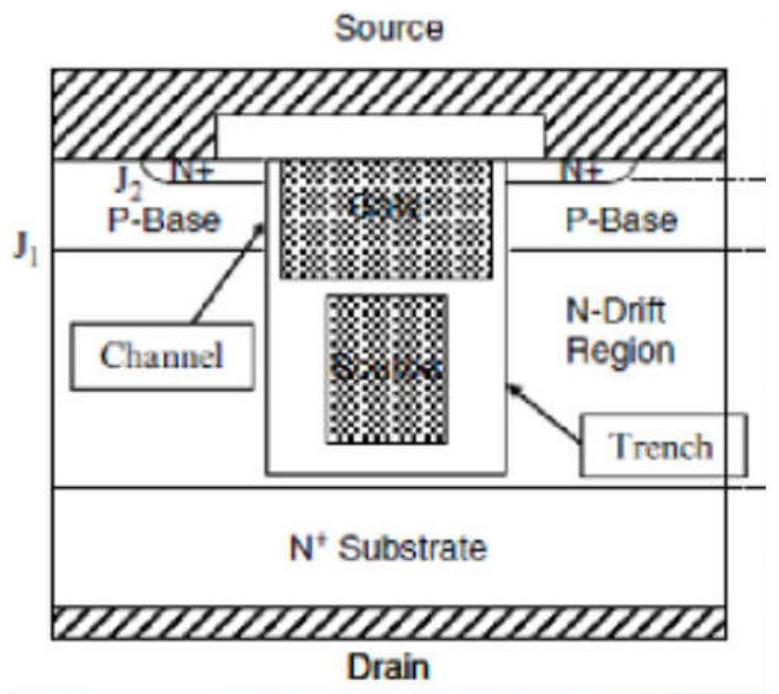

[0055] Taking NMOS as an example, a semiconductor power device of the present invention includes a substrate 1, an oxide layer 2, a dielectric layer 3, a well region 4, a drift region 5, a trench 6, a gate oxide layer 7, a field oxide layer 8, and polysilicon 9 , source 10, gate 11, drain 12, lightly doped region 13 and heavily doped region 14, wherein the substrate 1 is a P-type substrate, the well region 4 is a P-type well region, and the drift region 5 is an N-type In the drift region, N-type ions are implanted into the bottom of the trench 6 to form a lightly doped region 13 , and the upper surfaces of the well region 4 and the drift region 5 are implanted with N-type ions to form a heavily doped region 14 .

[0056] In the present invention, the substrate 1, the oxide layer 2 and the dielectric layer 3 are sequentially arranged from bottom to top, and the ion implantation in the upper surface of the P-type substrate forms a P-type well region, and the ion implantation in t...

Embodiment 2

[0074] Taking PMOS as an example, a semiconductor power device of the present invention includes a substrate 1, an oxide layer 2, a dielectric layer 3, a well region 4, a drift region 5, a trench 6, a gate oxide layer 7, a field oxide layer 8, and polysilicon 9 , source 10, gate 11, drain 12, lightly doped region 13 and heavily doped region 14, wherein the substrate 1 is an N-type substrate, the well region 4 is an N-type well region, and the drift region 5 is a P-type In the drift region, P-type ions are implanted into the bottom of the trench 6 to form a lightly doped region 13 , and P-type ions are implanted into the upper surface of the well region 4 and the drift region 5 to form a heavily doped region 14 .

[0075] In the present invention, the substrate 1, the oxide layer 2 and the dielectric layer 3 are sequentially arranged from bottom to top, and the ion implantation in the upper surface of the N-type substrate forms an N-type well region, and the ion implantation in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com