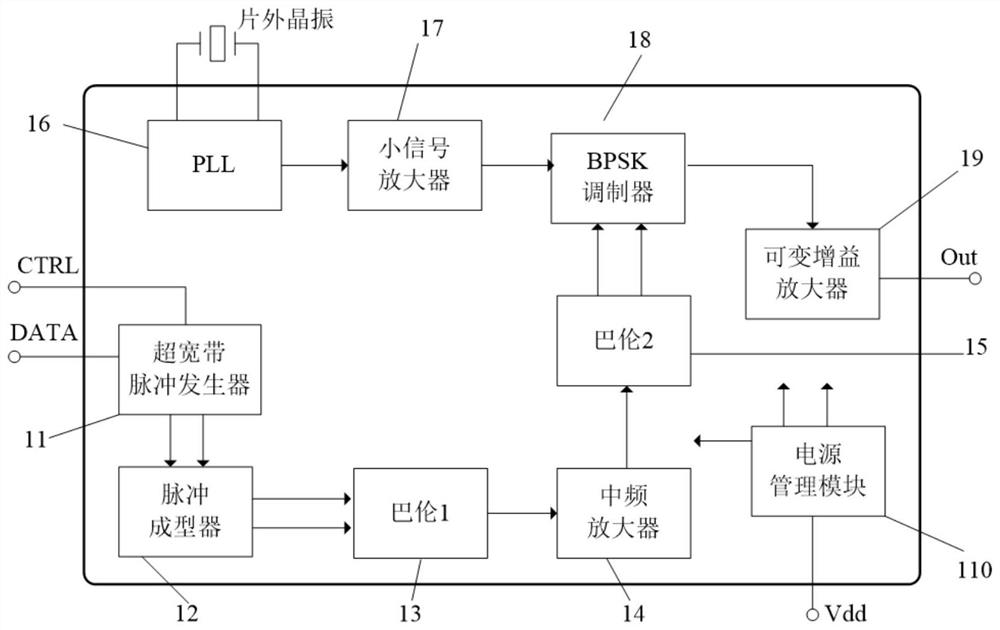

BPSK modulated UWB transmitter radio frequency front-end chip architecture

A radio frequency front-end and transmitter technology, which is applied in the field of architecture design of UWB transmitter radio frequency front-end chips, can solve problems such as complexity and unsuitability to standard protocols and architectures, and achieve the effect of reducing power consumption and chip power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to facilitate those of ordinary skill in the art to understand and implement the present invention, the present invention will be described in further detail below in conjunction with the accompanying drawings and implementation examples. It should be understood that the implementation examples described here are used to illustrate and explain the present invention, and are not intended to limit the present invention. Inventions and general replacements known to those skilled in the art also fall within the protection scope of the present invention.

[0043] Such as figure 1 As shown, the RF front-end chip architecture of the BPSK-modulated UWB transmitter includes: an ultra-wideband pulse generator 11, a pulse shaper 12, a balun 13, an intermediate frequency amplifier 14, a balun 2 15, a BPSK modulator 18, and a PLL module 16. Small signal amplifier 17 and variable gain amplifier 19;

[0044] The ultra-wideband pulse generator 11, pulse shaper 12, balun one 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More