Fast comparator circuit with wide common-mode input voltage

A common-mode input voltage and comparator circuit technology, applied in multiple input and output pulse circuits, electrical components, pulse processing, etc., can solve problems such as limiting the maximum transmission rate of signals, reducing edge rates, and affecting signal transmission quality. Achieve the effect of improving signal quality and increasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

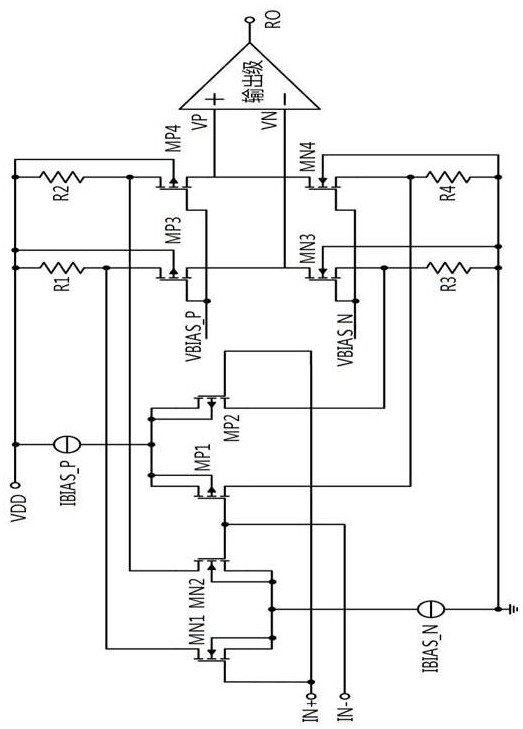

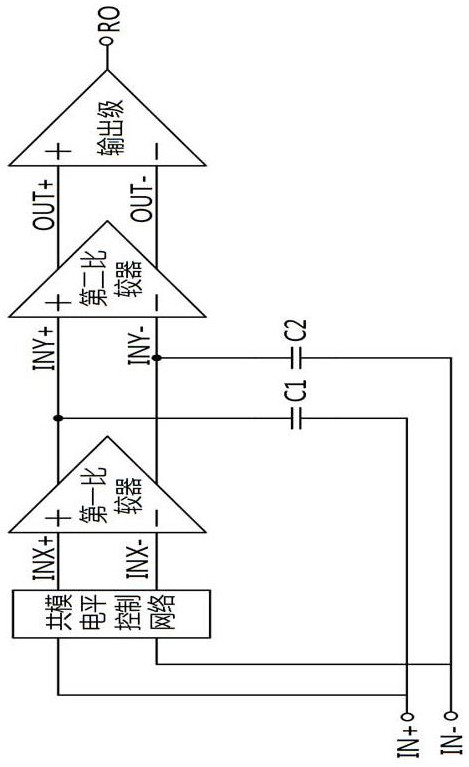

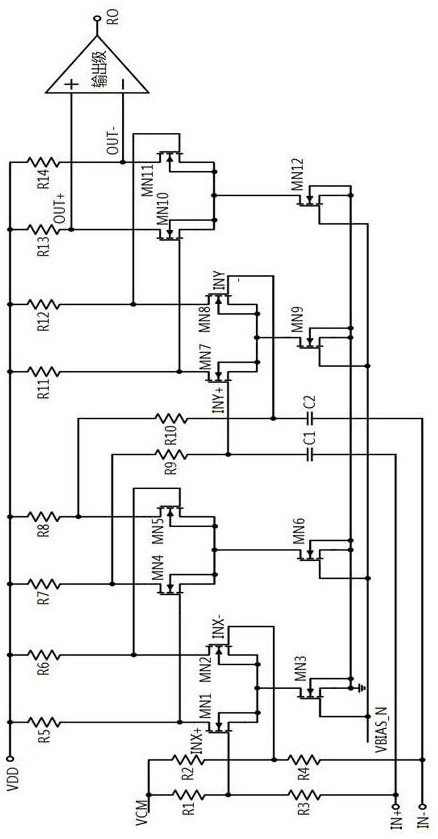

[0040] In order to solve the low-pass filter formed by the input capacitance of the large-size comparator in the prior art, the edge rate will be reduced, thereby limiting the maximum transmission rate of the signal, and the additional capacitive load brought by the input capacitance will cause the receiver input extra jitter at the end, which affects the technical problem of signal transmission quality. This embodiment provides a fast comparator circuit with wide common-mode input voltage. The circuit obtains a small offset by cascading two sets of comparators. voltage VOS and very high rates of dynamic signal transmission. Compared with the traditional comparator with a wide common-mode input voltage range, the comparator circuit in the present invention makes the offset voltage VOS and the signal transmission rate no longer restrict each other. On the premise of ensuring a more accurate offset voltage VOS, the signal transmission rate is increased and the signal quality is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More