HDL code simulation coverage rate asynchronous event-driven automatic analysis method

An asynchronous event, automatic analysis technology, applied in software testing/debugging, instrumentation, electrical digital data processing, etc., can solve problems affecting simulation performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

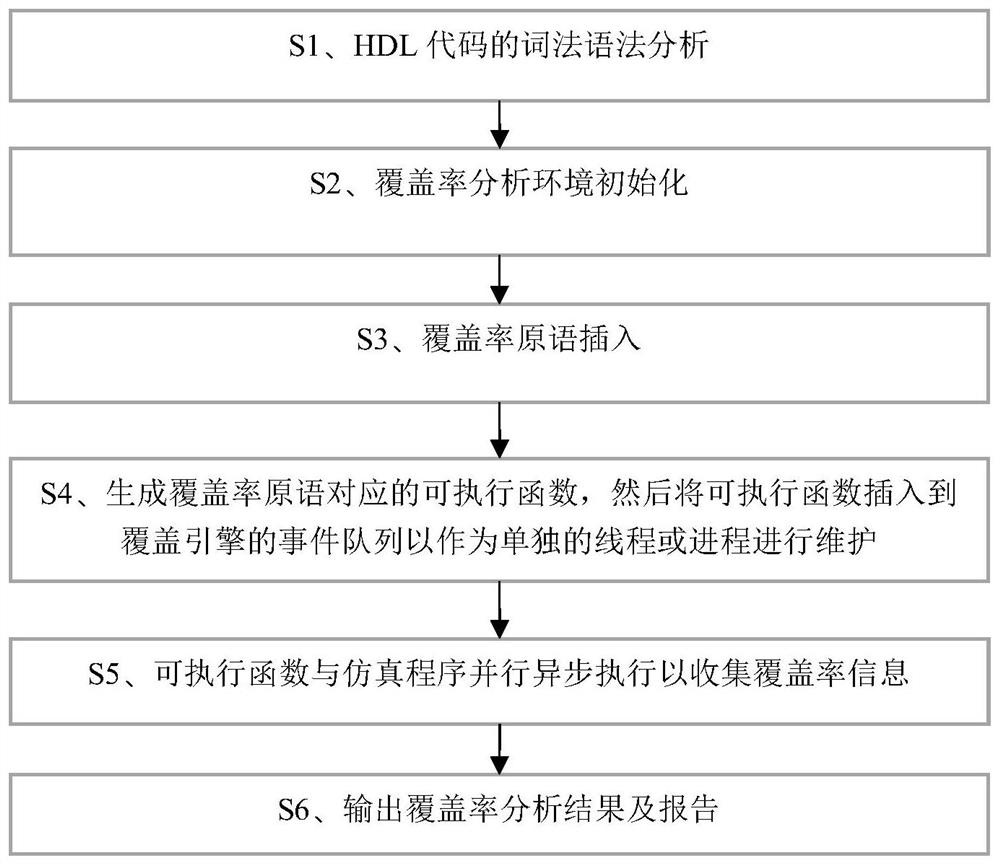

[0032] In order to understand the above-mentioned purpose, features and advantages of the present invention more clearly, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. It should be noted that, in the case of no conflict, the embodiments of the present application and the features in the embodiments can be combined with each other.

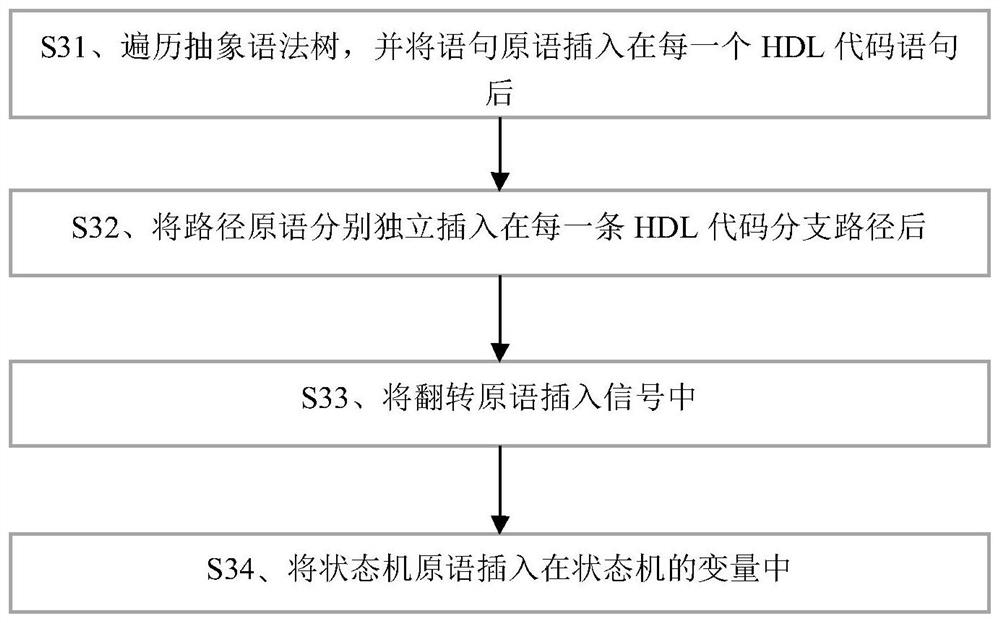

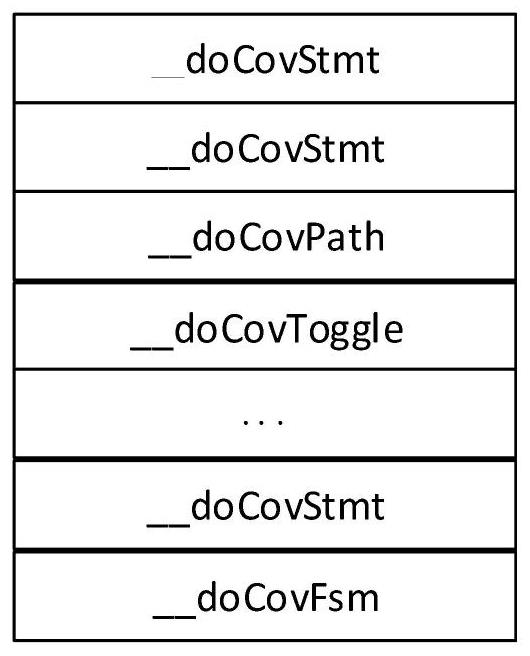

[0033] Specifically, an asynchronous event-driven automatic analysis method for HDL code simulation coverage proposed by a specific embodiment of the present invention, such as Figure 1-2 shown, including the following steps:

[0034] S1, Lexical syntax analysis of HDL code;

[0035] Lexical and grammatical analysis is to do lexical and grammatical analysis on HDL (Hardware Description Language, Verilog HDL and VHDL), including:

[0036] S11, write the lexical rules of HDL code, utilize the Flex software tool to generate the C program source code of lexical...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More