Simultaneous signal packing and pin allocation driven by design

A technology for signal pin and channel assignment, applied in computer-aided design, computing, instrumentation, etc., to solve the problems that software simulation cannot keep up with integrated circuits, lack of scalability, and low efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

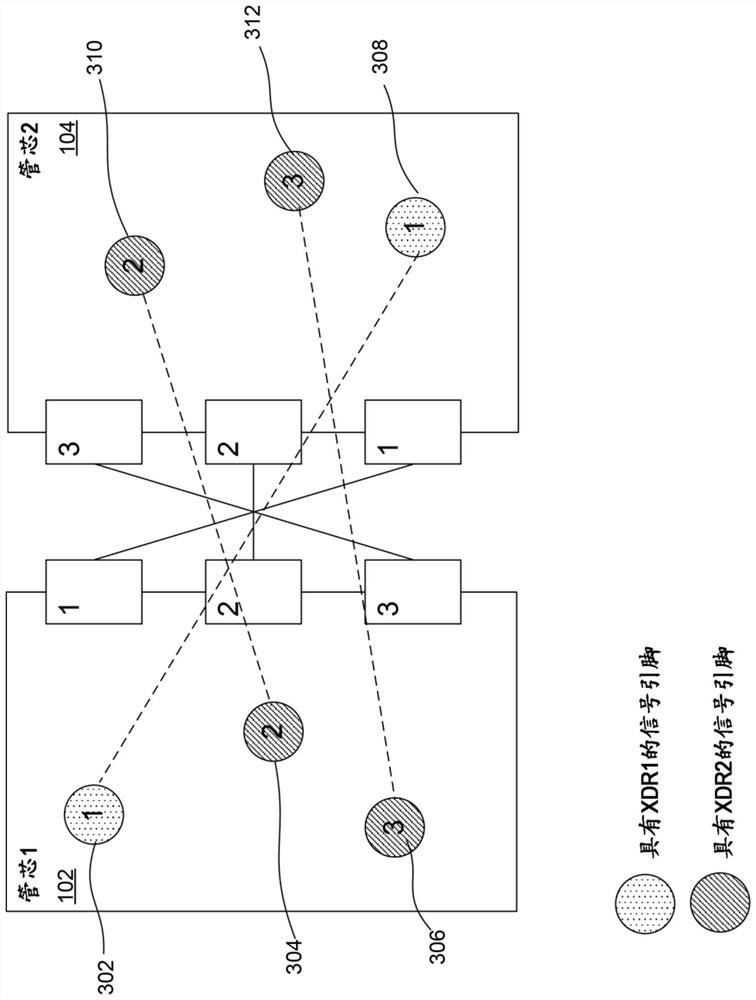

[0017] Aspects of the present disclosure relate to simultaneous signal grouping and pin assignments driven by design-under-test (DUT) pin locations.

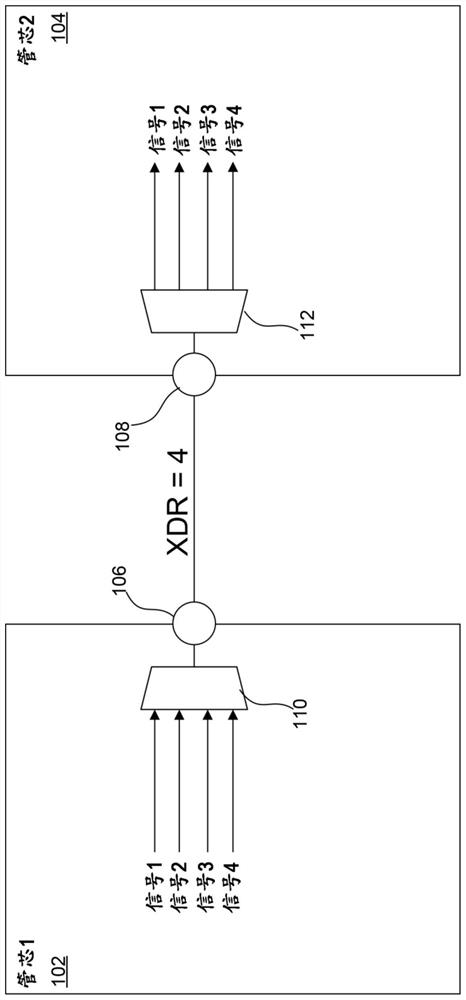

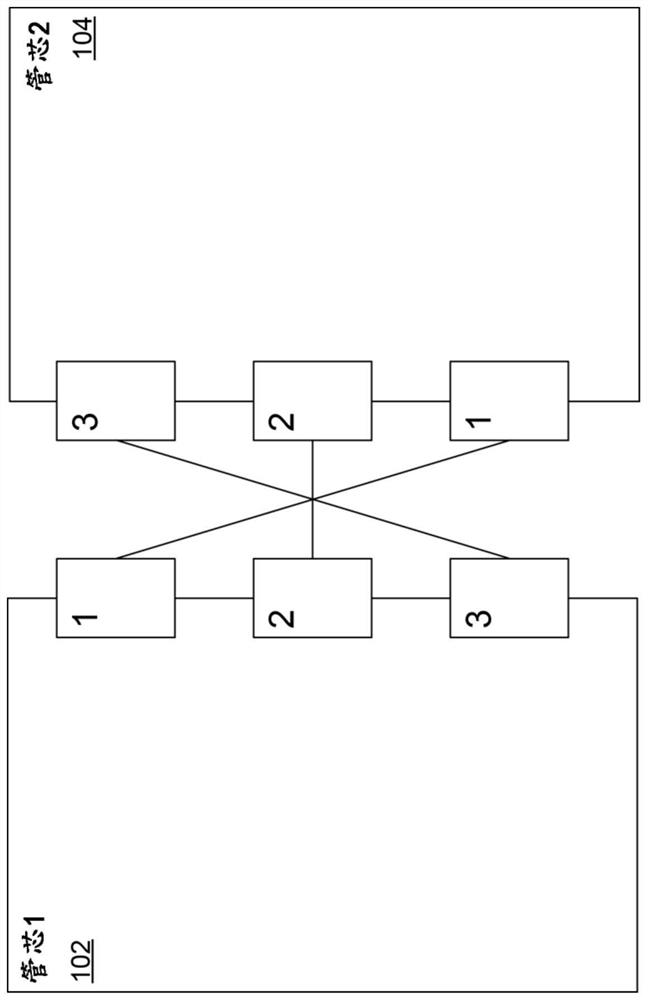

[0018] Signal communication between a pair of Field Programmable Gate Arrays (FPGAs) is carried through physical devices called sockets. Pinout refers to the assignment of specific design wires to specific sockets. The number of sockets between a pair of FPGAs is limited, which in turn limits the number of signals that can be transmitted between the pair of FPGAs. To overcome this limitation, a technique called Multi-Time Division Multiplexing (MTDMX) can be used, whereby multiple signals share a physical wire. In an exemplary configuration, the multiplexer is deployed in the transmitter side FPGA and the demultiplexer is deployed in the receiver side FPGA, where the signals are sent sequentially at the transmitter side and sequentially at the receiver side take over. Furthermore, different signals are assigned to different M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com