Modeling method of field effect transistor

A field effect transistor and modeling method technology, applied in special data processing applications, instruments, design optimization/simulation, etc., can solve the problem of incomplete test data, no large-scale promotion, non-conservation of high-order current and charge sources, etc. problems, to save manpower and material resources, achieve coordinated development, and accelerate process optimization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

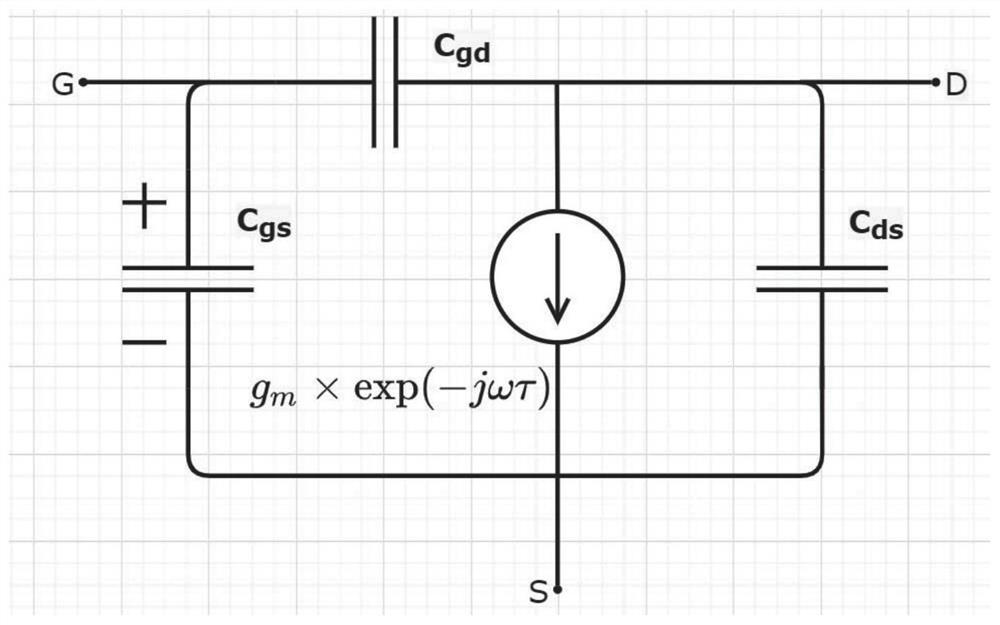

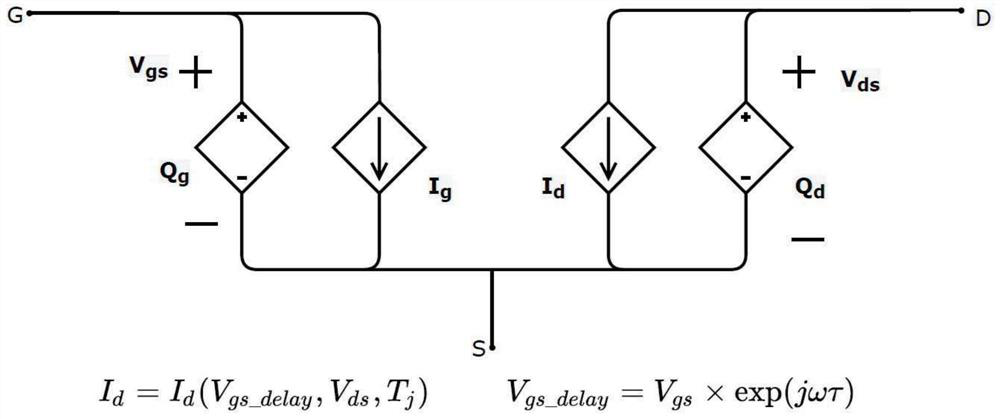

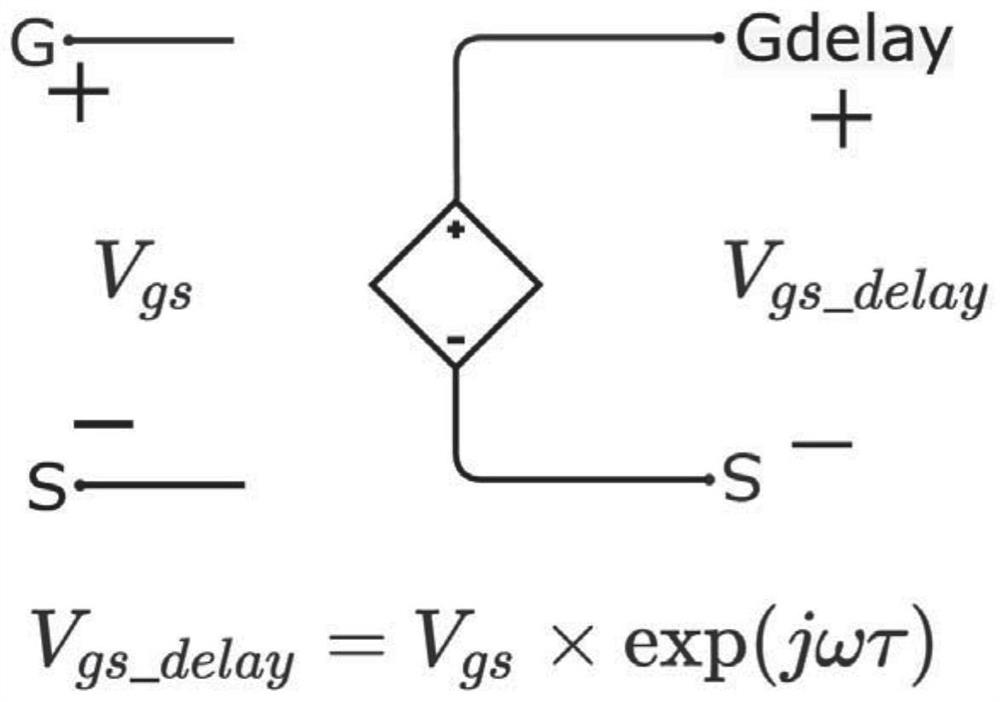

[0058] As mentioned earlier, some existing FET models, such as the Root Model and NeuroFET developed by Keysight, have covered the first-generation semiconductors to the third-generation semiconductors, such as MOSFET, LDMOS, GaAS pHEMT and GaN HEMT . These model architectures have nothing to do with the physics of the device. You only need to test standard S-parameters (scattering parameters), pulse or static I-V curves, and the models can be automatically generated without manual intervention. However, the biggest defect is that they do not model NQS well However, the model proposed by NXP and others uses high-order current sources and voltage sources, which can only simulate the NQS effect in a narrow band, and the charge conservation and simulation convergence of high-order sources will also be a major challenge.

[0059] In view of these deficiencies in the prior art, the inventors of the present application conducted an in-depth analysis of the NQS phenomenon of FETs, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More