Display panel

A technology for display panels and substrates, applied in the fields of instruments, nonlinear optics, optics, etc., can solve the problems of low pixel density and inability to meet the high-resolution requirements of VR equipment, etc., to achieve pixel density, improve process yield, shrink The effect of taking up space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

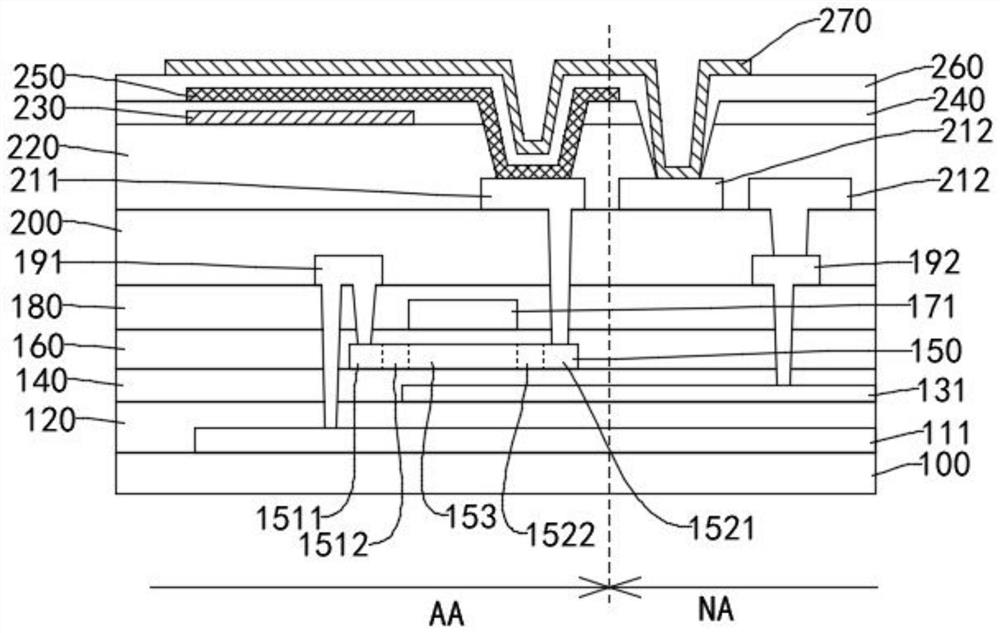

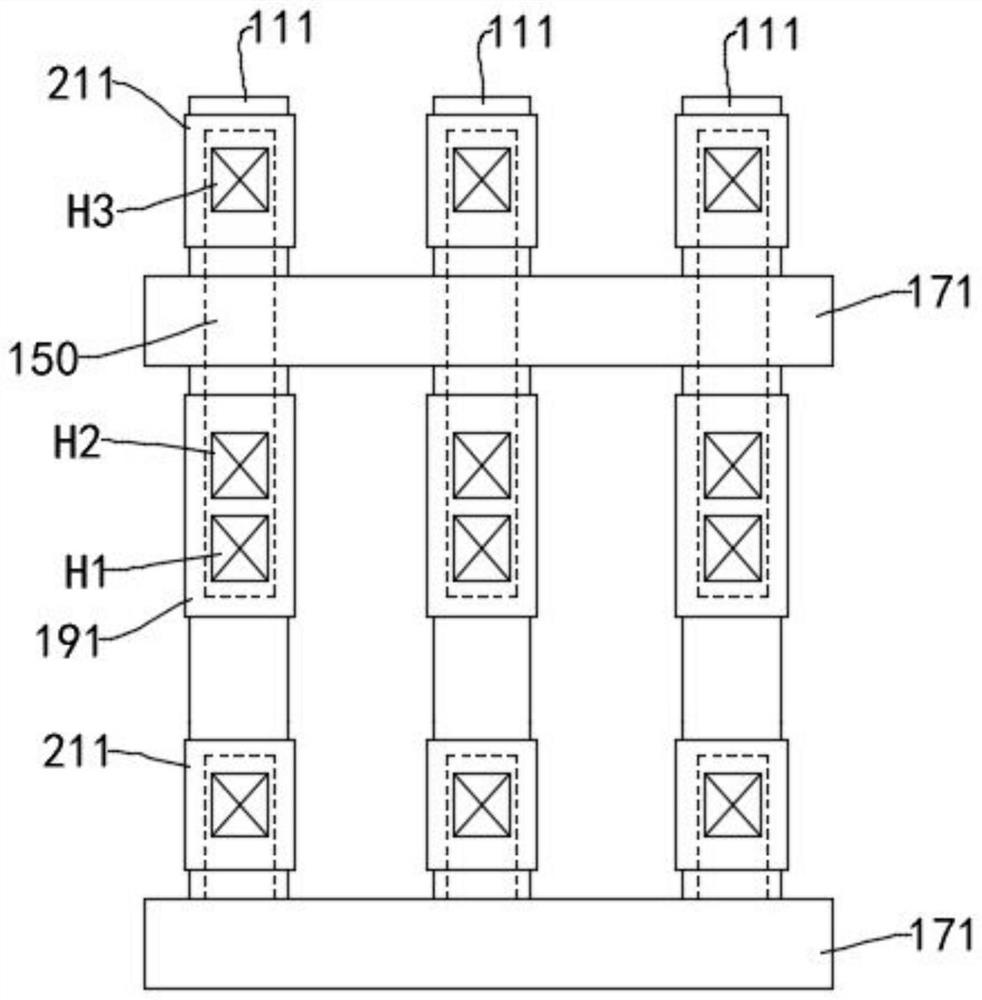

[0027] The technical solutions in the embodiments of the present application will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present application. Obviously, the described embodiments are only a part of the embodiments of the present application, but not all of the embodiments. Based on the embodiments in the present application, all other embodiments obtained by those skilled in the art without creative work fall within the protection scope of the present application.

[0028] An embodiment of the present application provides a display panel, the display panel includes a first conductive layer disposed on one side of a substrate, an active layer disposed on a side of the first conductive layer away from the substrate, and a first conductive layer disposed on the active layer away from the substrate A second conductive layer on one side of the conductive layer, and a third conductive layer on the side of the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More