Wafer-level system packaging structure and packaging method

A system packaging and wafer-level technology, applied in the direction of microstructure devices, manufacturing microstructure devices, microstructure technology, etc., can solve the problems of low packaging efficiency, save time, prevent lateral overflow, and enhance mechanical strength.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0036] This embodiment provides a wafer-level system packaging method, including the following steps:

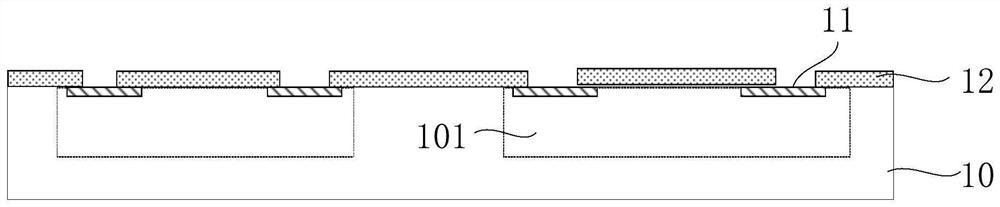

[0037] S01: Provide a first device wafer, a plurality of device modules are formed inside the first device wafer, the first device wafer has a front surface and a back surface, the front surface is exposed to electrically connect the device modules and is recessed in a plurality of first solder pads on the front side;

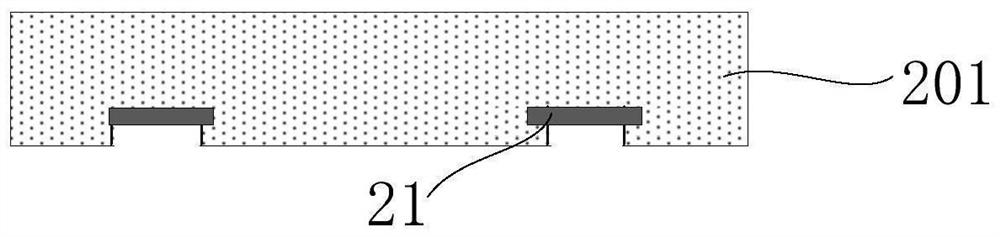

[0038] S02: providing a plurality of first chips, the lower surfaces of the first chips have second pads;

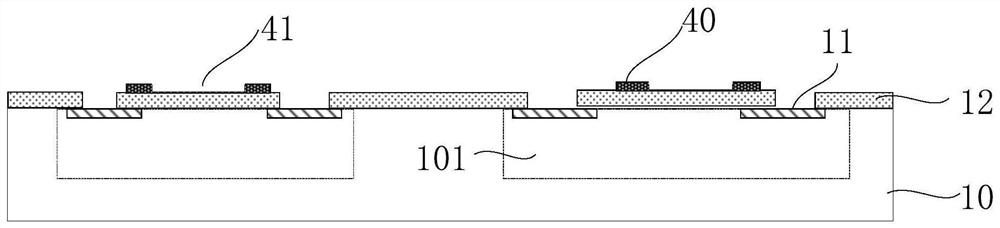

[0039] S03: forming an adhesive layer on the front surface of the first device wafer or the lower surface of the first chip, and forming an opening in the adhesive layer; bonding the first device through the adhesive layer the wafer and the first chip, the cavity formed by the opening is used as the working cavity of the first device module and / or the first chip; The pads are relatively surrounded by a gap;

[0040] S04: Use an electroplating process t...

Embodiment 2

[0069] refer to Image 6 , the difference between this embodiment and Embodiment 1 is that the backside of the second chip has the first electrical connection structure 22 , the method further includes, providing a second chip 50 or a second device wafer, and connecting the second chip 50 Or the second device wafer is electrically connected to the first electrical connection structure 22 .

[0070] In the present embodiment, the first electrical connection structure 22 is formed on the back of the second chip 50 . After bonding the first chip 201 , the second chip 50 is provided; and then the second chip 50 and the first chip 201 are bonded. The second chip 50 may be electrically connected to one device module 101 , or may be electrically connected to two or more device modules 101 . The figure shows a case where the second chip 50 is electrically connected to one device module 101 . It should be noted that, for the electrical connection between the second chip 50 and the de...

Embodiment 3

[0073] refer to Figure 7 The difference between this embodiment and Embodiment 2 is that the lower surface of the first device wafer 10 has a second electrical connection structure 13, and the method further includes: providing a third chip or a third device wafer 100, The third chip or the third device wafer 100 is electrically connected to the second electrical connection structure 13 .

[0074] The lower surface of the first device wafer 10 has a second electrical connection structure 13 , the third device wafer 100 includes a plurality of third chips 51 , and the second electrical connection structure 13 is electrically connected to the third chips 51 . First, the lower surface of the first device wafer 10 is thinned to expose the second electrical connection structure 13 , and then the third device wafer 100 is bonded on the first device wafer 10 , and the third chip 51 and the For the electrical connection of the second electrical connection structure 13 , reference ma...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Area | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More