Monolithic integrated three-primary-color Micro-LED chip and preparation method thereof

A single-chip integration and three-color technology, applied in semiconductor devices, electrical components, nanotechnology, etc., can solve problems such as low yield, poor timeliness, and low accuracy, so as to improve crystal quality, avoid low yield, reduce The effect of small polarizing electric fields

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

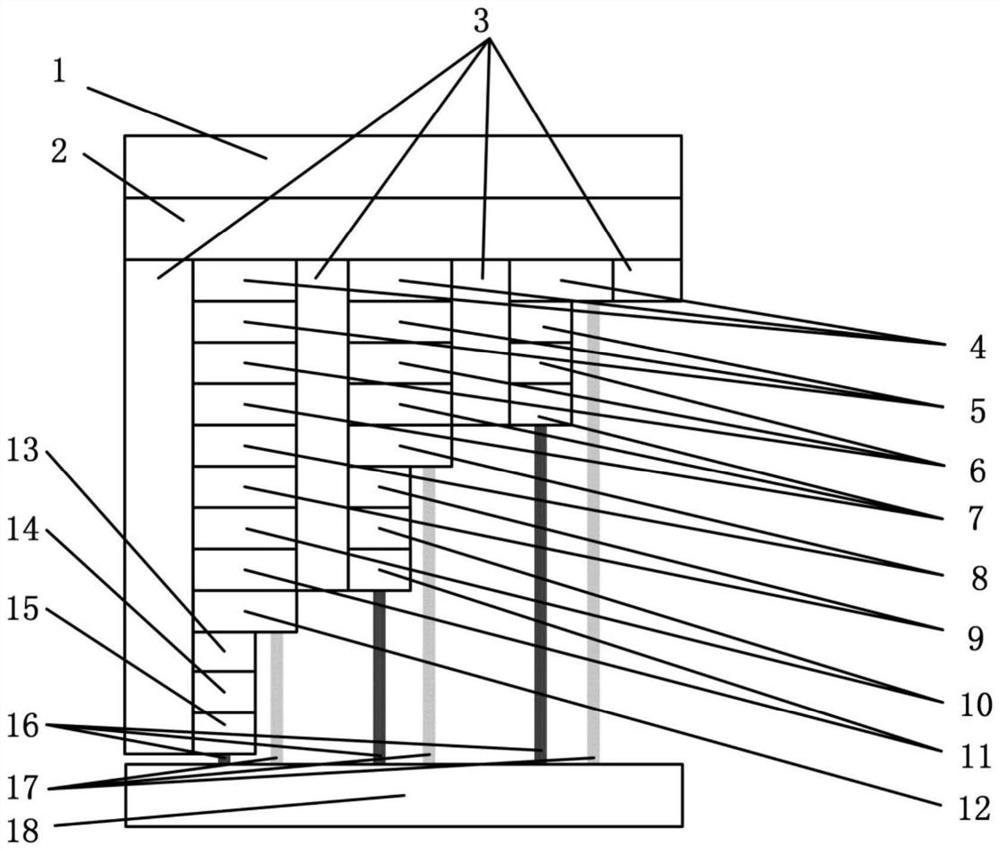

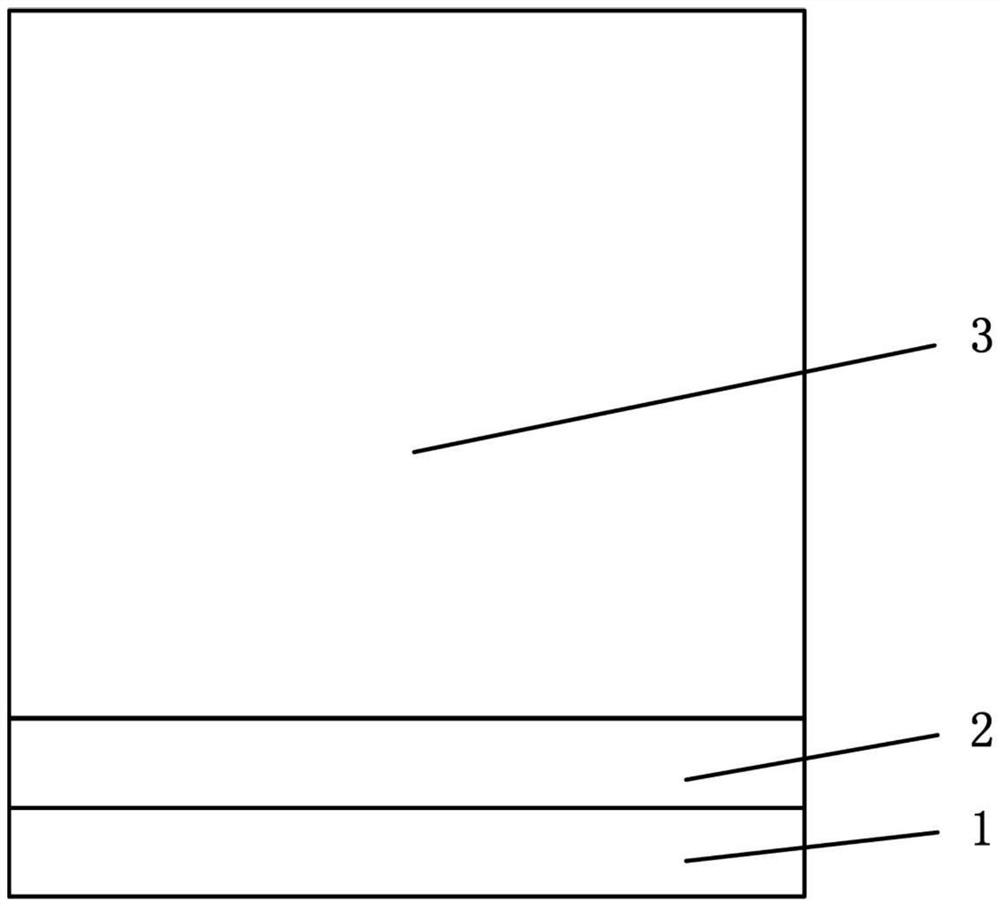

[0035] Embodiment 1 provides a monolithic integrated three-primary-color Micro-LED chip, see figure 1 , Image 6 , Figure 7 , comprising a substrate 1, a buffer layer 2 located on the substrate 1, an insulating layer 3 located on the buffer layer 2, the insulating layer 3 is etched to form a nano-scale micropore array, the micro The hole array constitutes a plurality of pixel units.

[0036] The substrate 1 can be one of sapphire, Si, and GaN, the buffer layer 2 can be a u-GaN buffer layer, and the insulating layer 3 can be SiO 2 Insulation. The thickness of the substrate 1 is 50-200 μm, the thickness of the buffer layer 2 is 1-4 μm, and the thickness of the insulating layer 3 is 5-10 μm. The buffer layer 2 can reduce the dislocation density of the subsequent epitaxial layer growth and improve the crystal quality.

[0037] see Figure 1 to Figure 5, each of the pixel units includes a first light-emitting region, a second light-emitting region and a third light-emitting ...

Embodiment 2

[0043] Embodiment 2 is a chip preparation method corresponding to the chip provided in Embodiment 1. Specifically, Embodiment 2 provides a preparation method of a monolithically integrated three-primary-color Micro-LED chip, including the following steps:

[0044] Step 1. Growing a buffer layer on the substrate;

[0045] Step 2. depositing an insulating layer on the buffer layer;

[0046] Step 3. Photolithography and etching are performed on the insulating layer, and the etching depth is until the buffer layer is exposed, so as to obtain a nano-scale microhole array;

[0047] Step 4. The micro-hole array constitutes a plurality of pixel units, and each of the pixel units includes a first light-emitting area, a second light-emitting area and a third light-emitting area separated by the insulating layer; all light-emitting areas are The first epitaxial layer, the second epitaxial layer and the third epitaxial layer are grown sequentially from bottom to top, and the three epitax...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com