Semiconductor substrate, field effect transistor, and method for forming silicon germanide layer

A field-effect transistor and semiconductor technology, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of increased penetration dislocation density, reduction of dislocation, and deterioration of surface roughness, etc., and achieve high yield.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] Below, refer to Figure 1 to Figure 6 , While explaining the first embodiment of the present invention.

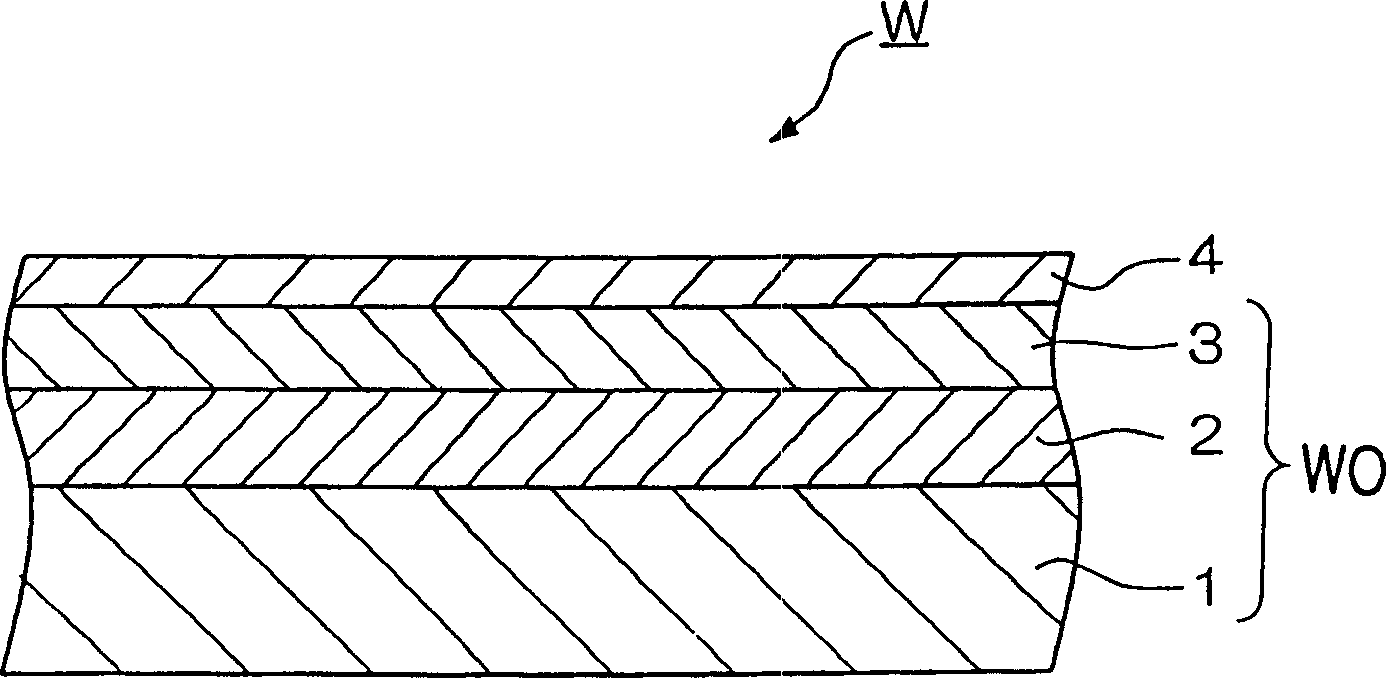

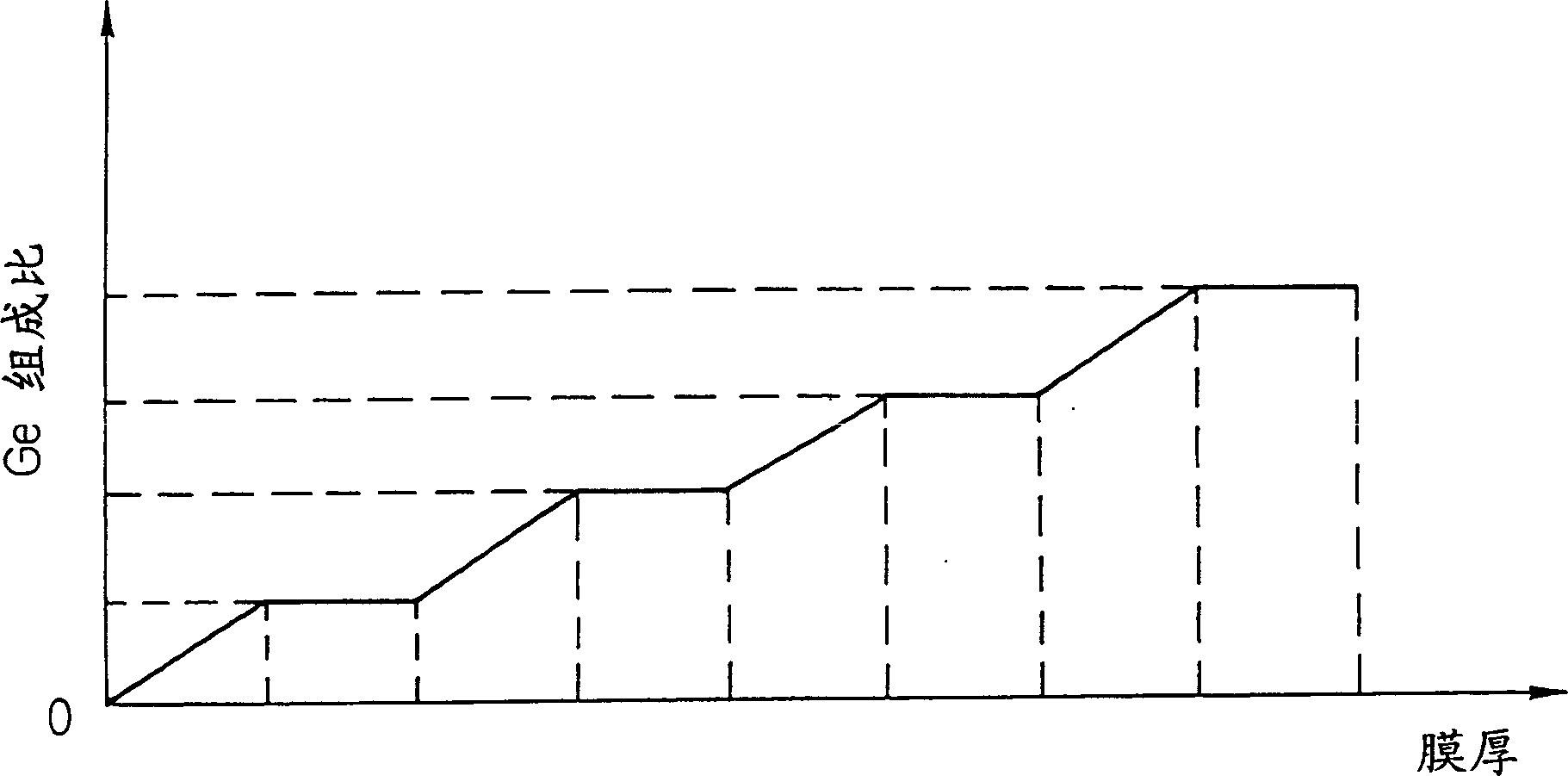

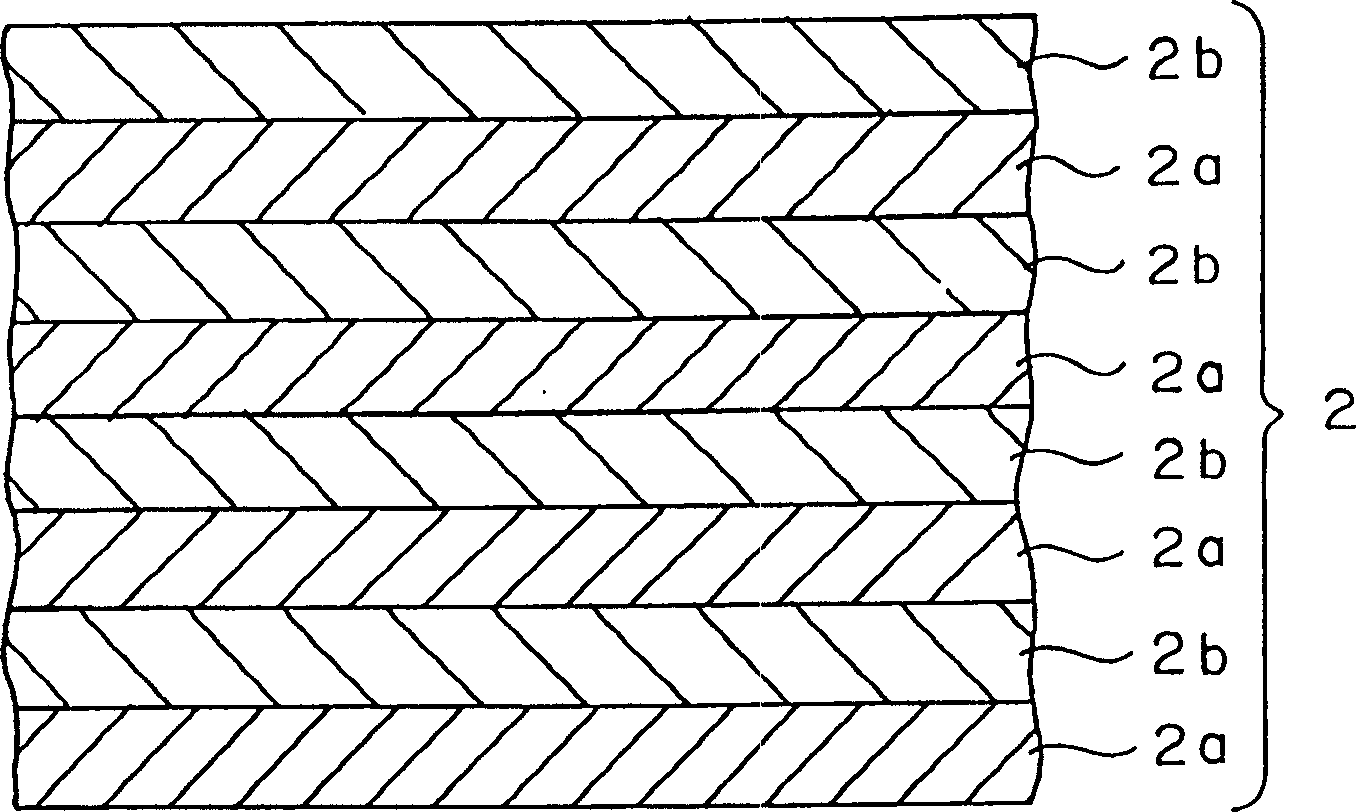

[0045] figure 1 The cross-sectional structure of the semiconductor wafer (semiconductor substrate) W provided with the semiconductor wafer (semiconductor substrate) WO of the present invention and the deformed Si layer is shown in FIG. figure 1 As shown in the low-pressure CVD method, the Ge composition ratio x from 0 to y (for example, y=0.3) on the Si substrate 1 manufactured by the upward growth of the CZ method has an inclination in the film formation direction and is stepped Morphological changes of Si 1-x Ge x The step gradient layer (SiGe buffer layer) 2 is epitaxially grown. In addition, in the film formation by the above-mentioned low-pressure CVD method, H 2 As a carrier gas, SiH is used 4 And GeH 4 As the source gas.

[0046] Secondly, epitaxially grow Si with a certain Ge composition ratio on the stepped inclined layer 2. 1-y Ge y The relaxation layer 3 to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More