Zero-delay slew-rate controlled output buffer

A technology of output buffer and signal output, which is applied to power oscillators, amplifiers with semiconductor devices/discharge tubes, amplifiers, etc., and can solve problems such as reduced switching speed, narrowed gap, and electromagnetic interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Best Mode for Carrying Out the Invention

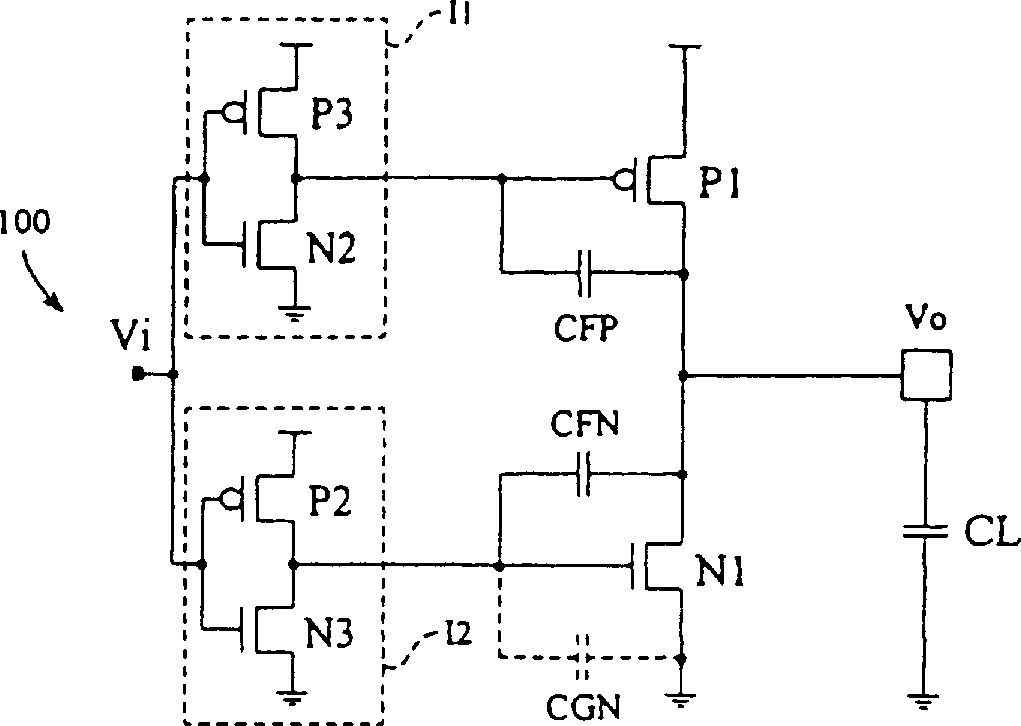

[0019] refer to figure 1 , the output buffer circuit 100 according to the present invention comprises an input node v for receiving a digital signal i . The input node is coupled to the control gates of four transistors: P-channel transistors P2 and P3, and N-channel transistors N2 and N3. Transistors P3 and N2 are coupled as inverter I1 and transistors P2 and N3 are coupled as inverter I2.

[0020] The output of buffer 100 is driven by transistors P1 and N1, whose drains are connected to the output node v o coupling. The source of transistor P1 is connected to V DD is coupled, while the source of transistor N1 is coupled to ground potential. The control gate of transistor P1 is coupled to the drains of transistors P3 and N2. Similarly, the control gate of transistor N1 is coupled to the drains of transistors P2 and N3.

[0021] In addition, according to the present invention, from the output node v o The feedback path...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More