Method for making silicon nitride ROM

A technology of read-only memory and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., and can solve the problems of complex ion implantation process, low reliability, breakdown, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 example

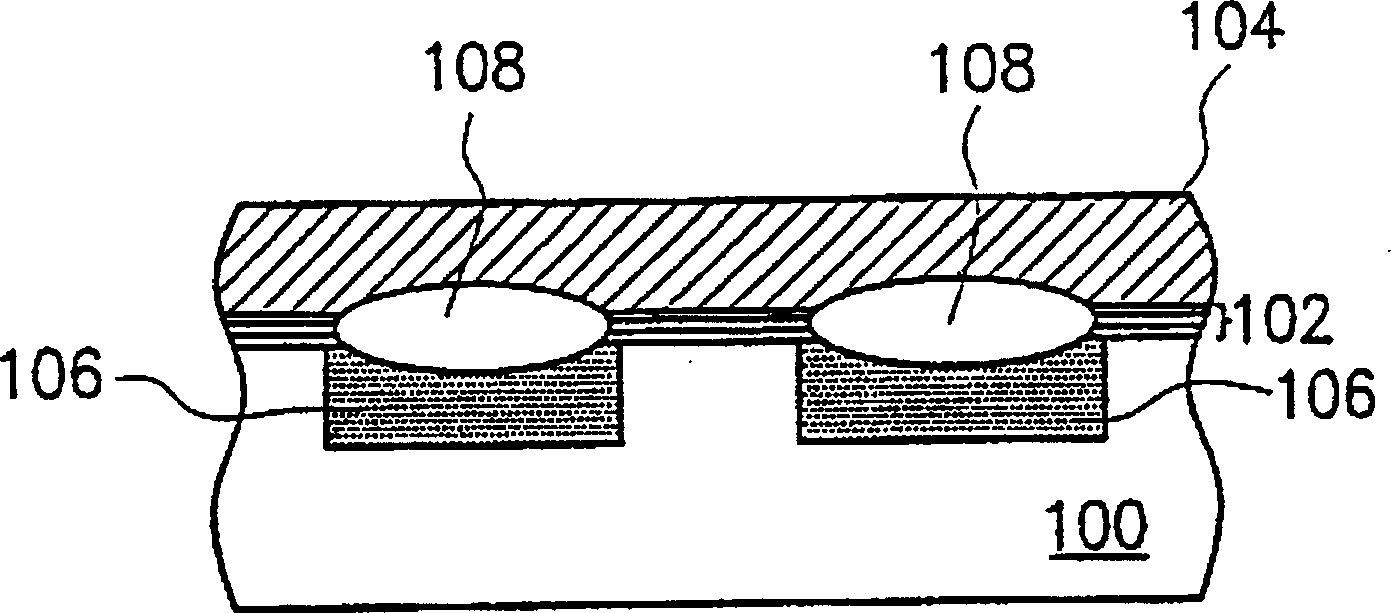

[0046] In addition, the present invention can also be applied to a method for manufacturing a silicon nitride read-only memory (Nitride ReadOnly Memory, referred to as NROM), so as to prevent the dopant of the buried bit line from diffusing due to heat treatment, and to reduce the gap of the polysilicon pattern line width. In addition, the effective length of the channel can also be increased, so that the components can be miniaturized.

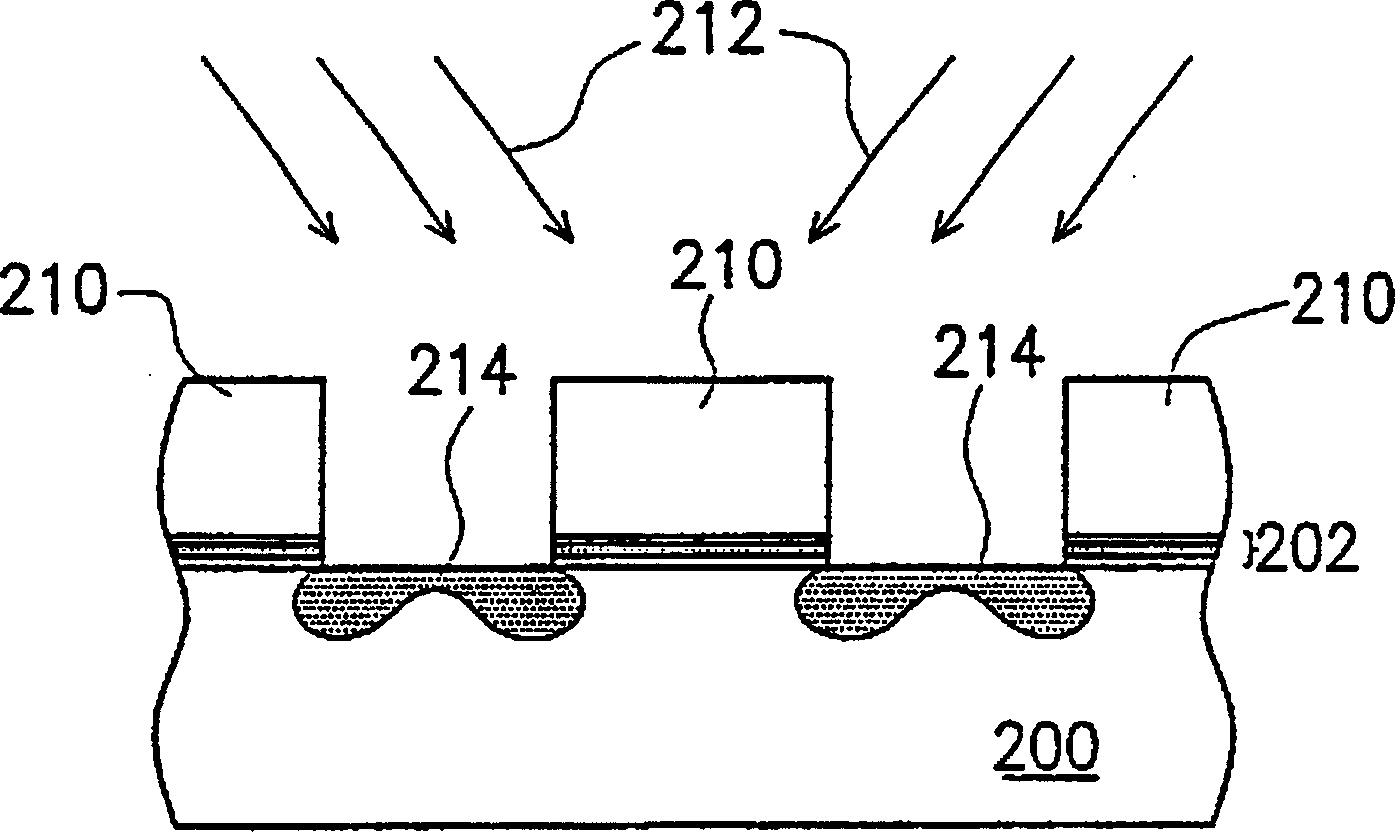

[0047] The front-end process of the silicon nitride read-only memory is as in the first embodiment Figure 3A to Figure 3C The same, and the mask pattern must be the gate pattern 324, the material of which is polysilicon, for example, and then refer to Figure 5 shown.

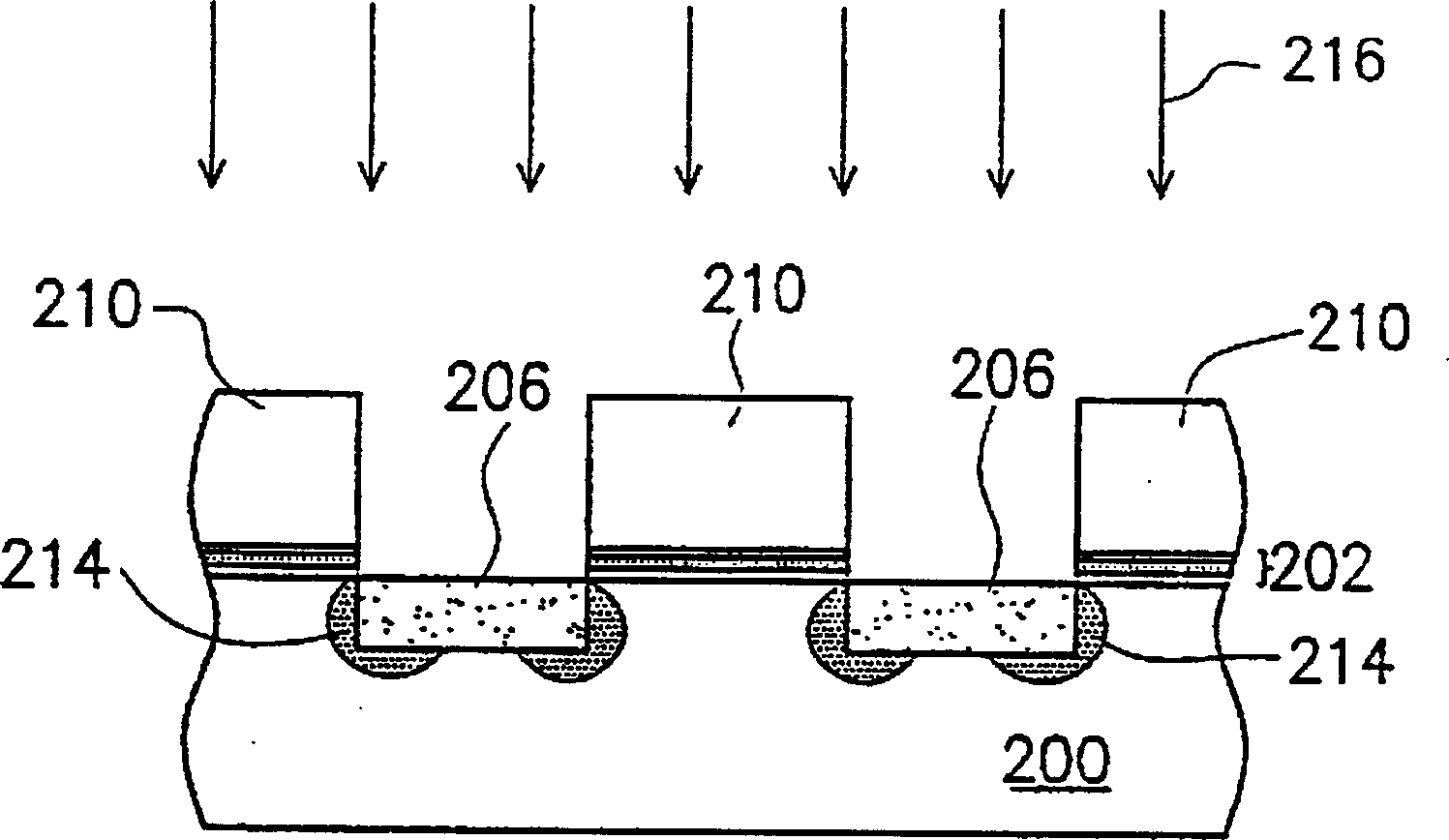

[0048] Figure 5 It is a cross-sectional view of the manufacturing process of a silicon nitride ROM according to the second embodiment of the present invention, and it is a process after forming the pocket-type doped region 318 .

[0049] Please refer to Figure 5 , usin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More