Semiconductor device

A semiconductor and device technology, which is applied in the field of semiconductor devices to improve mechanical and electrical characteristics, can solve the problems of uneven current, the reduction of the maximum cut-off current of semiconductor chips, and the inability to cut off the current of MOS gate, so as to eliminate fluctuations and unevenness, improve The effect of the maximum cut-off current and the reduction in the number of screw fixations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

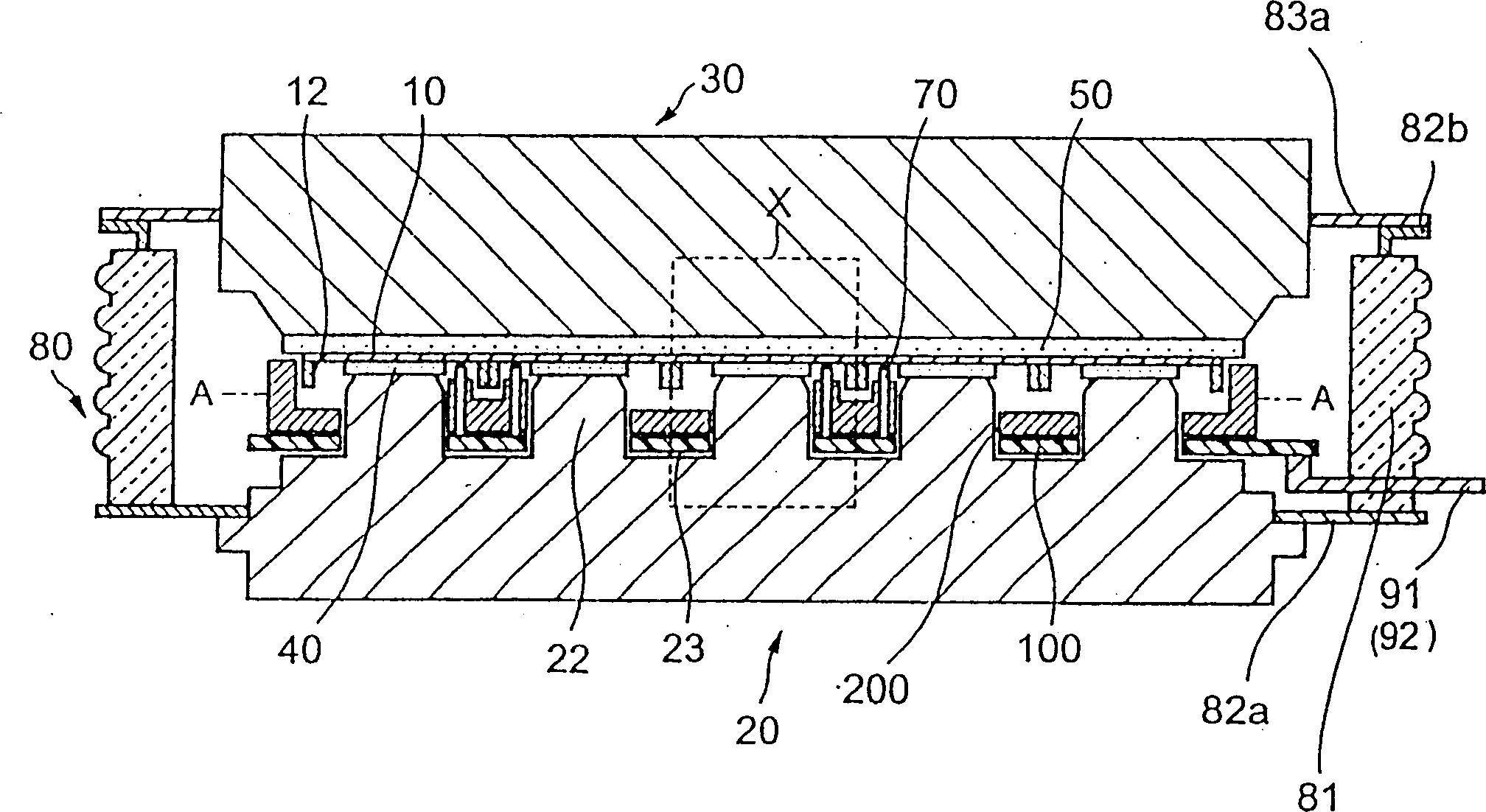

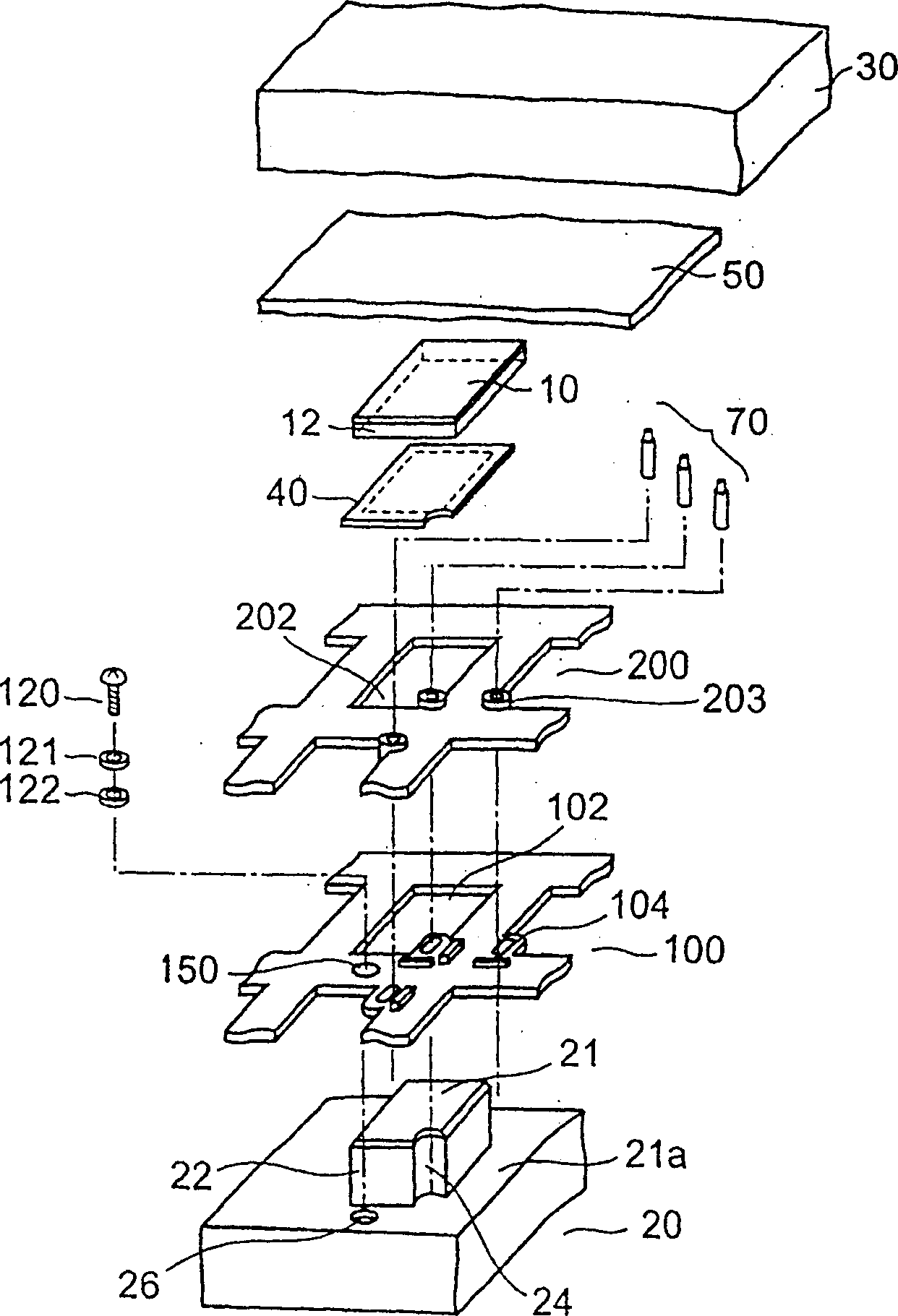

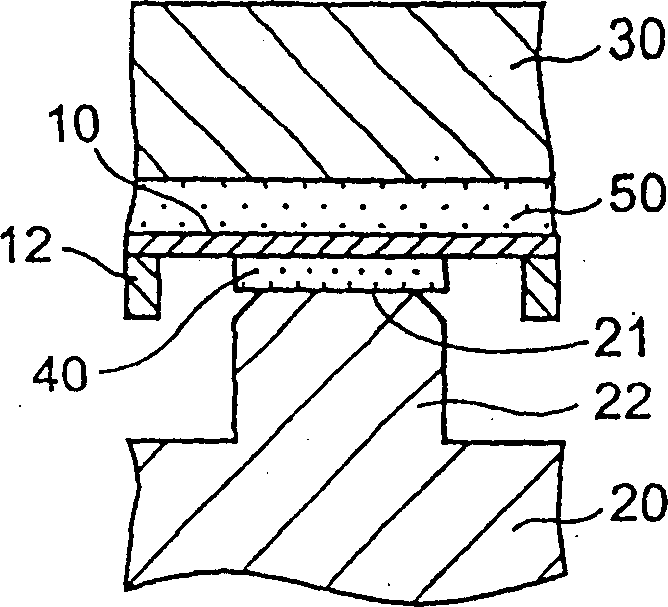

[0086] First, refer to figure 1 , Describes the outline of the configuration of the power control semiconductor device. figure 1 It is a cross-sectional view of a power control semiconductor device related to an embodiment of the present invention.

[0087] That is to say, semiconductor devices for power control, for example, a second main electrode member (hereinafter referred to as emitter copper pillar) 20 having a planar square pillar 22 and recessed portion 23 and a first main electrode member (hereinafter referred to as collector copper The pillars 30 are arranged in an opposed state. Semiconductor chips 10 such as IGBTs and IEGTs are arranged between the respective pillars 22 of the emitter copper pillar 20 and the aforementioned collector copper pillar 30 through molybdenum (Mo) buffer plates (hereinafter referred to as Mo buffer plates) 40 and 50, With the help of the above-mentioned emitter copper column 20 and the above-mentioned collector copper column 30 being press...

no. 2 Embodiment approach

[0162] Reference Figure 19 A detailed description will be given of the semiconductor device for power control according to the second embodiment of the present invention.

[0163] Figure 19 It is a schematic cross-sectional view showing the main part of the power control semiconductor device according to the second embodiment. In the figure, the same parts as those in the first embodiment are denoted by the same reference numerals, and repeated descriptions of the parts are omitted, and only the different parts are described.

[0164] In this embodiment and the above-mentioned first embodiment, regarding the contact between the emitter copper post 20 and the emitter wiring pattern 110 of the circuit wiring board 100, the circuit board mounting screw (second connecting conductor) 120 is used for connection in the above-mentioned first embodiment However, in this embodiment, the emitter pin (second connecting conductor) 300 is used for connection, and this point is different.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More