In-line upgrade system for in-situ programmable gate array program and its implementation method

A gate array and program technology, applied in the field of external bus updating FPGA program, can solve problems such as unfavorable upgrade programs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

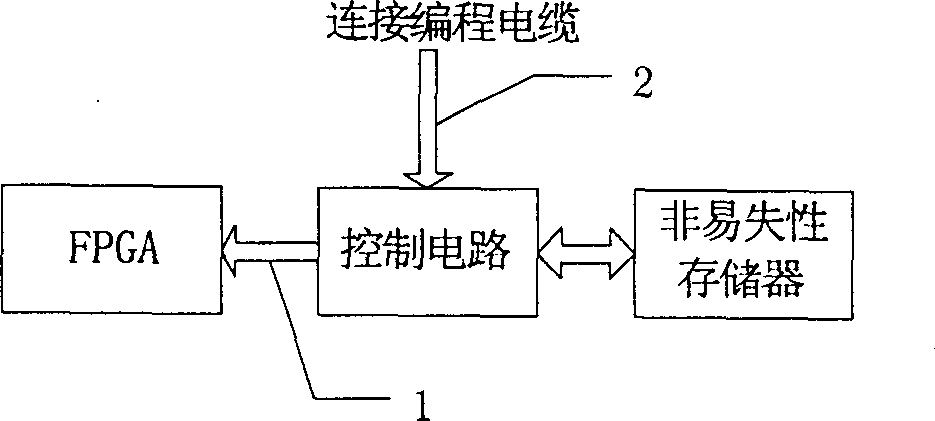

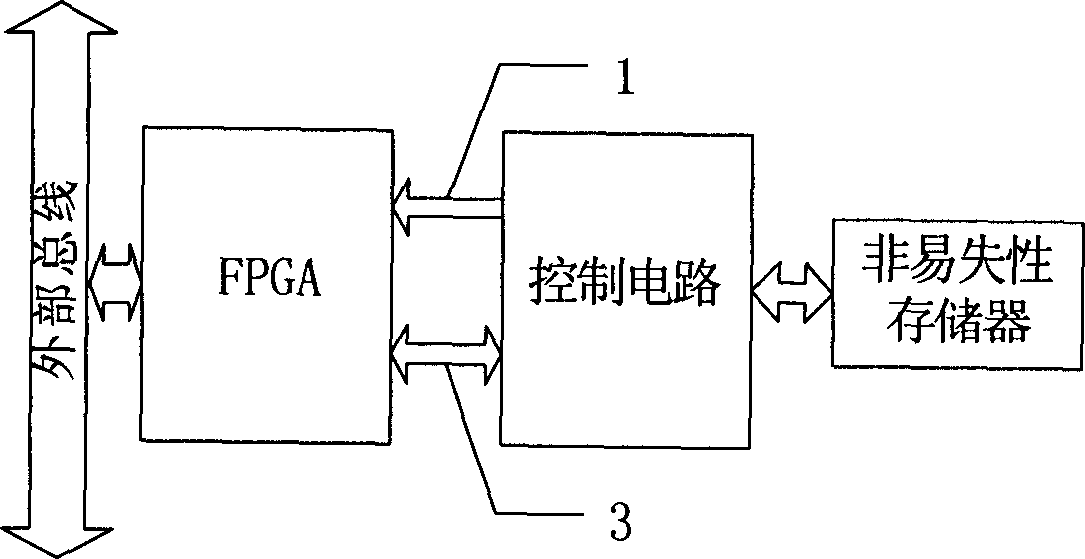

[0020] please see image 3 : 3 is the dedicated programming bus, the rest are with figure 1 same. When working, FPGA and external buses work according to their own design requirements and are not affected by the control circuit. During programming, the external bus transmits data to the FPGA through a certain agreed method, and the FPGA transmits the data to the control circuit through the dedicated programming bus 3, and then writes the data into the non-volatile memory. Figure 4 yes image 3 An example of . The dedicated programming bus is the I2C bus. The FPGA is the 10K30 of the FLEX10K series of Altera Company. The FPGA is connected to the microcomputer through the external bus—PCI bus, and then transmits the data to the control circuit made by the chip EPM7064S through the two-wire transmission protocol of I2C. The control circuit is bidirectionally connected with the nonvolatile memory made of SST company chip 29EE010.

[0021] goodbye Figure 5 : The FPGA progr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More