Method of improving performance of flash memory

A memory, flash technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of oxygen-nitrogen-oxygen layer erosion, performance degradation of flash memory, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

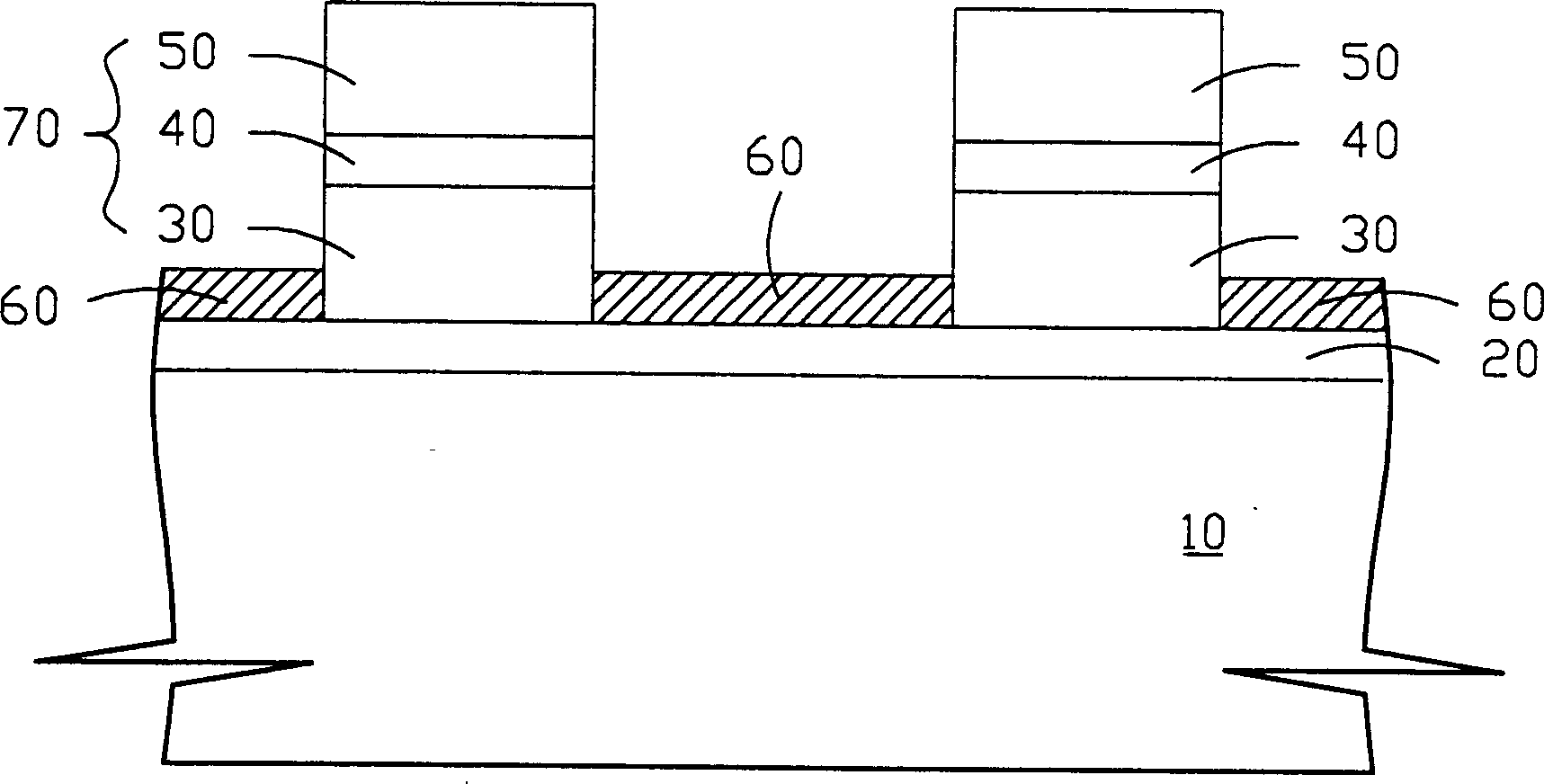

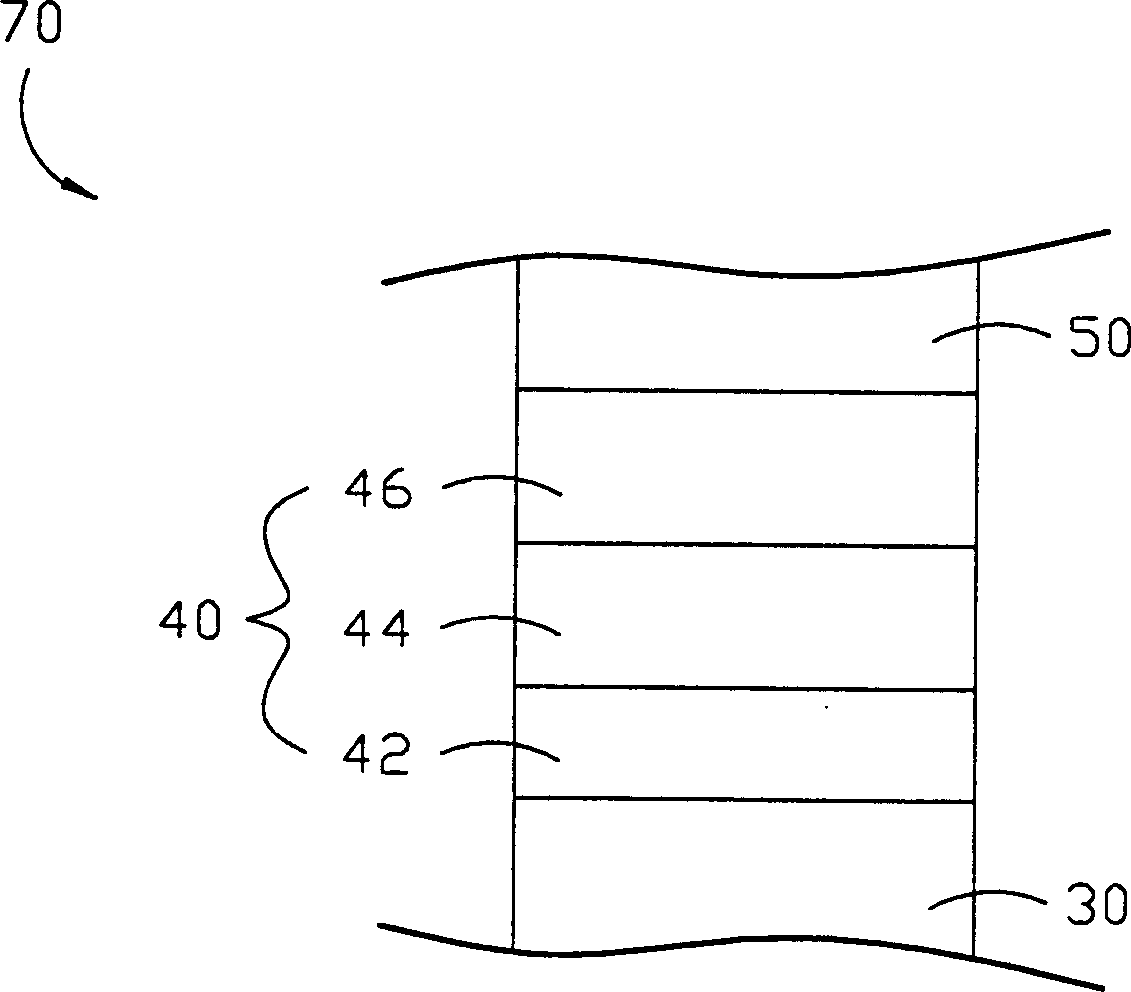

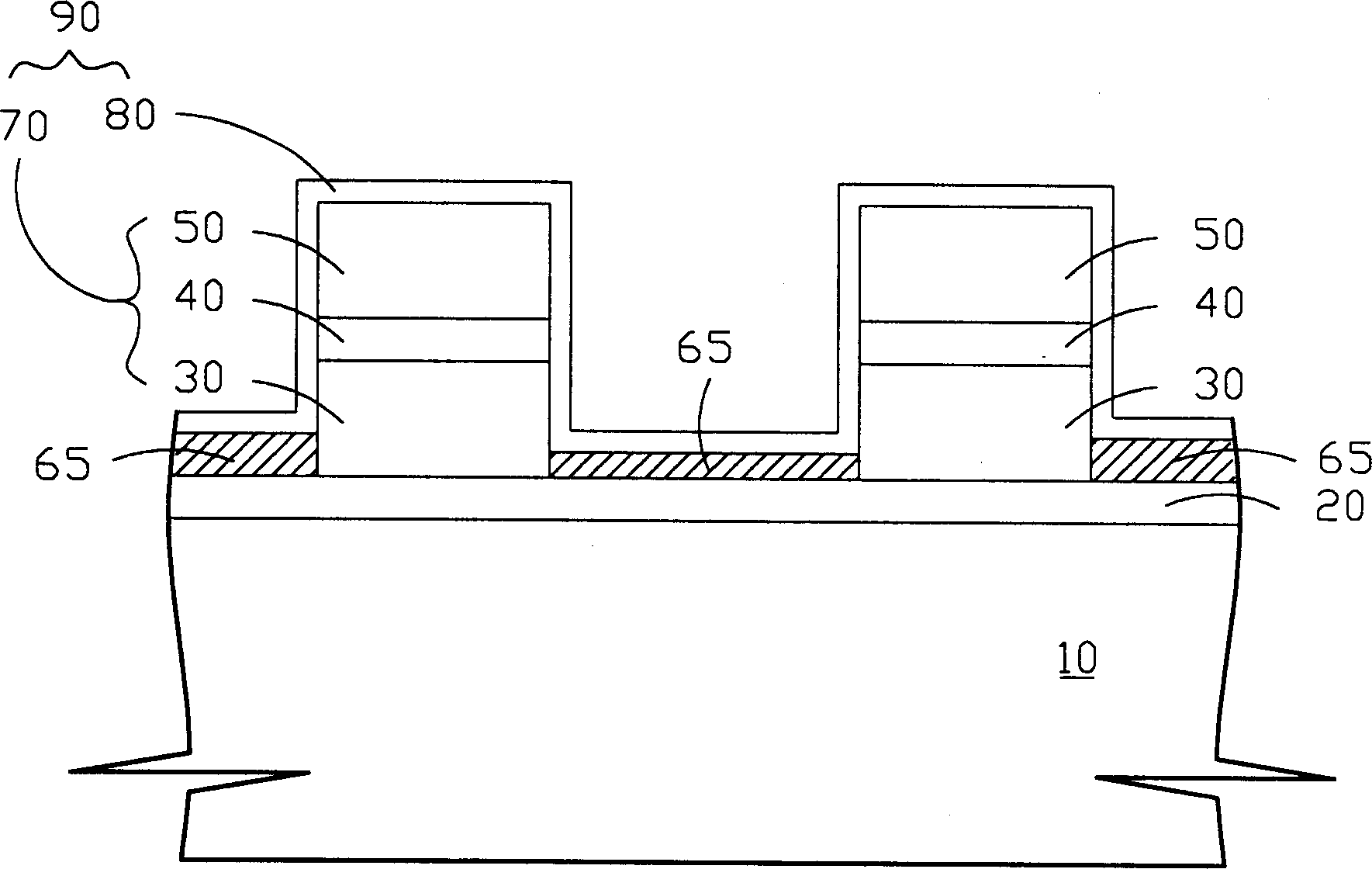

[0029] Such as Figure 5Shown is a cross-sectional view of a typical flash memory unit cell, the memory unit usually includes a substrate 100 and a thin gate oxide layer 110 (usually as a tunnel oxide layer) formed on the surface of the substrate 100, two The stacked gate structure 160 is located on the gate oxide layer 110 . The stacked gate structure 160 also includes a first polysilicon layer as a floating gate 120 on the tunnel oxide layer 110, an inner poly dielectric layer 130 on the floating gate 120, and finally, a second polysilicon layer layer overlies the inner poly dielectric layer 130 as a control gate 140 .

[0030] Such as Figure 5 As shown, the stacked gate structure 160 is formed using conventional etching methods. However, a problem usually created by this step is the formation of polysilicon residue 150 . The polysilicon residue 150 is formed by etching the unmasked part of the polysilicon layer 120. The material of the polysilicon residue 150 is mainly...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More