Balance symmetric type read-out amplifier circuit for nonvolatile memory

A non-volatile, sense amplification technology, applied in static memory, read-only memory, digital memory information, etc., can solve the problem of increasing the input capacitive load of the sense amplifier, failing to solve the small leakage current of the memory cell, reducing the readout Operation speed and other issues, to achieve the effect of saving data rewriting time, eliminating small leakage current, and reducing charge pump load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

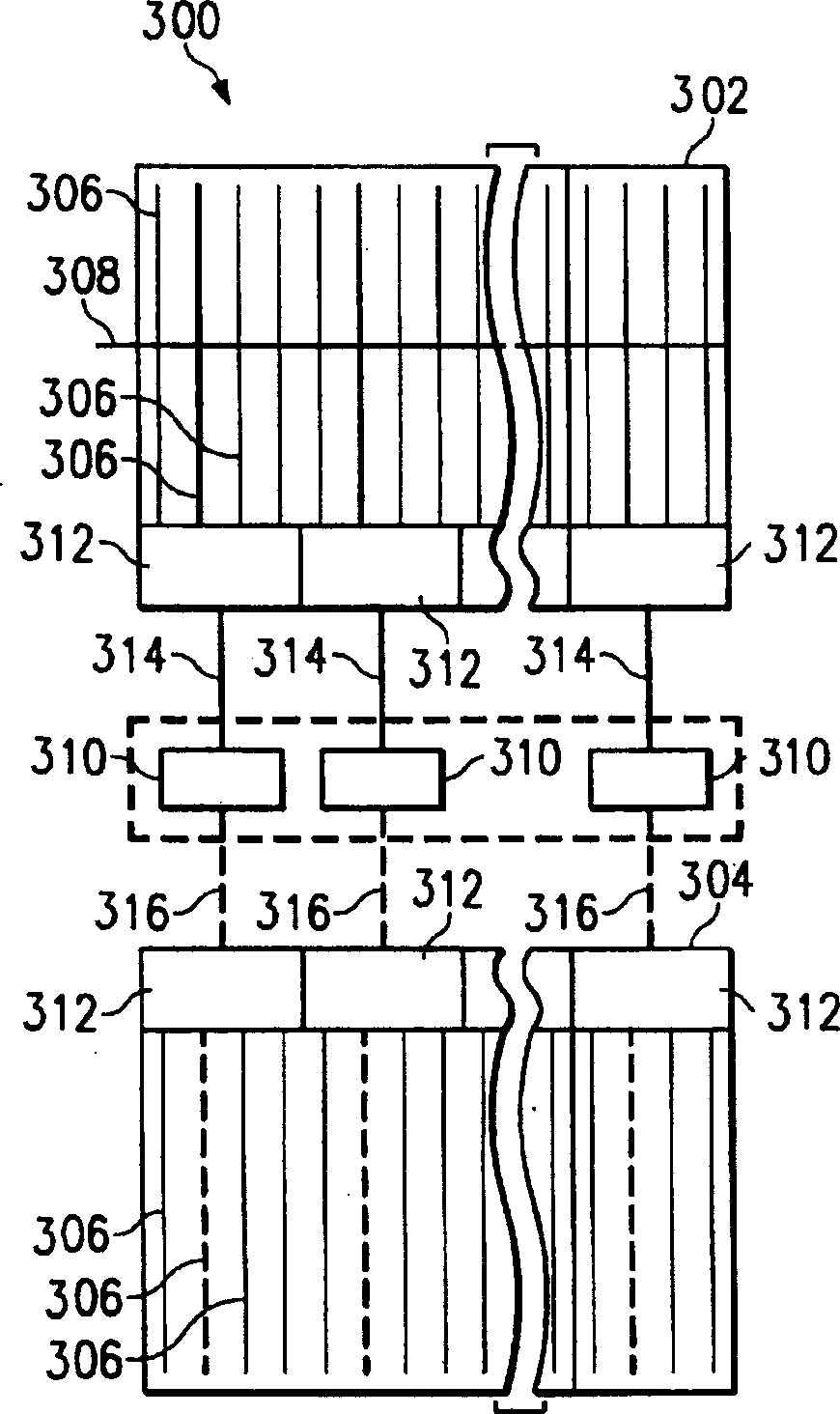

[0066] according to Figure 6 ~ Figure 11 The preferred embodiments of the present invention are given and described in detail in conjunction with the accompanying drawings, so as to better illustrate the structural features and functional features of the present invention.

[0067] The preferred embodiment of the present invention can be used for reading of general-purpose electrically erasable and programmable read-only memory (EEPROM) or electric flash type electrically erasable and programmable read-only memory (Flash EEPROM) Out of circuitry, these EEPROMs can be a stand-alone device or an embedded memory, including as part of a large-scale integrated circuit such as a microprocessor or microcontroller.

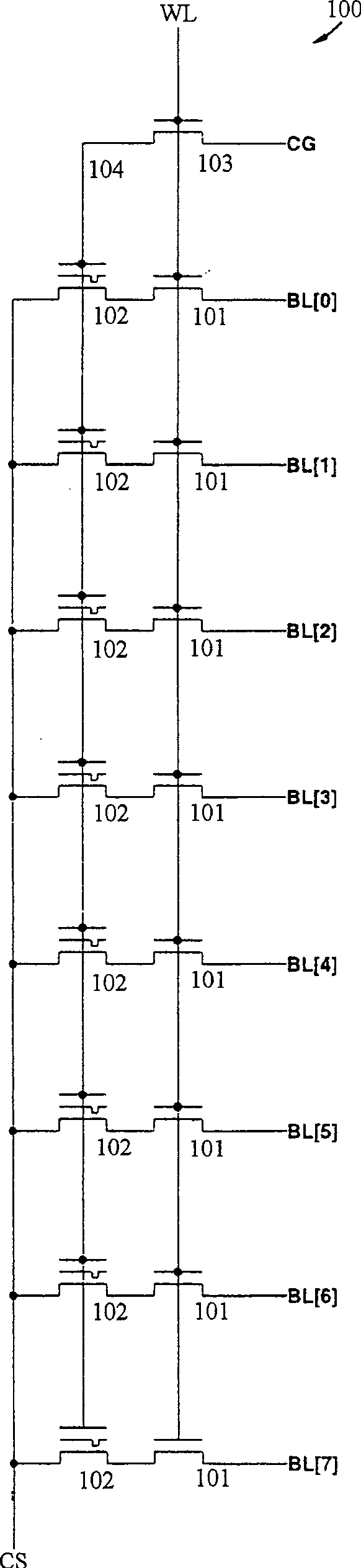

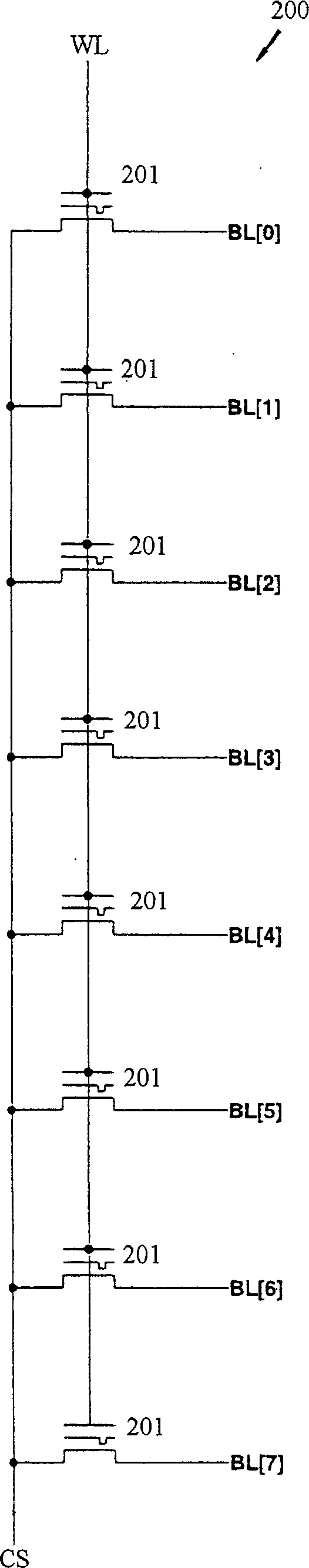

[0068] A semiconductor memory cell array is composed of many identical memory cells organized into rows (word lines) and columns (bit lines). In the fabrication process of semiconductor devices, it is required to uniformly fabricate these memory cells. However, in orde...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com