Emulate testing system and testing method for universal digital circuit

A technology for simulation testing and digital circuits, applied in circuits, semiconductor/solid-state device testing/measurement, electrical digital data processing, etc. It can solve the problems of disconnection from circuits, poor scalability of the test environment, code reuse, etc., to speed up the test progress. , the effect of reducing the risk of testing and reducing the correlation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The scheme of the present invention will be further described below in conjunction with the accompanying drawings.

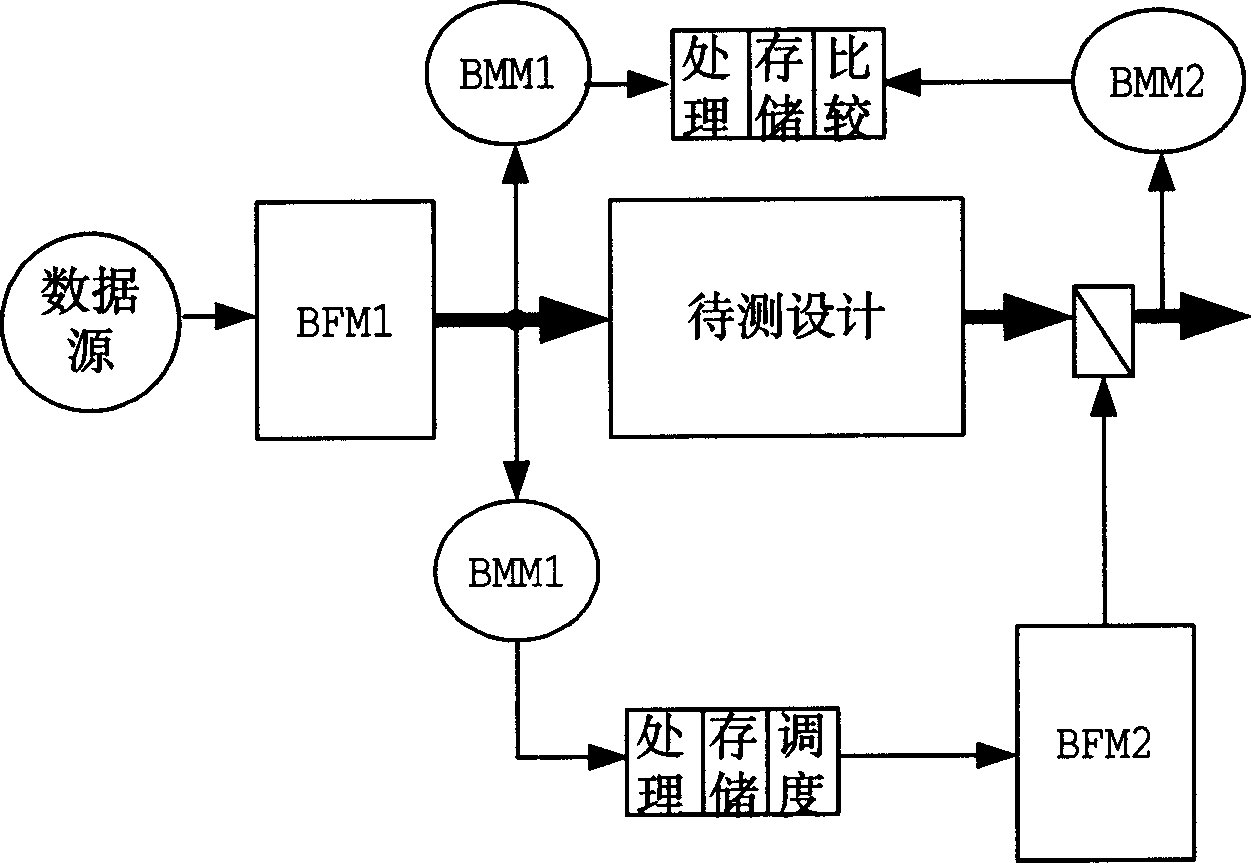

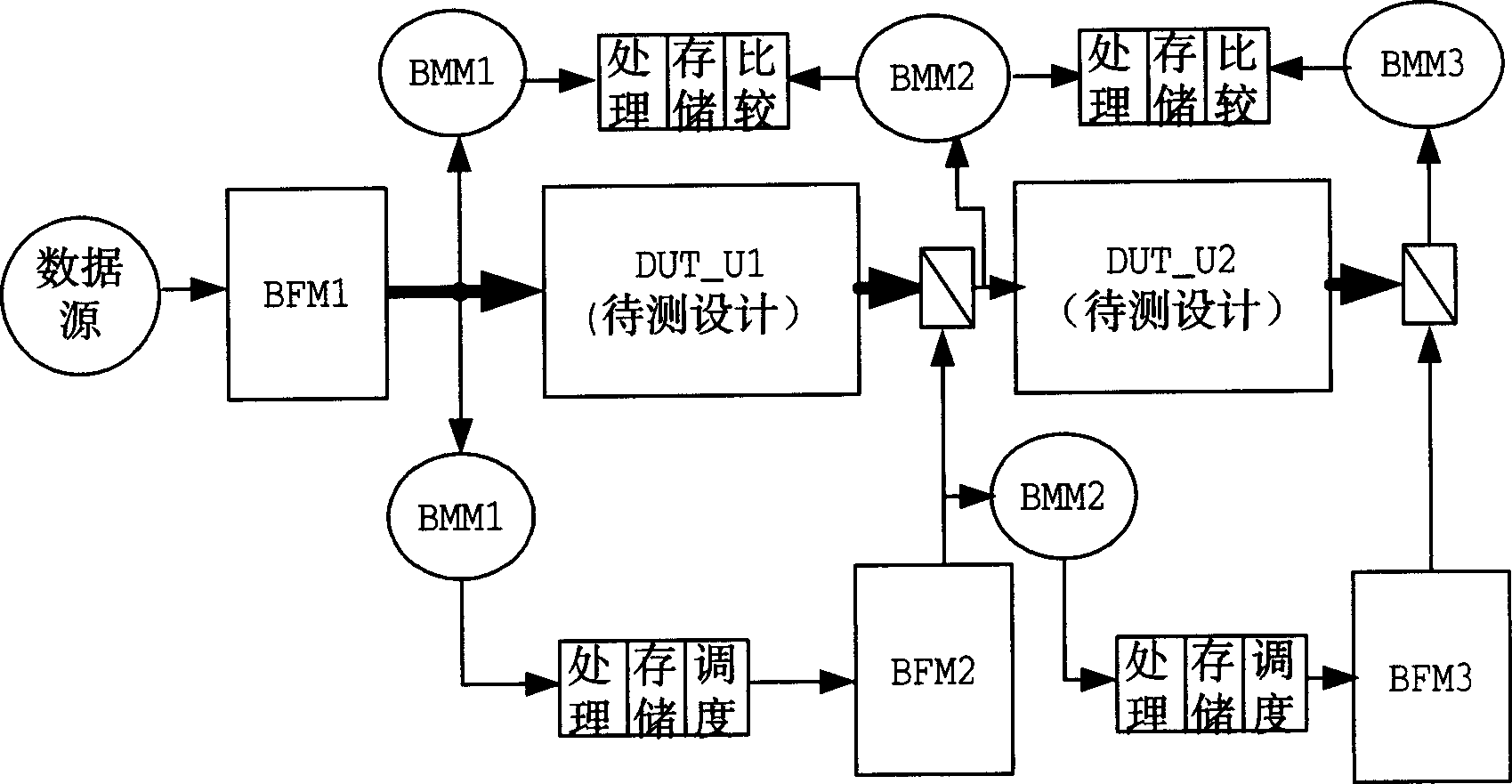

[0032] refer to figure 2 , the general digital circuit emulation test system of the present invention is made up of the data source that is used to generate test excitation data, the bus function module BFM1 that stimulates data to be mapped to time sequence by bus standard and at least one two-way test unit, described two-way test unit It is composed of an up-circuit test line and a down-circuit test line respectively connected to the input and output ends of the design to be tested, wherein

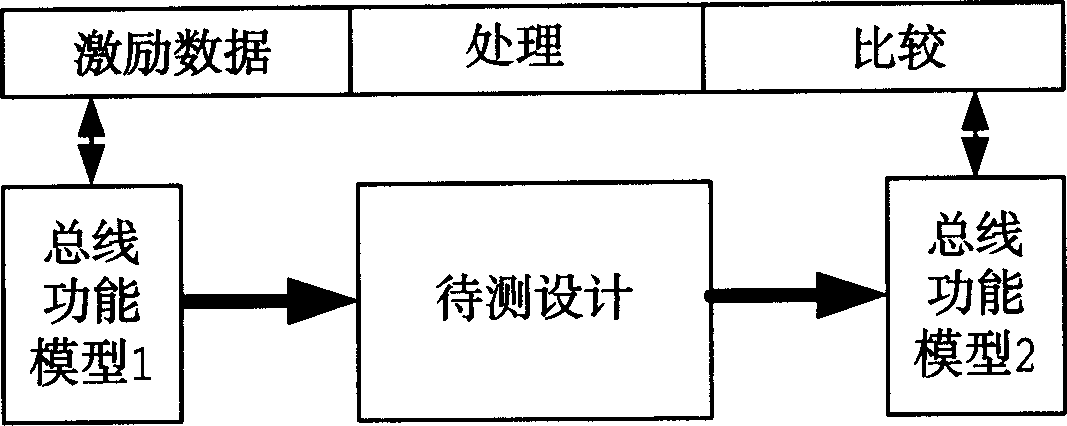

[0033] The composition of the test circuit on the road is: the input bus monitoring module BMM1 that maps the signal timing of the bus into unit data, and the processing unit that performs algorithm simulation on the design under test according to the unit data output by the input bus monitoring module to obtain the expected output data, and The storage unit that...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More