Integrated circuit with nonvoltile data memory circuit

A technology of integrated circuits and latch circuits, applied to logic circuits, digital memory information, circuits, etc. using basic logic circuit components, can solve problems such as easy data inversion, reduce the area of circuit elements, reduce the The effect of simplifying the design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] An embodiment of the present invention will be described below with reference to the drawings. However, the protection scope of the present invention is not limited to the following embodiments, but encompasses the scope defined by the appended claims and their equivalents.

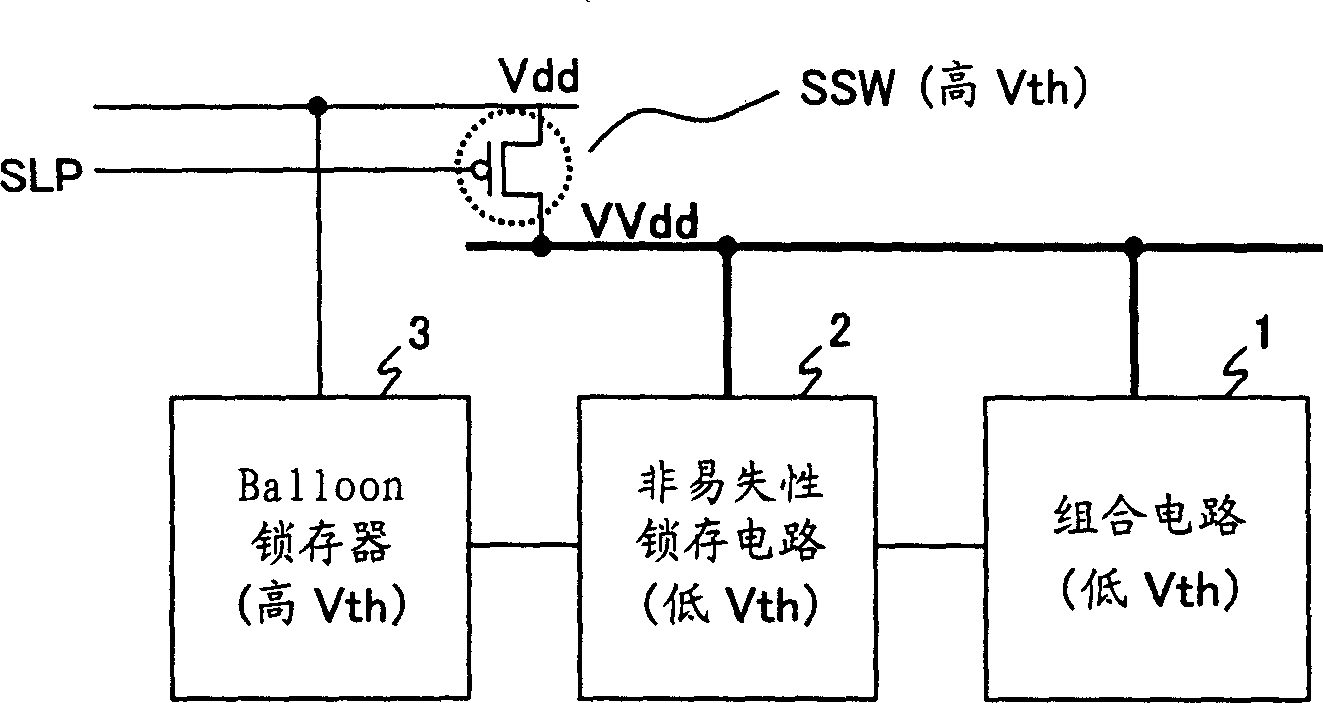

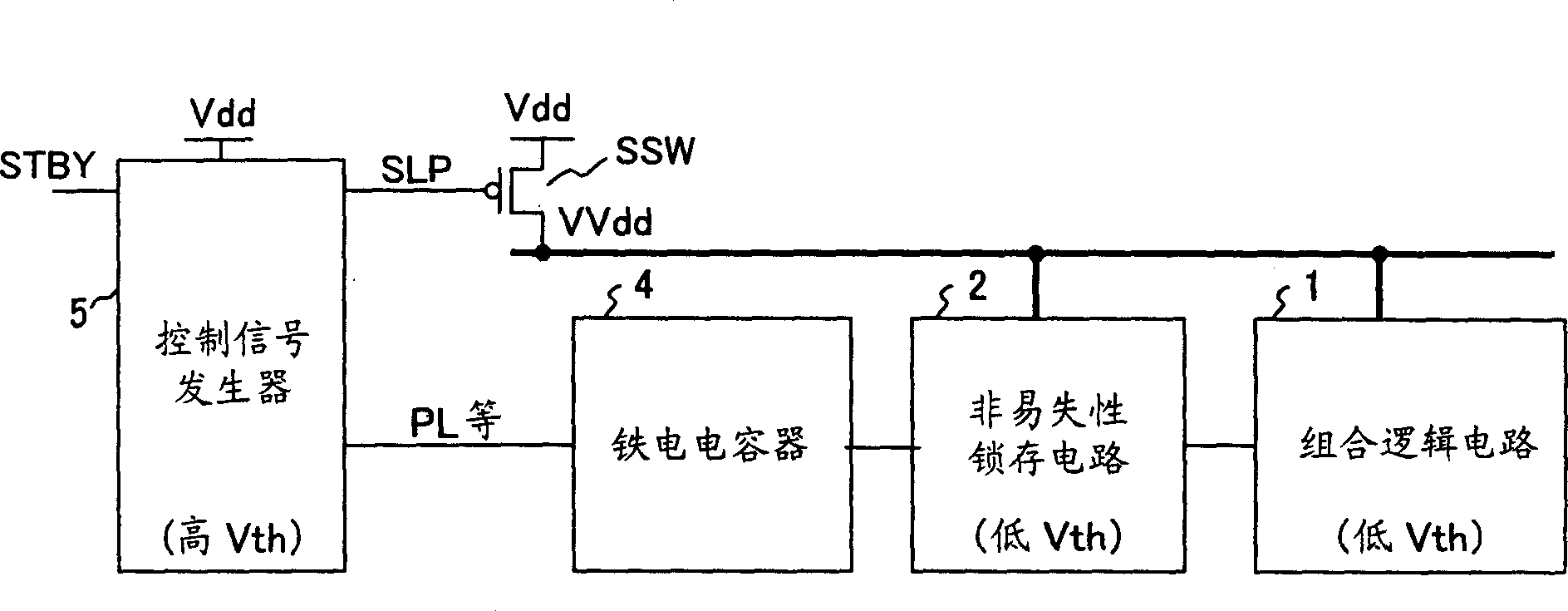

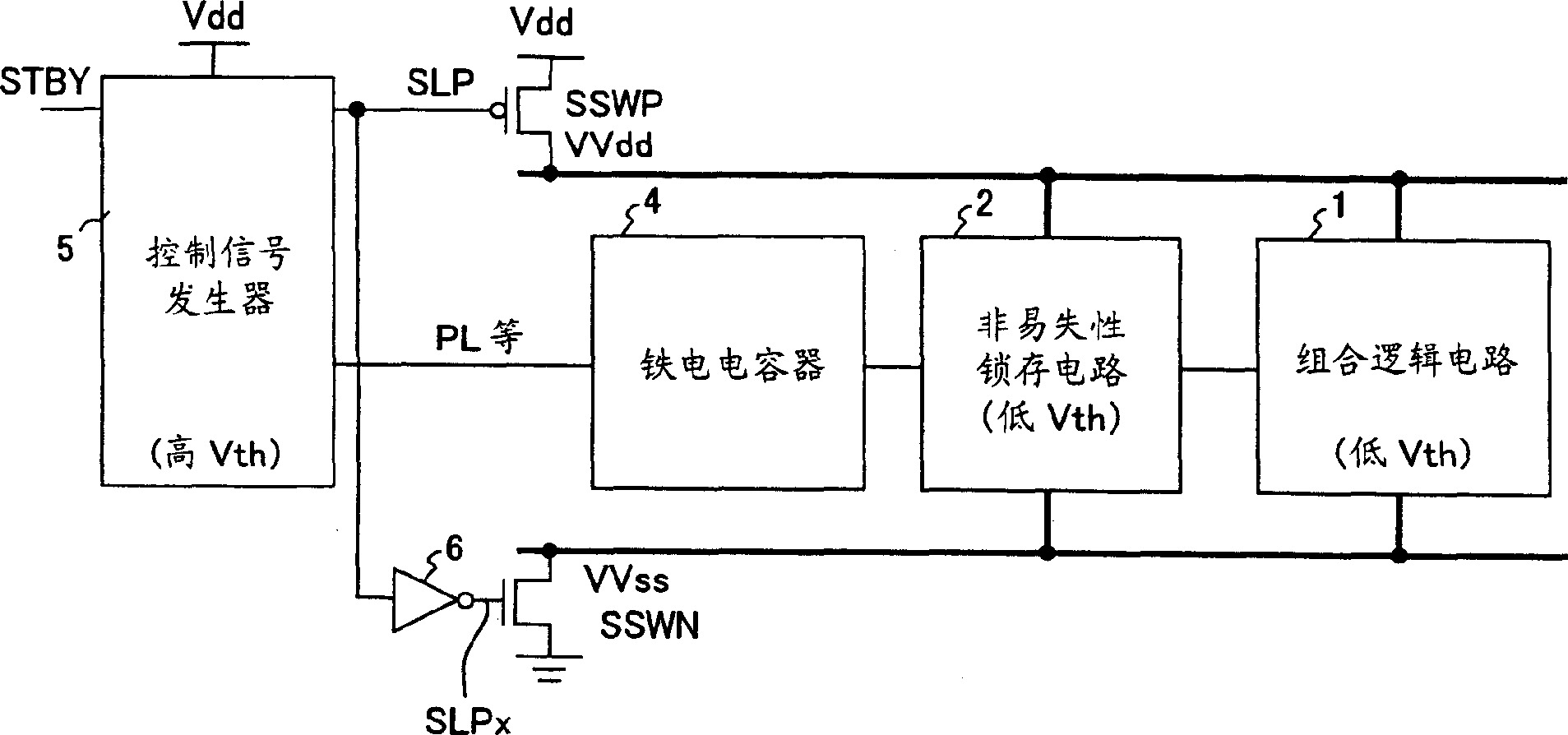

[0044] figure 2 It is the schematic diagram of the structure of the integrated circuit in this embodiment. Similar to the example in Fig. 1, the normal power supply Vdd and the virtual power supply VVdd are connected through a sleep switch SSW, and the combinational logic circuit 1 and the non-volatile latch circuit 2 are connected to the virtual power supply VVdd. The sleep switch SSW is composed of high Vth transistors, whereas the combinational logic circuit 1 and the nonvolatile latch circuit 2 are composed of low Vth transistors.

[0045] The ferroelectric capacitor 4 is provided in the integrated circuit of this embodiment to hold the data held in the nonvolatile latch circuit 2 even when t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More