Method for making optically-controlled transistor and its structure

A manufacturing method, transistor technology, applied in the direction of final product manufacturing, sustainable manufacturing/processing, semiconductor devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

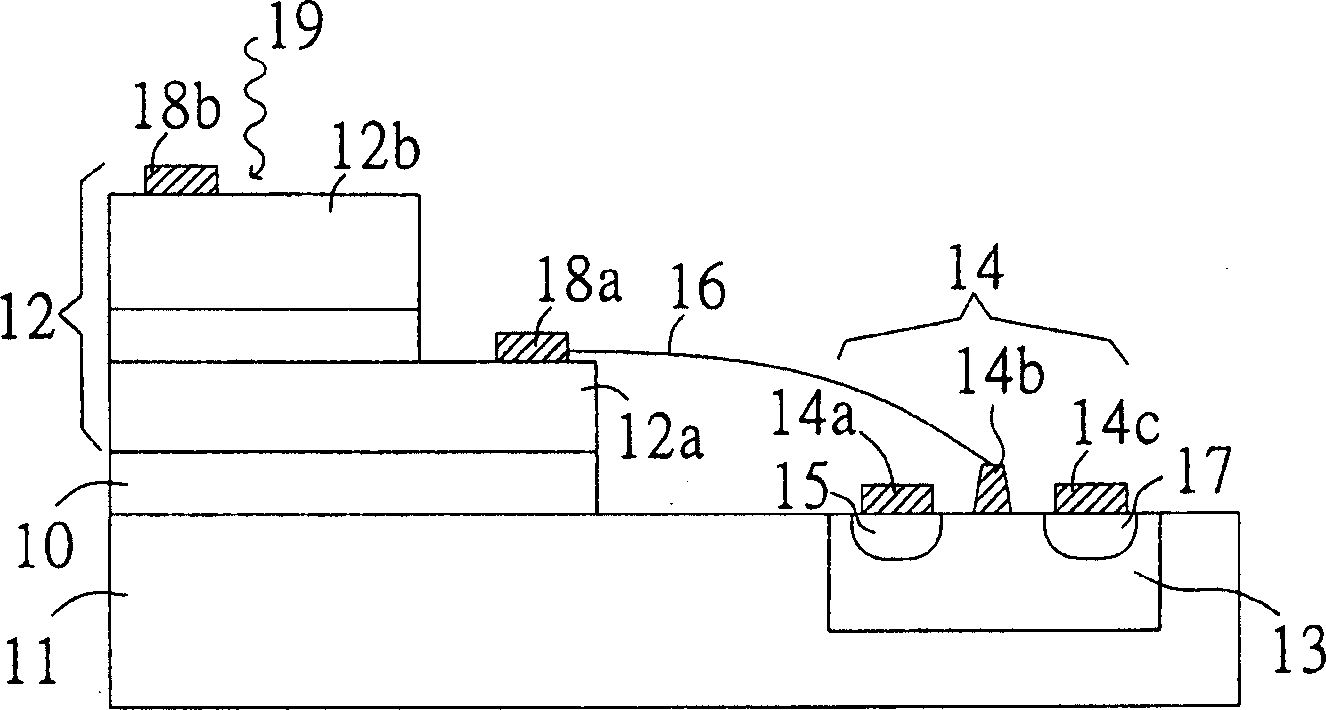

[0038] As mentioned above, in order to form a prism-shaped light-receiving layer between the source and drain of the transistor, the feature of the present invention is to grow a layer of boron phosphide (BP) as a buffer layer on the silicon substrate, and then continue By growing gallium nitride-based materials, it is possible to form a gallium nitride-based layer with a cubic lattice (Cubic Lattice). Since the cubic lattice has and crystal planes, it is easy to form such a layer by epitaxy or etching. The prism-shaped light-receiving layer can therefore improve the light-controlling sensitivity of the transistor of the present invention.

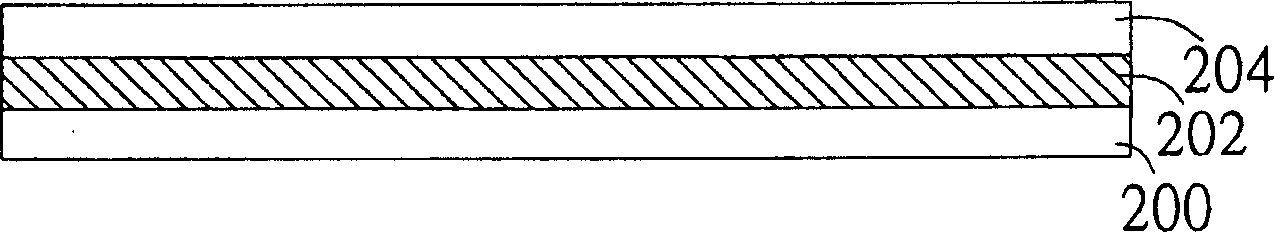

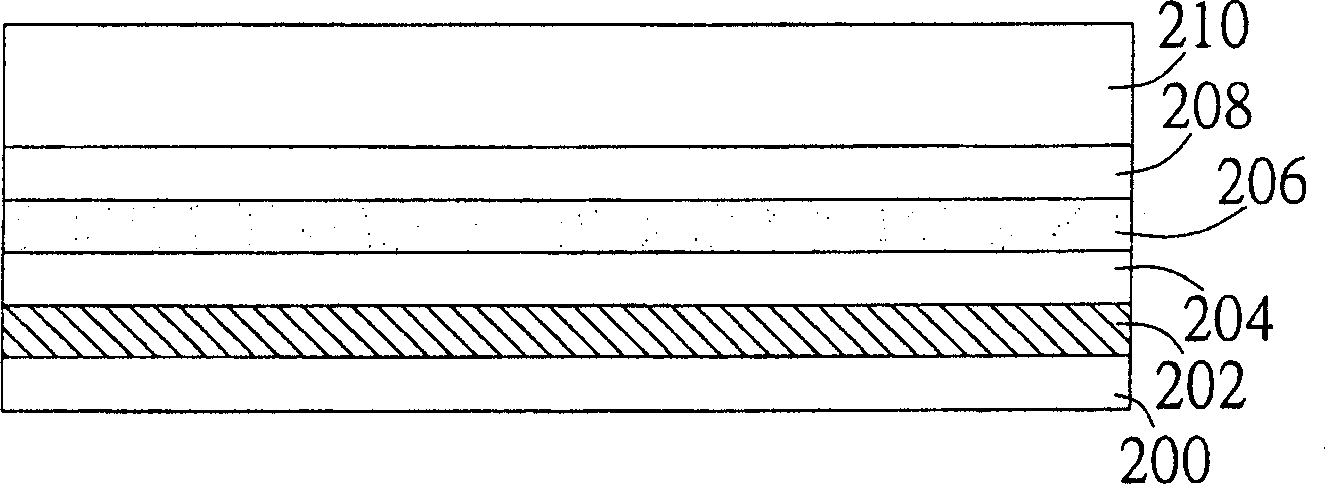

[0039] Please refer to Figure 2A, in order to form gallium nitride-based materials with a cubic lattice, the phototransistor of the present invention forms a buffer layer 202 of boron phosphide material on the surface of the crystal plane of the silicon substrate 200, and then forms a layer aluminum nitride (AlN) layer 204 . Wherein ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| electron mobility | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More