Technical method for integrated circuit design, test and measurement integration

A technology of integrated circuits and technologies, applied in circuits, electrical solid state devices, computing, etc., to achieve the effect of improving design accuracy and use efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The method of the present invention is realized by computer program control, and consists of three parts: the design of the integrated circuit; the verification of the integrated circuit; and the test of the integrated circuit.

[0036] Part I: Integrated Circuit Design.

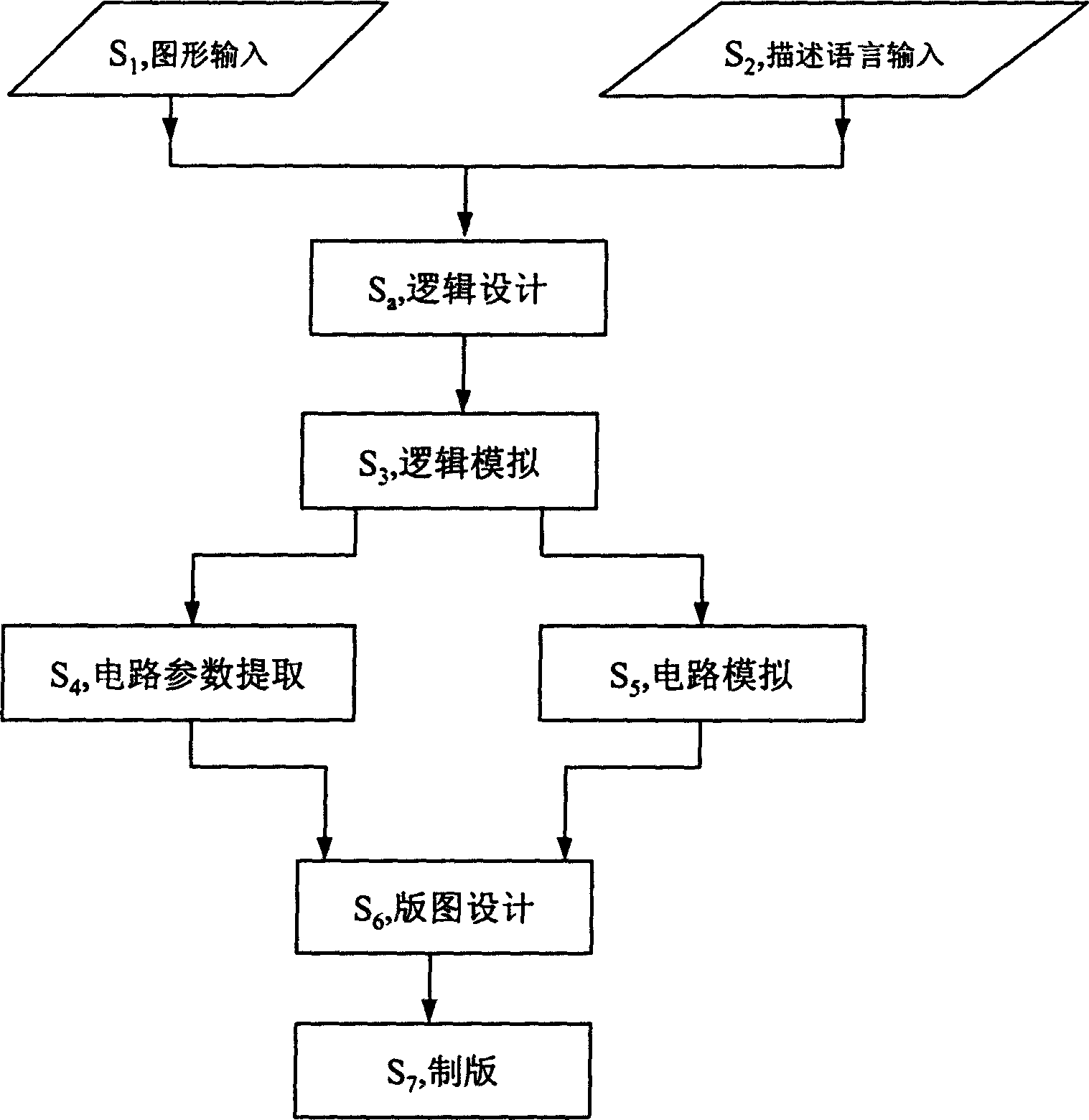

[0037] For ease of presentation, this part of the invention is referred to as an automatic design subsystem, see figure 1 , figure 1 It is a block diagram of the automatic design subsystem in integrated circuit design. The entire automatic design subsystem is divided into: (1) input form of integrated circuit design subsystem; (2) logic design; (3) logic simulation; (4) circuit parameter extraction and circuit simulation; (5) layout design; (6) plate making.

[0038] The workflow of automatic design subsystem is as follows:

[0039] S 1 , the step of graphic input is used to input the design information of the integrated circuit, and the form of graphic input can provide the user with a means of i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More