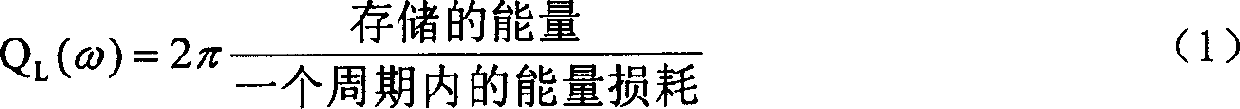

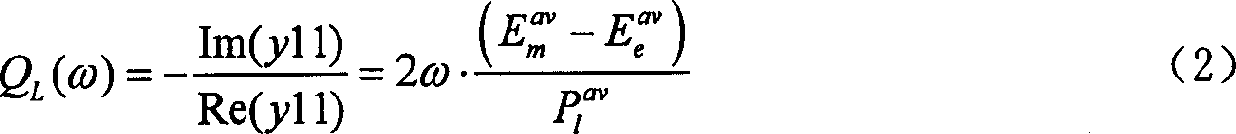

Optimized design method for PN junction underlay isolation on-chip inductance

A design method and PN junction technology, applied in the field of microelectronics, can solve the problems of reducing the isolation of a single-layer PN junction substrate, reducing the effect of inductance parasitic capacitance, increasing inductance loss, etc., so as to reduce the equivalent capacitance of substrate parasitic, reduce Effects of mirror image current loss and eddy current loss reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention is further specifically described below in conjunction with the accompanying drawings.

[0037] Figure 1 shows the standard CMOS hierarchical relationship of four-layer metal interconnection lines; the inductance is formed by winding interconnection lines, and the connections between different layers are connected by through holes. The PN junction is completed by ion implantation of the active layer.

[0038] Fig. 2 is a vertical PN junction series structure of a single well process. 21 is a substrate, and 23 is ion diffusion or implantation opposite to the substrate to form a well, so that a PN junction 27 is formed between 21 and 23 . Ions 25 of opposite polarity are diffused or implanted on 23 , so that a PN junction 28 is formed between 25 and 23 . 22 and 24 in the figure are the depletion layers of the PN junction, and there is no free mobile charge, so the high-resistance depth formed by the PN junction is no longer the depletion layer of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More